摘要: 提出了一種基于ISP技術實現高速數據采集的方法,給出了使用VHDL語言和原理圖完成數據采集模塊中地址發生器和比較電路的部分邏輯設計,只要將所設計的程序下載到可編程器件ispLSI2032中即可實現預期功能。同時,ispLSI2032器件的高密度和可編程性也提高了硬件電路的集成性、可靠性及保密性。

關鍵詞: ISP(在系統可編程);VHDL;高速采集;ispLSI2032

隨著深亞微米及納米半導體制造技術的進步,可編程邏輯器件在電路設計中的應用已十分廣泛。ISP(在系統可編程)器件是先進的可編程器件,

它的優點是不需要編程器即可直接對安裝在用戶目標板上的ISP器件進行編程,而且編程、調試都很方便。當產品升級換代時,只要通過軟件對ISP器件重新編程即可,便可使其具有新的邏輯功能,而不需要增加硬件投入。

目前,ISP芯片內部資源越來越多,速度也越來越快,開發的軟件功能也更加完善。VHDL就是隨著PLD發展起來的一種硬件描述語言,是一種應用于電路設計的高層次描述語言。本文將介紹一種在高速數據采集模塊中部分電路采用ISP技術進行設計的方法。

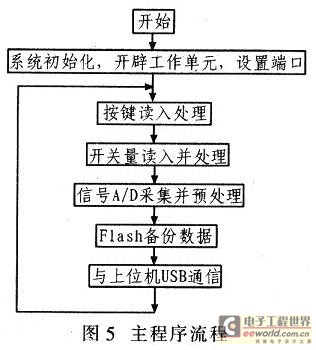

1 高速數據采集模塊的實現

高速數據采集模塊的系統框圖如圖1所示。圖中的ispLSI2032是整個數據采集系統的控制核心?它內部包括了地址信號產生、鎖存、ADC轉換數據的比較、數據存儲器的讀寫控制以及大部分控制邏輯?晶振電路產生的12MHz時鐘可直接在is-pLSI2032內部進行2分頻以得到6MHz的采樣時鐘。高速數據緩存部分由兩片SRAM構成?該SRAM可提供自己的地址線、數據線和控制線。兩個端口可分別與ispLSI2032和單片機的P0口連接。用is-pLSI2032可遞增RAM的地址?同時可提供寫入脈沖以將A/D轉換數據寫入RAM。當A/D轉換的數據超出某一上下限時,系統會將地址數據寫入is-pLSI2032內部的鎖存器中?并在其后打開鎖存,同時將地址送到單片機的P0口,單片機由此地址讀出RAM中相應地址的數據,并通過RS232口傳送到PC機或其它外設。

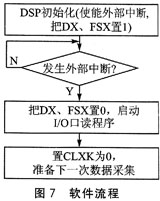

圖2所示是該數據采集系統的基本硬件電路圖。圖中的A/D轉換芯片選用的是美國MAXIM公司的12位A/D轉換器MAX120,它有全控制模式、獨立模式、慢存儲模式、ROM模式和連續轉換模式5種工作模式。在此電路中,MAX120工作于連續轉換模式, 由于MAX120芯片的MODE=DGND,因此,它的INT/BUSY為BUSY輸出。單片機啟動轉換時,INT/BUSY變為低電平,同時將INT0(P3.2)置低,以使計數器的計數狀態與MAX120的INT/BUSY信號一致,也就是說,每轉換完一次,計數器就加以產生新的存儲器地址;轉換結束后,INT/BUSY轉變為高電平,數據在引腳D0~D11處有效,此時WE信號為低,存儲器寫端口打開,并將ADC所轉換的數據寫入與計數器所產生地址對應的存儲單元。繼而INT/BUSY信號再次變低, MAX120進入下一次轉換。直到采集的數據超出某一上下限,ADC模塊中的比較器產生一信號使單片機外部中斷,進而轉入中斷數據處理。其后單片機將讀取存儲在鎖存器中的地址信號,并將其存儲;同時由此地址讀出存儲在存儲器中的超出上下限的數據。單片機定時取數時,先將INT0(P3.2)置高,此時地址產生器的累加由單片機控制(通過T0口,即P3.4)。單片機控制計數器重新計數并產生地址數據,產生的地址送到單片機P0口,并由此地址讀取存儲器中相應地址的數據,最后通過RS232口傳送到PC或其它外設。

圖2

2 ispLSI2032 的結構原理

2.1 ispLSI2032的主要結構

ispLSI2032的結構主要包括全局布線區、萬能邏輯模塊、輸出布線區、輸入總線和巨塊五個部分。其中全局布線區(Global Routing Pool)位于芯片中央,它將所有片內邏輯聯系在一起,其輸入輸出之間的延遲是恒定和可預知的。GRP在延時恒定并且可預知的前提下,提供了完善的片內互連性能。這種獨特的互連性保證了芯片的高性能,從而可容易地實現各種復雜的設計。

萬能邏輯模塊是該器件的基本邏輯單元,它由邏輯陣列、乘積項共享陣列、輸出邏輯宏單元和控制邏輯組成。當乘積項共享陣列將乘積項分配給或門后,可通過一個可編程的與/或/異或陣列輸出來控制該單元中的觸發器,從而使乘積項的共享更加靈活。每個輸出邏輯宏單元有專用的觸發器,每個觸發器與其它可組態電路的連接類似GAL的OLMC,也可以被設置為組合輸出或寄存器輸出。片內靈活的時鐘分配網絡可進一步加強GLB的能力。每一個GLB的時鐘信號既可選用全局同步時鐘,也可選用片內生成的異步乘積項時鐘。

輸出布線區是介于GLB和IOC之間的可編程互連陣列,通過對該區的編程可以將任一個GLB輸出靈活地送到I/O端口的某一個上,以便在不改變外部管腳排列的情況下,修改片內邏輯電路的結構。

輸入輸出單元(Input Output Cell)中的輸入、輸出或雙向信號與具體的I/O引腳相連接,可以構成輸入、輸出、三態輸出的I/O口。

巨塊是GLB及其對應的ORP、IOC的總稱。Is-pLSI2032中有兩個巨塊,通常分布在全局布線區的兩側。每個巨塊均包含GLB、I/O口和專用輸入端,其中專用輸入端不經鎖存器即可直接輸入。它們均可在軟件分配下供本巨塊內的GLB使用。

2.2 ispLSI2032的工作過程

外部信號一般通過I/O單元引導全局布線區,全局布線區主要完成任意I/O端到任意GLB的互連、任意GLB間的互連以及各輸入I/O信號到輸出布線區的連接。器件的所有功能均可由一個GLB或多個GLB級聯完成。在設計中,筆者使用的是ispLEVER軟件,它包含有Lattice編譯器、頂層項目管理器、設計輸入編輯器等?同時還包括Lattice門級功能和實時仿真器,因而能夠對原理圖、VHDL或Abel-HDL語言進行仿真?其設計流程如圖3所示。

3 ispLSI2032在系統中的應用

3.1 硬件選擇

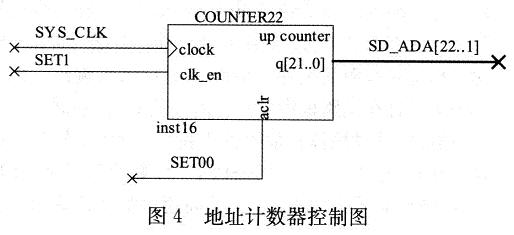

ispLSI器件可分為5大系列,它們的密度、速度以及寄存器數目各不相同。而ispLSI2032速度高達154MHz,是同行業中速度最高的CPLD器件,通過其在系統可編程(ISP)功能可在印刷電路板上對邏輯器件進行編程或改寫。ispLSI2032的內部電路總體框圖如圖4所示。

其中LOGIC9是地址發生電路的邏輯控制部分,COUN11是地址發生電路部分,GLF2是地址鎖存部分。地址發生電路與地址鎖存電路是實現A/D轉換后數據存儲的關鍵部件,它可向存儲器SRAM6264提供寫入操作的順序地址和讀出操作的實時地址,同時可提供地址計數器的清零信號和兩片數據鎖存器的方向控制信號。

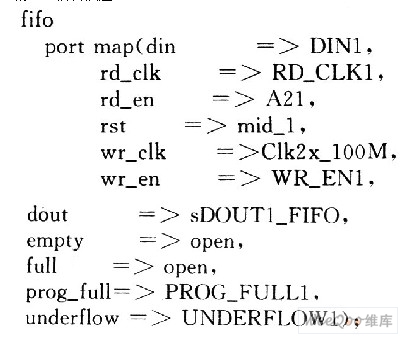

3.1 程序設計

在應用IspLSI2032進行系統設計時,可采用原理圖和VHDL混合輸入的方法。地址產生電路中COUN11可由兩個4位同步二進制計數器級聯構成。地址發生電路的邏輯控制部分LOGIC9、地址鎖存部分的邏輯控制部分和地址鎖存部分GLF2可由VHDL語言來進行設計,下面給出GLF2的程序設計代碼:

library ieee;

use ieee.std_logic_1164.all;

entity glf2 is

port(a0,a1,a2,a3,a4,a5,a6,a7: in std_logic;

b0,b1,b2,b3,b4,b5,b6,b7: in std_logic;

oc1,c,oc2: in std_logic;

Q0,Q1,Q2,Q3,Q4,Q5,Q6,Q7:out std_logic);

end glf2;

architecture exam of glf2 is

begin

process(oc1,c,oc2)

begin

if(oc1=‘0' and c=‘1' and oc2=‘1') then

Q0<=a0;Q1<=a1;Q2<=a2;Q3<=a3;Q4<=a4;Q5<=a5;Q6<=a6;Q7<=a7;

elsif(oc1=‘1' and c=‘1' and oc2=‘0') then

Q0<=b0;Q1<=b1;Q2<=b2;Q3<=b3;Q4<=b4;Q5<=b5;Q6<=b6;Q7<=b7;

end if;

end process;

end exam;

圖4

4 編程設計

將設計階段生成的熔絲圖JEDEC文件裝入到器件中去的過程稱為編程(也稱為下載、配置)。對在系統可編程邏輯器件,可使用ISP菊花鏈下載編程軟件(ispVM)來進行編程,筆者采用Lattice公司最新推出的一套EDA軟件—ispLEVER,同時采用原理圖、硬件描述語言、混合輸入三種方式來對所設計的數字電子系統進行功能仿真和時序仿真?然后通過計算機的并口和專用下載電纜直接對器件進行編程,最后對編程結果進行檢查并最終通過。

電子發燒友App

電子發燒友App

評論