快速傅里葉變換(FFT)在雷達(dá)、通信和電子對(duì)抗等領(lǐng)域有廣泛應(yīng)用。近年來(lái)現(xiàn)場(chǎng)可編程門(mén)陣列(FPGA)的飛速發(fā)展,與DSP技術(shù)相比,由于其并行信號(hào)處理結(jié)構(gòu),使得FPGA能夠很好地適用于高速信號(hào)處理系統(tǒng)。由于Altera等公司研制的FFTIP核,價(jià)錢(qián)昂貴,不適合大規(guī)模應(yīng)用,

2011-01-21 14:46:53 4750

4750

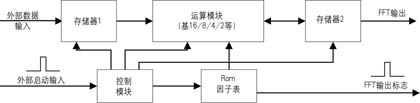

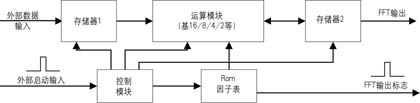

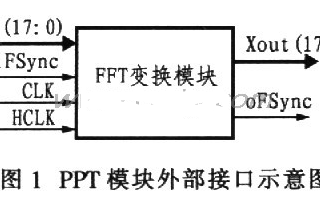

FPGA實(shí)現(xiàn)的 FFT 處理器的硬件結(jié)構(gòu)。接收單元采用乒乓RAM 結(jié)構(gòu), 擴(kuò)大了數(shù)據(jù)吞吐量。中間數(shù)據(jù)緩存單元采用雙口RAM , 減少了訪問(wèn)RAM 的時(shí)鐘消耗。計(jì)算單元采用基 2 算法, 流水線結(jié)構(gòu), 可在

2017-11-21 15:55:13

如何根據(jù)成本、功耗和性能來(lái)選擇微處理器?FPGA結(jié)構(gòu)中硬核和軟核的特點(diǎn)是什么?處理器IP有什么重要性?

2021-04-08 06:16:37

可編程邏輯(FPGA)與硬核處理器(HPS)之間互聯(lián)的結(jié)構(gòu)

2021-04-02 06:03:40

傳統(tǒng)的、基于通用DSP處理器并運(yùn)行由C語(yǔ)言開(kāi)發(fā)的算法的高性能DSP平臺(tái),正在朝著使用FPGA預(yù)處理器和/或協(xié)處理器的方向發(fā)展。這一最新發(fā)展能夠?yàn)楫a(chǎn)品提供巨大的性能、功耗和成本優(yōu)勢(shì)。

2011-09-29 16:28:38

音頻處理器的功能和FPGA器件的靈活性,能夠支持許多創(chuàng)新應(yīng)用。 廣泛的工業(yè)市場(chǎng)呢? 通常,廣泛的工業(yè)市場(chǎng)的需求并非像存儲(chǔ)、服務(wù)器或通信應(yīng)用所要求的那么性能導(dǎo)向或復(fù)雜。對(duì)于所有圍繞工業(yè)物聯(lián)網(wǎng)

2016-12-07 16:05:03

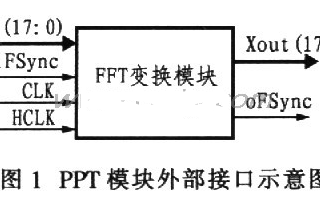

FPGA實(shí)現(xiàn)高速FFT處理器的設(shè)計(jì)介紹了采用Xilinx公司的Virtex - II系列FPGA設(shè)計(jì)高速FFT處理器的實(shí)現(xiàn)方法及技巧。充分利用Virtex - II芯片的硬件資源,減少?gòu)?fù)雜邏輯,采用

2012-08-12 11:49:01

本帖最后由 mr.pengyongche 于 2013-4-30 03:00 編輯

我想知道fft在dsp處理器上的實(shí)現(xiàn),,,他的表現(xiàn)是什么,,程序如何,,,波形是怎樣的,求這一題目的論文,,,感謝各位大神

2013-01-16 01:35:52

RISC的優(yōu)點(diǎn)Patterrson和Ditzel認(rèn)為處理器的設(shè)計(jì)有3個(gè)基本優(yōu)點(diǎn):基于RISC體系結(jié)構(gòu)設(shè)計(jì)的處理器管芯面積小。處理器的簡(jiǎn)單使得需要的晶體管減少和實(shí)現(xiàn)的硅片面積減小,剩下更大面積可集成

2022-04-24 10:02:29

SoCFPGA器件在一個(gè)器件中同時(shí)集成了處理器和FPGA體系結(jié)構(gòu)。將兩種技術(shù)合并起來(lái)具有很多優(yōu)點(diǎn),包括更高的集成度、更低的功耗、更小的電路板面積,以及處理器和FPGA之間帶寬更大的通信等等。這一同類(lèi)最佳的器件發(fā)揮了處理器與FPGA系統(tǒng)融合的優(yōu)勢(shì),同時(shí)還保留了獨(dú)立處理器和FPGA方法的優(yōu)點(diǎn)。

2019-09-26 07:59:27

生成針對(duì)Cortex-M處理器優(yōu)化的代碼。嵌入式編碼?Support Package的ARM?的Cortex?-M處理器可以生成使用CMSIS庫(kù)數(shù)學(xué)運(yùn)算的優(yōu)化代碼。將此生成的代碼用于ARM

2021-12-14 09:10:35

數(shù)據(jù)均衡決策的過(guò)程。該設(shè)計(jì)使用了在一個(gè)平臺(tái)FPGA中實(shí)現(xiàn)的一個(gè)嵌入式PowerPC。協(xié)處理器的意義協(xié)處理器是一個(gè)處理單元,該處理單元與一個(gè)主處理單元一起使用來(lái)承擔(dān)通常由主處理單元執(zhí)行的運(yùn)算。通常,協(xié)

2015-02-02 14:18:19

7.5 陣列結(jié)構(gòu)的FFT處理器7.6 流水結(jié)構(gòu)的FFT處理器7.6.1 基于SDF流水結(jié)構(gòu)的FFT處理器7.6.2 基于MDC流水結(jié)構(gòu)的FFT處理器7.7 IFFT與FFT的關(guān)系參考文獻(xiàn)第8章 一些細(xì)節(jié)

2012-04-24 09:33:23

中,數(shù)字信號(hào)處理系統(tǒng)經(jīng)常要進(jìn)行高速、高精度的FFF運(yùn)算。現(xiàn)場(chǎng)可編程邏輯陣列(FPGA)是一種可定制集成電路,具有面向數(shù)字信號(hào)處理算法的物理結(jié)構(gòu)。用FPGA實(shí)現(xiàn)FFT處理器具有硬件系統(tǒng)簡(jiǎn)單、功耗低的優(yōu)點(diǎn)

2019-07-03 07:56:53

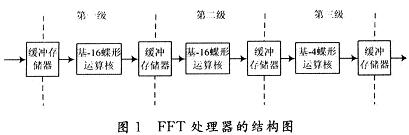

一種高速并行FFT處理器的VLSI結(jié)構(gòu)設(shè)計(jì)摘要:在OFDM系統(tǒng)的實(shí)現(xiàn)中,高速FFT處理器是關(guān)鍵。在分析了基4按時(shí)域抽取快速傅立葉變換(FFT)算法特別的基礎(chǔ)上,研究了一種高性能的FFT處理器的硬件

2008-10-15 22:41:48

代碼加速和代碼轉(zhuǎn)換到硬件協(xié)處理器的方法如何采用FPGA協(xié)處理器實(shí)現(xiàn)算法加速?

2021-04-13 06:39:25

舉例說(shuō)明FPGA作為協(xié)處理器在實(shí)時(shí)系統(tǒng)中有哪些應(yīng)用?FPGA用于協(xié)處理器有什么結(jié)構(gòu)特點(diǎn)和設(shè)計(jì)原則?

2021-04-08 06:48:20

的DSP是什么東西?打開(kāi)QuartusII的IP核向?qū)В缟蠄D所示。QuartusII中的DSP是一些IP核,它只做一些常見(jiàn)的算法,如:FFT、NCO、FIR等。顯然,這并非前面所說(shuō)的DSP處理器。查看

2020-09-04 10:31:13

我目前使用的是32位FFT LIB函數(shù),它在DSP庫(kù)(XC32和C32)中可用。這個(gè)庫(kù)還會(huì)與PIC32 MZ處理器一起工作嗎?據(jù)我所知,MZ系列包含一個(gè)加速fft轉(zhuǎn)換的指令,但是當(dāng)我查看

2019-08-08 10:49:05

最近,因?yàn)轫?xiàng)目需要在STM32F103系列處理器上,對(duì)采集的音頻信號(hào)進(jìn)行FFT運(yùn)算,然而STM32F103畢竟不是STM32F4系列的處理器,對(duì)于一般的FFT運(yùn)算程序還是比較緩慢的。幸虧官方提供了

2021-08-05 07:26:34

在arm處理器上多線程如何優(yōu)化加速呢?有哪些方法

2022-08-04 14:20:06

``基于FPGA的圖像FFT濾波處理 AT7_Xilinx開(kāi)發(fā)板(USB3.0+LVDS)資料共享 騰訊鏈接:https://share.weiyun.com/5GQyKKc 百度網(wǎng)盤(pán)鏈接

2019-08-08 11:33:01

基于FPGA的移位寄存器流水線結(jié)構(gòu)FFT處理器

2012-08-18 00:04:21

是處理數(shù)字信號(hào)如圖形、語(yǔ)音及圖像等領(lǐng)域的重要變換工具。快速傅里葉變換(FFT)是DFT的快速算法。FFT算法的硬件實(shí)現(xiàn)一般有3種形式:1)使用通用DSP來(lái)實(shí)現(xiàn);2)用專(zhuān)用DSP來(lái)實(shí)現(xiàn);3)通過(guò)FPGA來(lái)

2009-06-14 00:19:55

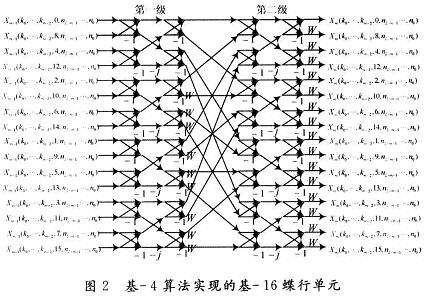

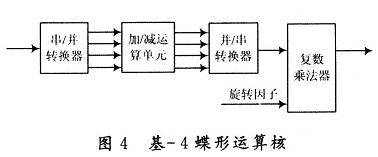

FFT算法在數(shù)字信號(hào)處理中占有重要的地位,所以本文提出了用FPGA實(shí)現(xiàn)FFT的一種設(shè)計(jì)思想,給出了總體實(shí)現(xiàn)框圖:重點(diǎn)設(shè)計(jì)實(shí)現(xiàn)了FFT算法中的蝶形處理單元,采用了一種高效乘法器算法設(shè)計(jì)實(shí)現(xiàn)了蝶形處理單元中的旋轉(zhuǎn)因子乘法器,從而提高了蝶形處理器的運(yùn)算速度,降低了運(yùn)算復(fù)雜度。

2017-11-28 11:32:15

的各個(gè)領(lǐng)域。采用INMOS公司的IMS A100級(jí)聯(lián)型信號(hào)處理器為模板,以FIR濾波器設(shè)計(jì)為核心,用FPGA技術(shù)開(kāi)發(fā)設(shè)計(jì)級(jí)聯(lián)型信號(hào)處理器,能夠應(yīng)用于數(shù)字FIR濾波、高速自適應(yīng)濾波、相關(guān)和卷積、離散

2019-07-30 07:22:48

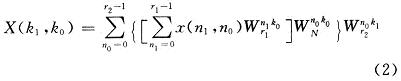

FFT算法的實(shí)現(xiàn)為了提高FFT工作頻率和節(jié)省FPGA資源,采用3級(jí)流水線結(jié)構(gòu)實(shí)現(xiàn)64點(diǎn)的FFT運(yùn)算。流水線處理器的結(jié)構(gòu)如圖2所示。每級(jí)均由延時(shí)單元、轉(zhuǎn)接器(SW)、蝶形運(yùn)算和旋轉(zhuǎn)因子乘法4個(gè)模塊組成

2019-06-17 09:01:35

某人工神經(jīng)網(wǎng)絡(luò)的FPGA處理器能夠?qū)?shù)據(jù)進(jìn)行運(yùn)算處理,為了實(shí)現(xiàn)集數(shù)據(jù)通信、操作控制和數(shù)據(jù)處理于一體的便攜式神經(jīng)網(wǎng)絡(luò)處理器,需要設(shè)計(jì)一種基于嵌入式ARM內(nèi)核及現(xiàn)場(chǎng)可編程門(mén)陣列FPGA的主從結(jié)構(gòu)處理系統(tǒng)滿足要求。

2021-05-21 06:35:27

本文設(shè)計(jì)的FFT處理器,基于FPGA技術(shù),由于采用移位寄存器流水線結(jié)構(gòu),實(shí)現(xiàn)了兩路數(shù)據(jù)的同時(shí)輸入,相比傳統(tǒng)的級(jí)聯(lián)結(jié)構(gòu),提高了蝶形運(yùn)算單元的運(yùn)算效率,減小了輸出延時(shí),降低了芯片資源的使用。

2021-04-28 06:32:30

多核處理器環(huán)境下的編程挑戰(zhàn)是什么如何通過(guò)LabVIEW圖形化開(kāi)發(fā)平臺(tái)有效優(yōu)化多核處理器環(huán)境下的信號(hào)處理性能

2021-04-26 06:40:29

本文講述汽車(chē)娛樂(lè)系統(tǒng)的需求,討論主流系統(tǒng)構(gòu)架,以及FPGA協(xié)處理器是如何集成到軟硬件體系中,以滿足高性能處理、靈活性和降低成本的要求。

2021-04-30 07:21:43

本文介紹了一種采用級(jí)聯(lián)結(jié)構(gòu)在FPGA上實(shí)現(xiàn)IIR數(shù)字濾波器的方法。

2021-04-15 06:16:32

嵌入式多核處理器結(jié)構(gòu)OpenMP并行化優(yōu)化

2021-03-02 06:59:00

目錄一、嵌入式微處理器體系結(jié)構(gòu)1、馮諾依曼體系結(jié)構(gòu)2、哈弗體系結(jié)構(gòu)二、嵌入式系統(tǒng)的硬件結(jié)構(gòu)1、嵌入式微控制器MCU(CPU+片內(nèi)內(nèi)存+片內(nèi)外設(shè))2、嵌入式微處理器MPU(CPU)3、嵌入式數(shù)字信號(hào)

2021-11-08 06:57:02

微處理器的結(jié)構(gòu)是由哪些部分組成的?微處理器的代碼是如何執(zhí)行的呢?

2022-02-28 09:25:10

結(jié)構(gòu)1微處理器的外部結(jié)構(gòu)總線的功能微處理器的內(nèi)部結(jié)構(gòu)典型的CPU內(nèi)部結(jié)構(gòu)圖堆棧指針SP微處理器的外部結(jié)構(gòu)8086CPU有40個(gè)管腳,稱(chēng)為微處理器的總線總線的功能微處理器的內(nèi)部結(jié)構(gòu)典型的CPU內(nèi)部結(jié)構(gòu)

2022-02-14 07:40:41

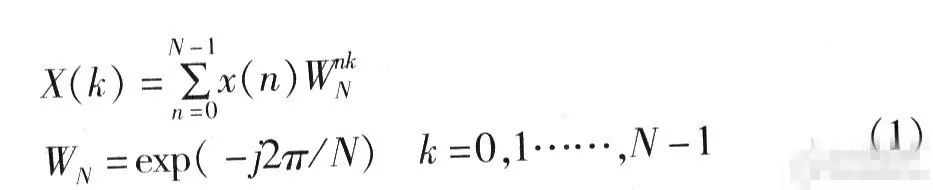

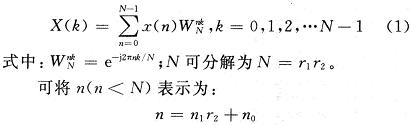

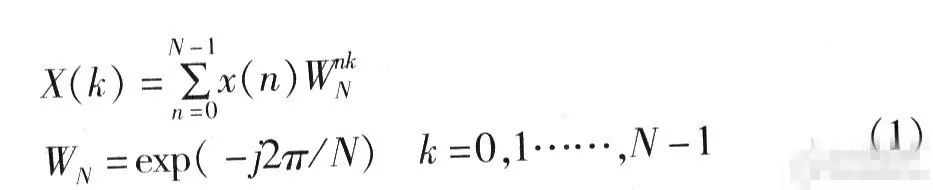

數(shù)字信號(hào)處理主要研究采用數(shù)字序列或符號(hào)序列表示信號(hào),并用數(shù)字計(jì)算方法對(duì)這些序列進(jìn)行處理,以便把信號(hào)變換成符合某種需要的形式。在現(xiàn)代數(shù)字信號(hào)處理中,最常用的變換方法就是離散傅里葉變換(DFT),然而

2019-08-14 08:26:23

快速傅里葉變換(FFT)在雷達(dá)、通信和電子對(duì)抗等領(lǐng)域有廣泛應(yīng)用。近年來(lái)現(xiàn)場(chǎng)可編程門(mén)陣列(FPGA)的飛速發(fā)展,與DSP技術(shù)相比,由于其并行信號(hào)處理結(jié)構(gòu),使得FPGA能夠很好地適用于高速信號(hào)處理

2019-08-28 06:10:15

處理器間通信和中斷方面仍需進(jìn)一步的研究。本文在處理器間通信和中斷控制方面進(jìn)行了深入的研究。MicroBlaze是一個(gè)被優(yōu)化過(guò)的可以在Xilinx公司FPGA中運(yùn)行的軟核處理器,可以和其他外設(shè)IP核一起完成

2021-03-16 07:44:35

討論了一種基于FPGA的64點(diǎn)FFT處理器的設(shè)計(jì)方案,輸入數(shù)據(jù)的實(shí)部和虛部均以16位二進(jìn)制數(shù)表示,采用基2DIT-FFT算法,以Altera公司的QuartusⅡ軟件為開(kāi)發(fā)平臺(tái)對(duì)處理器各個(gè)的模塊進(jìn)行設(shè)計(jì),在Stratix系列中的EP1S25型FPGA通過(guò)了綜合和仿真,運(yùn)算結(jié)果正確。

2021-04-29 06:25:54

本文根據(jù)FPGA的結(jié)構(gòu)特點(diǎn),圍繞在FPGA上設(shè)計(jì)實(shí)現(xiàn)八位微處理器軟核設(shè)計(jì)方法進(jìn)行探討,研究了片上系統(tǒng)的設(shè)計(jì)方法和設(shè)計(jì)復(fù)用技術(shù),并給出了指令集和其調(diào)試方法,提出了一種基于FPGA的微處理器的IP的設(shè)計(jì)方法。

2021-04-29 06:38:37

求大神分享一種基于FPGA的級(jí)聯(lián)結(jié)構(gòu)FFT處理器的優(yōu)化設(shè)計(jì)

2021-05-06 07:34:53

請(qǐng)問(wèn)FPGA協(xié)處理器有哪些優(yōu)勢(shì)?

2021-05-08 08:29:13

怎樣設(shè)計(jì)FIR濾波器結(jié)構(gòu)?怎樣設(shè)計(jì)級(jí)聯(lián)型信號(hào)處理器?如何對(duì)級(jí)聯(lián)型信號(hào)處理器進(jìn)行仿真測(cè)試?

2021-04-28 07:04:01

怎樣去設(shè)計(jì)可擴(kuò)展FFT處理器?可擴(kuò)展FFT處理器的結(jié)構(gòu)是如何構(gòu)成的?

2021-05-06 07:52:19

微處理器體系結(jié)構(gòu)由哪幾部分組成?超標(biāo)量處理器的微體系結(jié)構(gòu)由哪幾部分組成?

2022-02-28 07:31:47

嗨,大家好 我是sandeep,是FPGA的新手。我目前正在開(kāi)發(fā)一個(gè)項(xiàng)目,開(kāi)發(fā)一個(gè)模塊,負(fù)責(zé)處理從PLC接收的數(shù)據(jù)的加密和解密任務(wù)。我需要為沒(méi)有處理器的項(xiàng)目選擇FPGA。那么請(qǐng)你幫我選擇FPGA

2019-05-16 10:20:42

,最高可提供256 GMAC的DSP性能。將需要高速并行處理的工作卸載給FPGA,而將需要高速串行處理的工作留給處理器,這樣即可在降低系統(tǒng)要求的同時(shí)優(yōu)化整體系統(tǒng)的性價(jià)比。

2019-07-15 06:18:56

的媒體處理器MD-32特有的體系結(jié)構(gòu)特點(diǎn),提出C編譯器支持的,在匯編代碼級(jí)通過(guò)指令調(diào)度和轉(zhuǎn)換指令操作數(shù)及其類(lèi)型的代碼優(yōu)化方法,實(shí)現(xiàn)輸出高效的并行指令。統(tǒng)計(jì)數(shù)據(jù)表明:代碼執(zhí)行效率平均可以提高l5%,而代碼密度平均提高12%。

2011-03-03 10:46:37

針對(duì)在工業(yè)中越來(lái)越多的使用到的FFT,本文設(shè)計(jì)出了一種利用CORDIC 算法在FPGA 上實(shí)現(xiàn)快速FFT 的方法。CORDIC 實(shí)現(xiàn)復(fù)數(shù)乘法比普通的計(jì)算器有結(jié)構(gòu)上的優(yōu)勢(shì),并且采用了循環(huán)結(jié)構(gòu)

2009-08-24 09:31:10 9

9 Blackfin處理器性能優(yōu)化:Blackfin處理器性能優(yōu)化課程單元:Blackfin®處理器性能優(yōu)化主講人:Rick Gentile第一章:導(dǎo)言第1a節(jié):概述第1b節(jié):背景信息第2章:應(yīng)用框架

2009-09-02 13:05:38 18

18 本文討論了一種可在FPGA 上實(shí)現(xiàn)的FFT 結(jié)構(gòu)。該結(jié)構(gòu)采用基于流水線結(jié)構(gòu)和快速并行乘法器的蝶形處理器。乘法器采用改進(jìn)的Booth 算法,簡(jiǎn)化了部分積符號(hào)擴(kuò)展,使用Wallace 樹(shù)結(jié)構(gòu)和4-2

2009-09-11 15:46:40 16

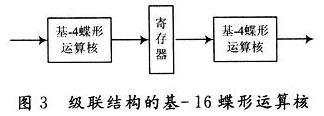

16 本文主要研究基于FPGA 的數(shù)據(jù)處理系統(tǒng),內(nèi)部包含一個(gè)1024 點(diǎn)的FFT 處理單元。FFT 部分采用基四算法,五級(jí)級(jí)聯(lián)處理,并通過(guò)CORDIC 流水線結(jié)構(gòu)使硬件實(shí)現(xiàn)較慢的復(fù)乘運(yùn)算轉(zhuǎn)化為移位

2009-12-19 16:18:35 59

59 本文利用頻域抽取基四算法,運(yùn)用靈活的硬件描述語(yǔ)言-Verilog HDL 作為設(shè)計(jì)主體,設(shè)計(jì)并實(shí)現(xiàn)一套集成于FPGA 內(nèi)部的FFT 處理器。FFT 處理器的硬件試驗(yàn)結(jié)果表明該處理器的運(yùn)算結(jié)

2010-01-20 14:33:54 40

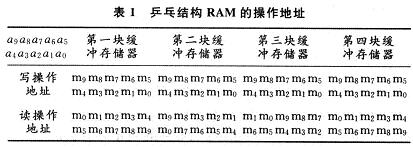

40 在OFDM系統(tǒng)的實(shí)現(xiàn)中,高速FFT處理器是關(guān)鍵。在分析了基4按時(shí)域抽取快速傅立葉變換(FFT)算法特點(diǎn)的基礎(chǔ)上,研究了一種高性能FFT處理器的硬件結(jié)構(gòu)。此結(jié)構(gòu)能同時(shí)從四個(gè)并行存

2010-07-02 16:51:15 11

11 針對(duì)在工業(yè)中越來(lái)越多的使用到的FFT,本文設(shè)計(jì)出了一種利用CORDIC算法在FPGA上實(shí)現(xiàn)快速FFT的方法。CORDIC實(shí)現(xiàn)復(fù)數(shù)乘法比普通的計(jì)算器有結(jié)構(gòu)上的優(yōu)勢(shì),并且采用了循環(huán)結(jié)構(gòu)的CORDIC算

2010-08-09 15:39:20 55

55 Actel公司推出專(zhuān)為Actel FPGA應(yīng)用而優(yōu)化的軟ARM7系列處理器CoreMP7,將可編程邏輯的設(shè)計(jì)靈活性和快速上市優(yōu)勢(shì)帶到這個(gè)行業(yè)標(biāo)準(zhǔn)的處理器技術(shù)中。 &

2006-03-13 13:04:25 741

741 用FPGA實(shí)現(xiàn)FFT算法

引言 DFT(Discrete Fourier Transformation)是數(shù)字信號(hào)分析與處理如圖形、語(yǔ)音及圖像等領(lǐng)域的重

2008-10-30 13:39:20 1426

1426

基于FPGA的高速定點(diǎn)FFT算法的設(shè)計(jì)方案

引 言 快速傅里葉變換(FFT)作為計(jì)算和分析工具,在眾多學(xué)科領(lǐng)域(如信號(hào)處理、圖像處理、生物信息學(xué)、計(jì)算物理

2010-02-09 10:47:50 992

992

在比較已有FFT實(shí)現(xiàn)方法的基礎(chǔ)上,提出一種基于FPGA的通用FFT處理器的設(shè)計(jì)方案。這種FFT實(shí)現(xiàn)結(jié)構(gòu)根據(jù)不同的輸入數(shù)據(jù)長(zhǎng)度動(dòng)態(tài)配置成相應(yīng)的處理器,可以支持多種基數(shù)為2、3、5的FFT計(jì)算,硬件資源得到了優(yōu)化,處理速度及數(shù)據(jù)精度滿足LTE系統(tǒng)中SC-FDMA基帶信號(hào)的

2011-01-16 12:51:03 922

922

提出了一種高速定點(diǎn)FFT 處理器的設(shè)計(jì)方法此方法在CORDIC 算法的基礎(chǔ)上通過(guò)優(yōu)化操作數(shù)地址映射方法和旋轉(zhuǎn)因子生成方法每周期完成一個(gè)基4 蝶形運(yùn)算具有最大的并行性同時(shí)按照本文提出

2011-06-28 18:08:12 28

28 作者提出了一種實(shí)時(shí)可重配置的FFT處理器.該處理器采用小點(diǎn)數(shù)內(nèi)部流水和大點(diǎn)數(shù)二維化處理結(jié)構(gòu),通過(guò)控制各處理模塊實(shí)現(xiàn)4,16,64,256和1 024點(diǎn)復(fù)數(shù)FFT運(yùn)算,并給出了該結(jié)構(gòu)與Hasan結(jié)構(gòu)的

2011-08-23 11:35:20 2370

2370 提出了Radix-4 FFT的優(yōu)化算法,采用該優(yōu)化算法設(shè)計(jì)了64 點(diǎn)流水線IFFT/FFT 處理器,該處理器可以在64 個(gè)時(shí)鐘周期內(nèi)僅采用3 個(gè)復(fù)數(shù)乘法器獲得64 點(diǎn)處理結(jié)果,提高了運(yùn)算速度,節(jié)約了硬件資

2011-12-14 16:03:35 47

47 首先,針對(duì)圖像聲納實(shí)時(shí)性的要求和FPGA片內(nèi)資源的限制,設(shè)計(jì)了級(jí)聯(lián)和并行遞歸兩種結(jié)構(gòu)的FFT處理器。文中詳細(xì)討論了利用流水線技術(shù)和并行處理技術(shù)提高FFT處理器運(yùn)算速度的方法,并

2011-12-27 13:51:14 51

51 DFT(離散傅里葉變換)作為將信號(hào)從時(shí)域轉(zhuǎn)換到頻域的基本運(yùn)算,在各種數(shù)字信號(hào)處理中起著核心作用,其快速算法FFT(快速傅里葉變換)在無(wú)線通信、語(yǔ)音識(shí)別、圖像處理和頻譜分析

2012-05-25 10:18:28 1772

1772

本文主要研究如何利用FPGA實(shí)現(xiàn)FFl’算法,研制具有自主知識(shí)產(chǎn)權(quán)的FFT

信號(hào)處理器

2016-03-21 16:22:52 40

40 高級(jí)FPGA設(shè)計(jì) 結(jié)構(gòu)、實(shí)現(xiàn)和優(yōu)化,適合于FPGA的進(jìn)階學(xué)習(xí)。

2016-05-11 16:40:55 15

15 高級(jí)FPGA設(shè)計(jì) 結(jié)構(gòu)、實(shí)現(xiàn)和優(yōu)化,適合于學(xué)習(xí)FPGA的進(jìn)階學(xué)習(xí)。

2016-05-11 16:40:55 14

14 基于802_11ac的FFT_IFFT處理器設(shè)計(jì)_施隆照

2017-01-03 17:41:32 0

0 基于FPGA的1024點(diǎn)高性能FFT處理器的設(shè)計(jì)_鐘冠文

2017-03-19 11:36:55 10

10 算法及其實(shí)現(xiàn)方法的研究具有很強(qiáng)的理論和現(xiàn)實(shí)意義。 1 FFT 算法及其實(shí)現(xiàn)方法 現(xiàn)場(chǎng)可編程門(mén)陣列 FPGA 是一種可編程使用的信號(hào)處理器件,其運(yùn)算速度高,內(nèi)置高速乘法器可實(shí)現(xiàn)復(fù)雜累加乘法運(yùn)算;同時(shí)其存儲(chǔ)量大,無(wú)需外接存儲(chǔ)器就可實(shí)現(xiàn)大量數(shù)

2017-10-15 10:54:31 20

20 Vviado-HLS基于Xilinx FPGA對(duì)C的解析,綜合原理。Vivado-HLS FPGA并行與處理器架構(gòu) 與處理器架構(gòu)相比,FPGA結(jié)構(gòu)具有更高的并行。Vivado-HLS對(duì)軟件C程序編譯時(shí)與處理器編譯是不一樣的執(zhí)行機(jī)制。

2017-11-18 12:23:09 2377

2377

三角形聯(lián)結(jié)級(jí)聯(lián)H橋拓?fù)潇o止無(wú)功發(fā)生器( SVG)能夠動(dòng)態(tài)補(bǔ)償無(wú)功負(fù)序功率,提高功率因數(shù),抑制電壓閃變和波動(dòng),改善電網(wǎng)電能質(zhì)量,近年來(lái)得到了廣泛研究。對(duì)于級(jí)聯(lián)H橋結(jié)構(gòu)的靜止無(wú)功發(fā)生器,其直流側(cè)電壓控制

2018-03-19 16:07:04 1

1 ,它的計(jì)算量較大。運(yùn)算時(shí)間長(zhǎng),在某種程度上限制了它的使用范圍。快速傅里葉變換(FFT)的提出使DFT的實(shí)現(xiàn)變得接近實(shí)時(shí),DFT的應(yīng)用領(lǐng)域也得以迅速拓展。它在圖像處理、語(yǔ)音分析、雷達(dá)、聲納、地震、通信系統(tǒng)

2019-01-15 10:20:00 2757

2757

的Stratix系列FPGA為例,它具有多達(dá)79 040個(gè)邏輯單元、7 MB的嵌入式存儲(chǔ)器、優(yōu)化的數(shù)字信號(hào)處理器和高性能的I/O能力,非常方便以全并行流水方式進(jìn)行FFT處理。

2020-07-27 17:52:01 1191

1191

針對(duì)高速實(shí)時(shí)信號(hào)處理的要求,介紹了用現(xiàn)場(chǎng)可編程邏輯陣列(FPGA)實(shí)現(xiàn)的一種流水線結(jié)構(gòu)的FFT處理器方案。該FFT處理器能夠?qū)π盘?hào)進(jìn)行實(shí)時(shí)頻譜分析,最高工作頻率達(dá)到75 MHz。通過(guò)對(duì)采樣數(shù)據(jù)進(jìn)行

2021-01-25 14:51:00 12

12 及布局布線,并用ModelSim和Matlab對(duì)設(shè)計(jì)作了聯(lián)合仿真。結(jié)果表明,通過(guò)利用FPGA器件中大量的乘法器、邏輯單元及存儲(chǔ)器等硬件資源,采用全并行加流水結(jié)構(gòu),可在一個(gè)時(shí)鐘節(jié)拍內(nèi)完成32點(diǎn)FFT運(yùn)算的功能,設(shè)計(jì)最高運(yùn)算速度可達(dá)11 ns,可實(shí)現(xiàn)對(duì)高速A/D采樣數(shù)據(jù)的實(shí)時(shí)處理.

2021-03-31 15:22:00 11

11 EE-263:在TigerSHARC?處理器上并行實(shí)現(xiàn)定點(diǎn)FFT

2021-05-16 08:53:56 2

2 基于新型FPGA的FFT設(shè)計(jì)與實(shí)現(xiàn)設(shè)計(jì)方法。

2021-06-17 17:07:03 42

42 摘要:在對(duì)FFT(快速傅立葉變換)算法進(jìn)行研究的基礎(chǔ)上,描述了用FPGA實(shí)現(xiàn)FFT的方法,并對(duì)其中的整體結(jié)構(gòu)、蝶形單元及性能等進(jìn)行了分析。

2022-04-12 19:28:25 4515

4515 差,成本昂貴。隨著FPGA發(fā)展,其資源豐富,易于組織流水和并行結(jié)構(gòu),將FFT實(shí)時(shí)性要求與FPGA器件設(shè)計(jì)的靈活性相結(jié)合,實(shí)現(xiàn)并行算法與硬件結(jié)構(gòu)的優(yōu)化配置,不僅可以提高處理速度,并且具有靈活性高。開(kāi)發(fā)費(fèi)

2023-05-11 15:31:41 1649

1649

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論