利用基于SystemC/TLM的方法學(xué)進(jìn)行IP開發(fā)和FPGA建模

隨著系統(tǒng)級(jí)芯片技術(shù)的出現(xiàn),設(shè)計(jì)規(guī)模正變得越來越大,因而變得非常復(fù)雜,同時(shí)上市時(shí)間也變得更加苛刻。通常RTL已經(jīng)不足以擔(dān)當(dāng)這一新的角色。上述這些因素正驅(qū)使設(shè)計(jì)師開發(fā)新的方法學(xué),用于復(fù)雜IP(硬件和軟件)以及復(fù)雜系統(tǒng)的驗(yàn)證。ST公司建立了一個(gè)設(shè)計(jì)流,它從高級(jí)抽象開始,易于將模型寫入IP的精密周期或RTL模型中。當(dāng)轉(zhuǎn)入低級(jí)抽象時(shí),建模變得復(fù)雜,故IP驗(yàn)證也復(fù)雜。我們的方案最適合于這種應(yīng)用場(chǎng)景,因?yàn)樗试S人們?cè)诟鞯叵嗨频沫h(huán)境中運(yùn)行相同的測(cè)試平臺(tái)和測(cè)試場(chǎng)景,因而允許在整個(gè)開發(fā)周期里高效地復(fù)用所有的測(cè)試范例和環(huán)境。

?

在半導(dǎo)體領(lǐng)域,開發(fā)產(chǎn)品的第一步就是以高級(jí)抽象開發(fā)規(guī)范的模型,通常用C/C++來實(shí)現(xiàn)。這里,SystemC和C++庫提供了很大幫助。它簡(jiǎn)化了共存的硬件和軟件設(shè)計(jì)的概念化。再加上實(shí)現(xiàn)事務(wù)級(jí)模型間對(duì)口連接的TLM傳送庫,SystemC加速了整個(gè)驗(yàn)證過程。另一個(gè)重要方面是所有不同抽象架構(gòu)中經(jīng)過增強(qiáng)的可移植性。同一測(cè)試配置可以無縫地用于不同抽象級(jí)的設(shè)計(jì)。

?

本文將討論一種此類的方法學(xué)。最終的目標(biāo)是設(shè)計(jì)和實(shí)現(xiàn)UWB MAC(媒體訪問層)IP。出于架構(gòu)開發(fā)的目的,決定用SystemC來實(shí)現(xiàn)整個(gè)IP。還開發(fā)了抽象級(jí)具有不同程度變化的不同架構(gòu)。所付出的努力比較少,最后得到的仿真速度很快,軟件的實(shí)際編寫也可以在設(shè)計(jì)周期非常早的階段開始。該IP的RTL結(jié)果被移植到了SPEAr系列的FPGA中。除了ARM內(nèi)核和相應(yīng)的一系列IP,SPEAr還提供一個(gè)可配置邏輯塊,這為用戶在實(shí)現(xiàn)其邏輯功能時(shí)提供了無與倫比的靈活性。從而縮短了上市時(shí)間,同樣也實(shí)現(xiàn)了空前的成本節(jié)省。

?

設(shè)計(jì)開發(fā)方法學(xué)

?

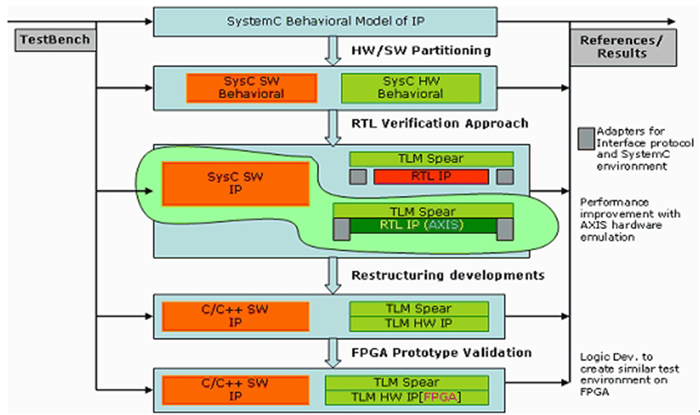

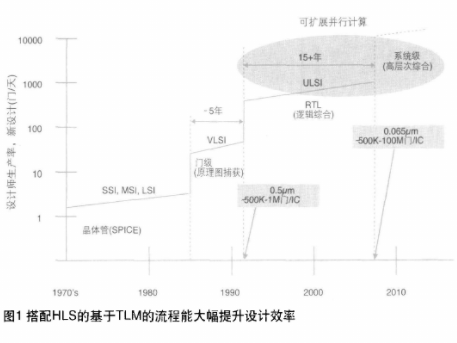

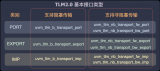

圖1所示的該方法學(xué)實(shí)現(xiàn)了開發(fā)的內(nèi)核中的事務(wù)級(jí)建模(TLM)。TLM是一種對(duì)數(shù)字系統(tǒng)進(jìn)行建模的高級(jí)方案,這里將模塊之間的具體通信與功能單元或通信架構(gòu)的具體實(shí)現(xiàn)分離開。把總線或FIFO這類通信機(jī)制模型化成信道,用SystemC接口類將這些信道提供給模塊和部件。這些信道模型的信令接口功能將取代事務(wù)請(qǐng)求,這將減少具體的低級(jí)信息交換。

?

圖1:IP開發(fā)方法學(xué)流程。

?

在事務(wù)級(jí)建模時(shí),

* 更加注重?cái)?shù)據(jù)轉(zhuǎn)移的功能-即轉(zhuǎn)移的是什么數(shù)據(jù),從那里來,到那里去

* 不太關(guān)注實(shí)際的實(shí)現(xiàn)-即不太關(guān)注數(shù)據(jù)轉(zhuǎn)移所用的實(shí)際協(xié)議

該方案使得系統(tǒng)設(shè)計(jì)師的實(shí)驗(yàn)變得更加容易,例如,可以利用不同的總線架構(gòu)(所有都支持公共的抽象接口),不一定需要對(duì)與任意總線進(jìn)行交互的模型進(jìn)行重新編碼,只要這些模型能夠通過公用接口與總線進(jìn)行交互即可。

?

在我們的方法中,起始點(diǎn)是對(duì)整個(gè)功能系統(tǒng)平臺(tái)進(jìn)行建模。這是利用SystemC并通過sc fifo接口實(shí)現(xiàn)的。為了描述通信接口間的數(shù)據(jù)流,采用了各種架構(gòu)。這些架構(gòu)基本上都是協(xié)議需要遵守的參數(shù)和幀格式信息。圍繞IP創(chuàng)建了一個(gè)測(cè)試環(huán)境,環(huán)境中開發(fā)了測(cè)試平臺(tái),來傳輸分別來自兩側(cè)的輸入,即發(fā)送和接收。在這兩種范例中,利用這種配置產(chǎn)生了預(yù)期的結(jié)果或參考。在抽象層,與平臺(tái)一起使用來進(jìn)行修改,快速并有效地做試驗(yàn)時(shí)將變得很容易,不過精度會(huì)降低一些。

?

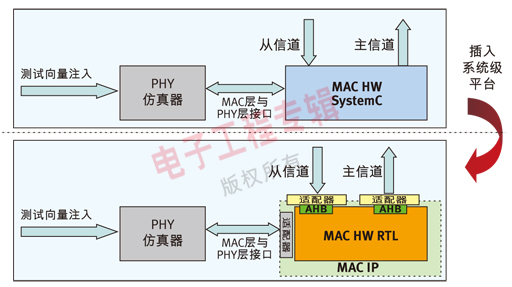

圖中所示為用于開發(fā)中下一級(jí)輸入的配置平臺(tái)。這里的核心思想是確定系統(tǒng)的瓶頸并執(zhí)行軟硬件劃分。該方案在進(jìn)行軟硬件劃分方面是有效并安全的,因?yàn)槠脚_(tái)提供能夠用來識(shí)別出整個(gè)系統(tǒng)瓶頸的原始統(tǒng)計(jì)信息。該階段中,實(shí)現(xiàn)了IP的功能模型,使其具備了具體的接口,并嵌入了功能性。而在軟硬件劃分階段將對(duì)該方法學(xué)中所用的方案進(jìn)行具體化。附加到該平臺(tái)上的另一個(gè)是DMA-PL080的TLM模型,下一步是用MAC HW RTL替代整個(gè)MAC HW SystemC功能模型,如圖2所示。整個(gè)周邊環(huán)境是一樣的,因此測(cè)試注入與其他步驟中的注入一樣。與之前環(huán)境的變化是采用了負(fù)責(zé)到信號(hào)變換的事務(wù)處理適配器。由于該系統(tǒng)基于ARM,適配器的書寫必須遵從信號(hào)級(jí)AHB總線接口。實(shí)際上,該平臺(tái)將相同的環(huán)境表征為現(xiàn)實(shí)系統(tǒng),不過與此同時(shí),開始面對(duì)仿真性能方面的問題。顯然,我們還不能用該配置來執(zhí)行廣泛的調(diào)試/驗(yàn)證,不過可以運(yùn)行簡(jiǎn)單的測(cè)試(具有較短的仿真時(shí)間)。

?

?

圖2:從SystemC MAC HW向VHDL RTL MAC HW適配器的轉(zhuǎn)換。

?

由于在當(dāng)前仿真環(huán)境中發(fā)現(xiàn)瓶頸,我們對(duì)基于硬件模擬XTREME服務(wù)器的平臺(tái)進(jìn)行評(píng)估,該平臺(tái)基本提供了硬件所需的FPGA塊,并提供了軟件與整個(gè)環(huán)境的無縫集成。基于XTREME服務(wù)器中早期平臺(tái)的移植只需要很少工作量,并且相對(duì)于基于ncsim的仿真環(huán)境,實(shí)現(xiàn)了5倍的仿真速度。很顯然,這使得我們能夠調(diào)試并執(zhí)行VHDL RTL設(shè)計(jì)的驗(yàn)證,否則將會(huì)浪費(fèi)過多時(shí)間。同時(shí),基于Xtreme服務(wù)器的平臺(tái)還提供了同等調(diào)試能力。

硬件/軟件劃分

?

系統(tǒng)中軟硬件劃分決策是最為重要的一個(gè)方面。之所以硬件/軟件劃分變得如此關(guān)鍵,是因?yàn)槿缦乱恍┮蛩兀缦到y(tǒng)的實(shí)時(shí)處理需求,應(yīng)用軟件的存儲(chǔ)限制以及其他因素。許多時(shí)候,設(shè)計(jì)開發(fā)階段一些決策依賴于直覺判斷或者先前的經(jīng)驗(yàn)。但當(dāng)某些事情發(fā)生錯(cuò)誤時(shí)這將蘊(yùn)含一個(gè)風(fēng)險(xiǎn)。隨著系統(tǒng)復(fù)雜度以及流片成本的增加,這種決策方法可能會(huì)鑄成大錯(cuò)。強(qiáng)調(diào)需要一種有助于實(shí)現(xiàn)更好軟硬件劃分決策的方法學(xué)具有許多原因。

?

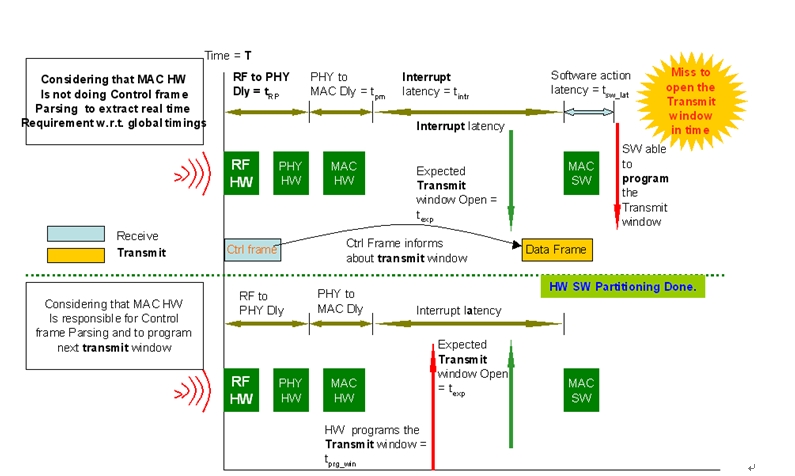

在UWB MAC系統(tǒng)開發(fā)范例中,具有很多必須很好遵守的時(shí)間約束,這是因?yàn)閼?yīng)用層完全依賴于空中——即來自射頻天線的全局廣播定時(shí)。實(shí)現(xiàn)決策的方案建立在我們從具體的系統(tǒng)級(jí)平臺(tái)的執(zhí)行中所獲取的經(jīng)驗(yàn)。我們能夠分析流水線數(shù)據(jù)通道中的數(shù)據(jù)流,能夠有效地發(fā)現(xiàn)它們是否將對(duì)系統(tǒng)構(gòu)成任何瓶頸。通常,當(dāng)系統(tǒng)中的數(shù)據(jù)流發(fā)送時(shí),數(shù)據(jù)幀必須從MAC發(fā)送到PHY,而對(duì)于接收,所產(chǎn)生的數(shù)據(jù)幀則從PHY到MAC,并存入到存儲(chǔ)器中由軟件進(jìn)行進(jìn)一步的分析。在仿真場(chǎng)景分析過程中,能夠識(shí)別出是否需要在硬件中進(jìn)行一些協(xié)議解析以采取及時(shí)的措施。

?

?

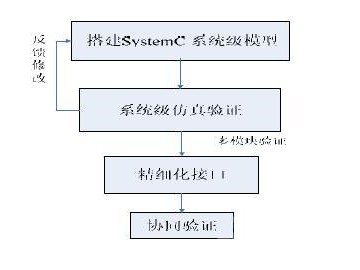

圖3:系統(tǒng)中著重硬件支持需求的應(yīng)用場(chǎng)景。

?

圖3中詳細(xì)給出了一個(gè)決策范例。根據(jù)協(xié)議的需求,接收數(shù)據(jù)中有一個(gè)控制包,它通知下次發(fā)送事件的通用定時(shí),即何時(shí)發(fā)送下一個(gè)數(shù)據(jù)包。考慮到MAC硬件是一個(gè)典型的數(shù)據(jù)通道,并將控制幀傳送到存儲(chǔ)器中,軟件對(duì)控制幀進(jìn)行處理并決定打開發(fā)送窗口。在發(fā)送窗口打開出現(xiàn)問題時(shí),用這種方案就能發(fā)現(xiàn)瓶頸。系統(tǒng)平臺(tái)結(jié)果被用來確認(rèn)這一理解,于是能夠做出更好決策來實(shí)現(xiàn)效率更高的系統(tǒng)。圖3中的另一個(gè)場(chǎng)景顯示了軟硬件劃分后的結(jié)果。

?

第一個(gè)范例中,當(dāng)軟件處理控制幀時(shí),全局定時(shí)如下:

?

窗口編程時(shí)間=T+t RP +tPM+tintr+tsw_lat>T+texp,故在系統(tǒng)中,SW沒有對(duì)及時(shí)打開發(fā)送窗口的指令進(jìn)行編程。

?

在第二個(gè)范例中,當(dāng)MAC HW處理控制幀時(shí),全局定時(shí)為:

窗口編程時(shí)間=T+tprg_win

?

與此同時(shí),現(xiàn)有的SPEAr板起到了很大的幫助作用,因?yàn)樵诎迳蠝y(cè)出了AES-CCM引擎的性能。因此能夠推斷出硬件中存在AES-CCM,因?yàn)锳ES-CCM軟件算法給不出所需要的性能。

?

挑戰(zhàn)

?

被測(cè)設(shè)計(jì)(DUT)或被測(cè)單元(UUT)的測(cè)試對(duì)任何設(shè)計(jì)方法學(xué)來說都是最關(guān)注的一個(gè)方面。在開發(fā)的初始階段,即架構(gòu)評(píng)估階段,必須需要一個(gè)高性能的性能仿真環(huán)境。具有行為功能TLM平臺(tái)能夠滿足這一需求,并對(duì)將要執(zhí)行的功能進(jìn)行功能檢查。當(dāng)進(jìn)入到低級(jí)抽象設(shè)計(jì)階段時(shí),仿真性能大大降低,這成為有效驗(yàn)證IP的一個(gè)問題。

?

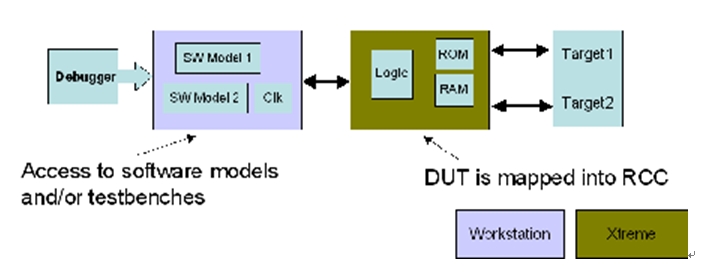

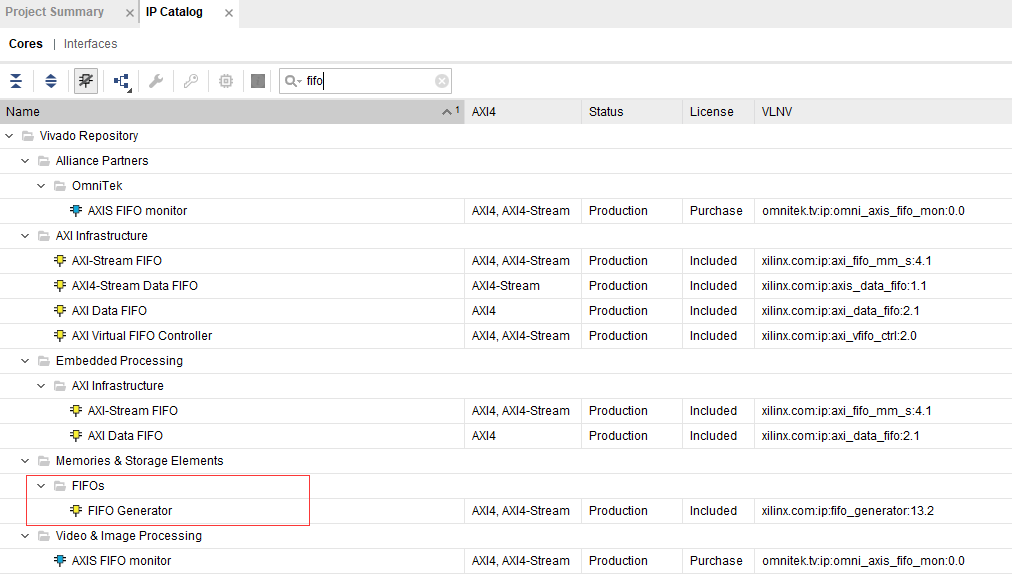

軟硬件的系統(tǒng)級(jí)仿真與軟硬件的協(xié)同仿真一塊進(jìn)行。ST有自己的平臺(tái),這是一個(gè)包含硬件(RTL)的混合平臺(tái),軟件利用SystemC書寫(見圖2)。該平臺(tái)的瓶頸是環(huán)境中所引入IP的RTL,而且注意到這將大大地降低性能。正如預(yù)期,這是所遇到的約束,而且對(duì)是否能夠比主仿真運(yùn)行更快的可能性進(jìn)行了評(píng)估。該方案基于Xtreme服務(wù)器硬件仿真,使得運(yùn)行速度至少要比NCSIM仿真快10倍。

?

?

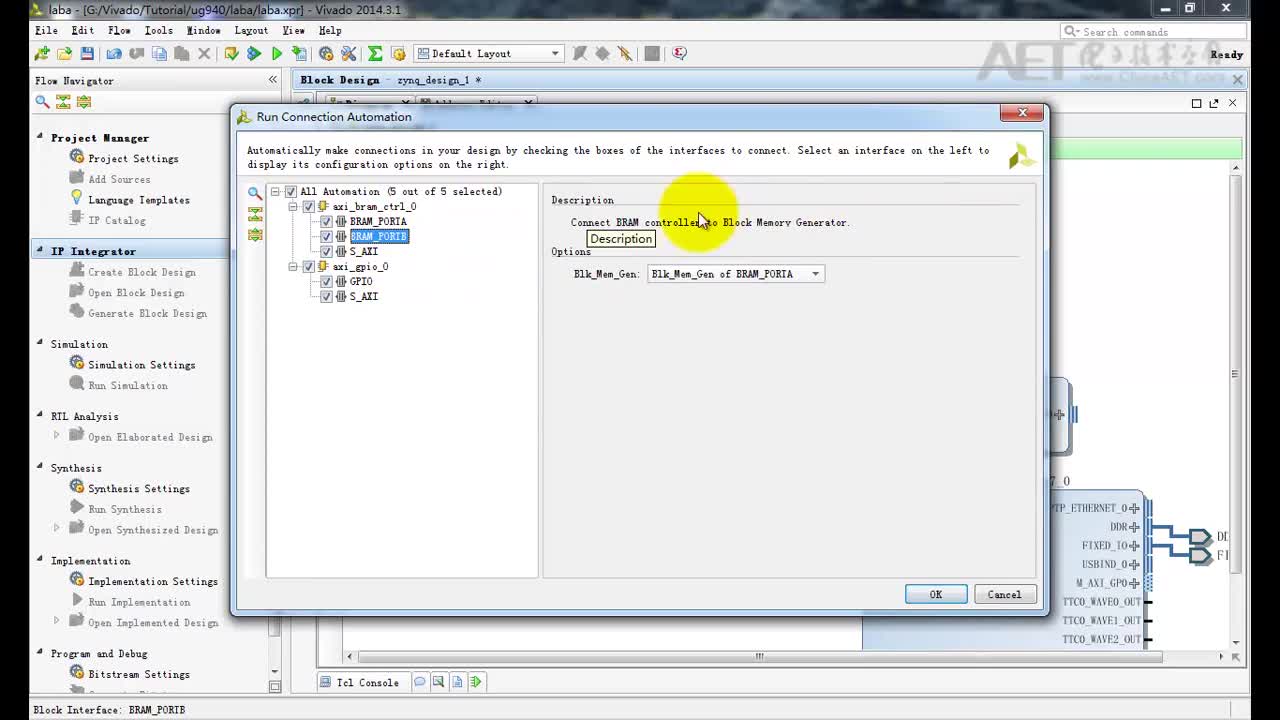

圖4:配有軟件的Xtreme服務(wù)器配置。

?

圖4所示的該技術(shù)對(duì)第一次仿真特別實(shí)用,不需要任何有關(guān)環(huán)境配置方面的工作量。其概念是在Xtreme的FPGA中運(yùn)行RTL IP。開始時(shí),引入的時(shí)鐘為軟件時(shí)鐘,但結(jié)果相當(dāng)可喜,還簡(jiǎn)化了RTL的系統(tǒng)驗(yàn)證和調(diào)試。配置過程中,整個(gè)仿真環(huán)境是類似的,僅有的改變是用VHDL RTL IP替代SysC IP。試驗(yàn)結(jié)果是仿真速度快了10倍。因此,Xtreme服務(wù)器平臺(tái)滿足了RTL驗(yàn)證/調(diào)試所用平臺(tái)的需求。最重要的方面是具有與ncsim同等水平的調(diào)適能力。還提供了與SystemC環(huán)境的無縫集成。

?

調(diào)試功能

?

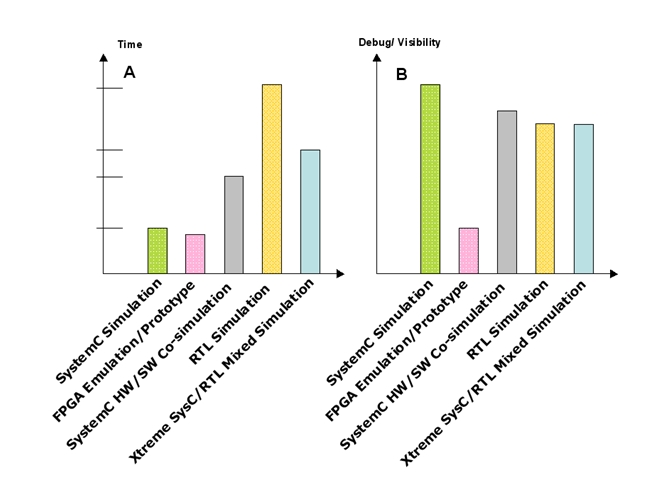

硬件方面的一個(gè)更具挑戰(zhàn)性的問題是調(diào)試。當(dāng)自檢失敗時(shí),就需要一個(gè)相關(guān)的測(cè)試范例。為了驗(yàn)證該測(cè)試范例,在檢查失敗原因時(shí)必須檢查所有的主要信號(hào)。所以需要對(duì)信號(hào)進(jìn)行存放,驗(yàn)證,從而找出具體的原因。利用基于XTREME服務(wù)器的平臺(tái)可以很容易地執(zhí)行所有這些功能,無須額外的工作量。通過將實(shí)際硬件移入獨(dú)立的FPGA,可以很容易地改善仿真速度,不過這種方法提供的調(diào)試功能較少。因此,基于XTREME服務(wù)器的平臺(tái)不僅改善了仿真速度,還能提供非常好的調(diào)試功能。圖5給出了分析結(jié)果。

?

圖5:A)不同平臺(tái)上的仿真性能。B)不同平臺(tái)上的調(diào)試復(fù)雜性。

?

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論