大家有沒(méi)有研究過(guò)用VHDL產(chǎn)生混沌序列的,都來(lái)說(shuō)下,搜不到相關(guān)的資料啊,哪位大神可以提供些意見(jiàn)?

2013-11-01 12:57:10

為Very-high-speed integrated circuit Hardware Description Language,即超高速集成電路硬件描述語(yǔ)言。它有三種數(shù)據(jù)對(duì)象——常數(shù)、信號(hào)、和變量,另外還有

2014-01-04 11:35:34

并行同時(shí)語(yǔ)句命令主要有哪幾種表達(dá)方式?VHDL語(yǔ)言中信號(hào)設(shè)置的不同方式及注意事項(xiàng)

2021-04-08 06:26:43

如何將一個(gè)進(jìn)程中的變量,帶出來(lái),并帶入到另一個(gè)進(jìn)程中進(jìn)行修改后,再將該變量返回原來(lái)的進(jìn)程中????本人對(duì)VHDL新手一個(gè),調(diào)試了好長(zhǎng)時(shí)間也沒(méi)成功,望哪位大神指點(diǎn)迷津,謝謝了(急!!!!)

2016-06-26 10:05:12

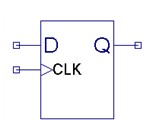

]重點(diǎn):VHDL語(yǔ)言的程序結(jié)構(gòu);VHDL語(yǔ)言的數(shù)據(jù)類型及數(shù)據(jù)對(duì)象。難點(diǎn):VHDL的數(shù)據(jù)對(duì)象中的變量和信號(hào)的區(qū)別。[理論內(nèi)容]一、VHDL的程序結(jié)構(gòu)圖1 VHDL的程序結(jié)構(gòu)圖圖1中是VHDL的全部結(jié)構(gòu),但

2009-03-19 14:52:00

使用。書(shū)中還附有大量程序設(shè)計(jì)和實(shí)驗(yàn)、實(shí)踐方面的習(xí)題。本書(shū)可作為高等院校的電子工程、通信、工業(yè)自動(dòng)化、計(jì)算機(jī)應(yīng)用技術(shù)、電子對(duì)抗、儀器儀表、數(shù)字信號(hào)處理、圖像處理等學(xué)科領(lǐng)域和專業(yè)的高年級(jí)本科生或研究生的VHDL

2008-06-04 10:31:29

vhdl頂層模塊可以調(diào)用子模塊內(nèi)部定義的信號(hào)嗎?怎么調(diào)用。。。。。verilog可以的,這樣可以方便調(diào)試。。。。。

2013-08-08 11:27:42

信號(hào)與時(shí)鐘的關(guān)系,在組合電路中信號(hào)是離散的,還是連續(xù)的?在組合電路延時(shí)為啥不可估計(jì)?答:這是同步電路研究的范疇,將數(shù)字電路系統(tǒng)中的信號(hào)分為兩類:離散信號(hào) 和 連續(xù)信號(hào)。同步電路中的離散信號(hào),重點(diǎn)研究

2018-03-07 11:13:32

什么是DSP圖像處理系統(tǒng)?DSP圖像處理系統(tǒng)中信號(hào)完整性的問(wèn)題是什么?有哪些解決方案?

2021-06-01 06:40:35

VHDL 對(duì)象有 4 種,即信號(hào)(Signal)、變量(Variable)、常量(Constant)和文件(File)。其中文件(File)是 VHDL’93 標(biāo)準(zhǔn)中新通過(guò)的,它是不可以綜合的。下面

2018-09-10 10:14:49

在Multisim中信號(hào)源產(chǎn)生的信號(hào)都是非常標(biāo)準(zhǔn)的信號(hào),如何使其產(chǎn)生帶有雜波或其他固定頻率的信號(hào)?

2014-11-06 17:20:22

請(qǐng)問(wèn),各位大蝦,labview8.2以后版本中,如何嵌入c語(yǔ)言,在采集數(shù)據(jù)時(shí),嵌入的c語(yǔ)言中如何調(diào)用采集到的信號(hào)變量。謝謝!

2012-05-10 14:13:56

對(duì)于line profile 和IMAQ histgram怎么分析圖中信息,怎么把表中信息與圖中信息對(duì)應(yīng),以及IMAQ histgram中飽和度與對(duì)比度的問(wèn)題,thanks。。。。。

2013-03-08 10:14:22

現(xiàn)在工程是多個(gè)人開(kāi)發(fā)維護(hù),有的使用VHDL,有的使用Verilog,因此工程是Verilog VHDL混合結(jié)構(gòu),兩部分模塊有相互調(diào)用關(guān)系。在使用debussy調(diào)試時(shí),從nTrace中添加信號(hào)到

2016-01-10 18:37:53

我仿真一個(gè)簡(jiǎn)單的電路,但不太會(huì)protues中信號(hào)發(fā)生器和示波器的應(yīng)用調(diào)節(jié),下圖是我自己畫的仿真電路,但是運(yùn)行老出錯(cuò),不知道是哪里的原因

2014-12-17 09:23:25

chufa信號(hào)第一個(gè)上升沿開(kāi)始,下面信號(hào)就跳為高電平,如何用VHDL實(shí)現(xiàn)????請(qǐng)高手指點(diǎn),謝謝!

2012-04-18 10:00:04

VHDL 對(duì)象有 4 種,即信號(hào)(Signal)、變量(Variable)、常量(Constant)和文件(File)。其中文件(File)是 VHDL’93 標(biāo)準(zhǔn)中新通過(guò)的,它是不可以綜合的。下面

2018-09-12 09:32:49

VHDL 不僅僅提供了一系列的順序語(yǔ)句,同樣也提供了很多并行語(yǔ)句。在 VHDL 中,并行語(yǔ)句主要包括以下幾種:? 進(jìn)程(PROCESS)語(yǔ)句;? 塊(BLOCK)語(yǔ)句;? 并發(fā)信號(hào)賦值;? 條件信號(hào)

2018-09-13 10:14:51

為什么我在操作自動(dòng)布線的時(shí)候,不能選中信號(hào)線或者電源線之類的?

2019-09-19 04:23:37

本帖最后由 Leo_Tseng 于 2012-10-1 17:40 編輯

在VHDL中,a:=b;c:=a;為什么不能在同一進(jìn)程中出現(xiàn)?變量的值不是立即變化的嗎?這樣有什么不可以的呢?為什么在verilog中就可以呢

2012-10-01 17:04:22

在仿真里,信號(hào)的驅(qū)動(dòng)究竟是在時(shí)鐘沿之前還是在時(shí)鐘沿之后?》關(guān)于仿真中信號(hào)驅(qū)動(dòng)那點(diǎn)事兒 記得在SystemVerilog中,對(duì)于仿真時(shí)信號(hào)的驅(qū)動(dòng)綠皮書(shū)里有這么兩個(gè)建議:時(shí)鐘信號(hào)驅(qū)動(dòng)賦值采用=。其他

2022-06-24 16:34:49

梯形圖的原理與特性梯形圖-VHDL設(shè)計(jì)方法梯形圖的VHDL描述方法

2021-04-30 07:28:11

大家好,如果我正在編寫一個(gè)具有40個(gè)輸出信號(hào)的VHDL代碼,每個(gè)代碼都是16位,那么最好將其作為單個(gè)輸出寫入std_logic_vector(639 downto 0)或者我應(yīng)該更好地寫40

2019-02-15 09:50:24

/tests.vhd”第386行:找到運(yùn)算符“+”的'0'定義,無(wú)法確定“+”的精確重載匹配定義這是VHDL代碼: 變量addr:std_logic_vector(31 downto 0

2019-04-10 11:42:27

嗨,對(duì)于學(xué)校項(xiàng)目,我需要設(shè)計(jì)一個(gè)信號(hào)發(fā)生器,它可以產(chǎn)生持續(xù)時(shí)間為60-70 ms的數(shù)字按鍵音信號(hào)(DTMF),可用于DTMF電話。之后的信號(hào)將被饋送到板載現(xiàn)有的數(shù)模轉(zhuǎn)換器,然后饋送到現(xiàn)有的板載

2019-03-13 07:14:02

你好, 如何將std_logic_vector(15 downto 0)的信號(hào)轉(zhuǎn)換為整數(shù)然后傳遞它或?qū)⑵溆糜赩DL模塊的變量? 我嘗試了以下但得到錯(cuò)誤 在VHDL模塊中...實(shí)體foobar是港口

2019-04-18 06:30:20

有什么方法可以提高無(wú)線系統(tǒng)中信號(hào)處理功能的性能呢?

2021-04-29 06:16:07

大家好,我想使用IO時(shí)鐘接口對(duì)輸入中的串行信號(hào)進(jìn)行過(guò)采樣。然后,該信號(hào)將由vhdl編程邏輯與全局時(shí)鐘一起使用。我希望使用IO時(shí)鐘以更高的頻率對(duì)這些輸入數(shù)據(jù)進(jìn)行采樣,而不是全局時(shí)鐘提供的數(shù)據(jù),但我

2019-08-07 09:51:55

嗨,我正在研究用于Xilinx FPGA設(shè)計(jì)的HDL。我遇到了一種情況,我希望將vhdl生成循環(huán)索引增加2。一個(gè)例子如下所示,LABEL:for i in 1 to CNTR_WIDTH -1

2019-01-16 08:12:42

一、VHDL簡(jiǎn)介1.1 VHDL 的歷史VHDL 的 英 文 全 名 是 Very-High-Speed Integrated Circuit Hardware

2020-09-02 19:32:26

旋轉(zhuǎn)電弧傳感信號(hào)濾波研究摘要:旋轉(zhuǎn)電弧焊接過(guò)程中信號(hào)的濾波與提取是焊接過(guò)程中首要解決的問(wèn)題,介紹了電弧傳感的工作原理與焊接信號(hào)的特點(diǎn),對(duì)旋轉(zhuǎn)電弧焊接中使用的數(shù)字濾波方法做了介紹,通過(guò)實(shí)驗(yàn)對(duì)各個(gè)方法

2009-10-13 14:57:03

本文介紹有關(guān)FreeRTOS中信號(hào)量和計(jì)數(shù)信號(hào)量在使用過(guò)程中需要注意的細(xì)節(jié),以及自己在過(guò)程中的分享的一些有關(guān)遇到的問(wèn)題和注意點(diǎn)。

2021-08-06 06:26:05

可直接使用 書(shū)中還附有大量程序設(shè)計(jì)和實(shí)驗(yàn)/實(shí)踐方面的習(xí)題本書(shū)可作為高等院校的電子工程 通信 工業(yè)自動(dòng)化 計(jì)算機(jī)應(yīng)用技術(shù) 電子對(duì)抗儀器儀表 數(shù)字信號(hào)處理 圖像處理等學(xué)科領(lǐng)域和專業(yè)的高年級(jí)本科生或研究

2012-02-27 13:52:50

了最后出現(xiàn)問(wèn)題是CPU引腳上的很多線沒(méi)有辦法走通了,求信號(hào)流向是按照信號(hào)的輸入還是按照輸出流向來(lái)進(jìn)行呢3、求雙面板布局中信號(hào)線和電源線如何考慮才能夠完美布通呢求路過(guò)的大神指點(diǎn)7 g- X

2014-10-20 14:59:11

解決背板互連中信號(hào)完整性問(wèn)題的兩種方案

2019-09-16 09:08:59

用VHDL語(yǔ)言編出一個(gè)電壓信號(hào)源,再編出一個(gè)積分電路,放大電路,濾波電路,移相電路對(duì)這個(gè)信號(hào)源進(jìn)行處理

2015-05-26 21:29:51

高速數(shù)合邏輯電路中信號(hào)線的電磁發(fā)射頻譜原理 提要 本文主要討論高速數(shù)合邏輯電路中,信號(hào)線的電磁發(fā)射頻譜。作者提供一個(gè)模型

2009-10-21 14:59:54

在高速電路設(shè)計(jì)中信號(hào)完整性分析由于系統(tǒng)時(shí)鐘頻率和上升時(shí)間的增長(zhǎng),信號(hào)完整性設(shè)計(jì)變得越來(lái)越重要。不幸的是,絕大多數(shù)數(shù)字電路設(shè)計(jì)者并沒(méi)意識(shí)到信號(hào)完整性問(wèn)題的重要性,或者是直到設(shè)計(jì)的最后階段才初步認(rèn)識(shí)到

2009-10-14 09:32:02

高速數(shù)字硬件電路設(shè)計(jì)中信號(hào)完整性在通常設(shè)計(jì)的影響是什么?高速電路設(shè)計(jì)中信號(hào)完整性面臨的挑戰(zhàn)有哪些?怎么處理?

2021-04-22 06:26:55

正弦波信號(hào)發(fā)生器VHDL源代碼

2008-01-02 20:46:30 236

236 一篇用VHDL實(shí)現(xiàn)快速傅立葉變換的論文,包括原理分析和代碼實(shí)現(xiàn),印度圣雄甘地大學(xué)M.A.學(xué)院提供

2008-05-20 11:01:15 59

59 VHDL語(yǔ)言及其應(yīng)用是在作者歷時(shí)七年為通信與信息系統(tǒng)、信號(hào)與信息處理專業(yè)研究生講授VHDL語(yǔ)言及其應(yīng)用課程的教學(xué)實(shí)踐基礎(chǔ)上編寫而成的。全書(shū)共分15章,以教授完整的VHDL語(yǔ)言體

2009-02-12 09:41:38 172

172 應(yīng)用變頻器控制技術(shù), 使液壓定量泵實(shí)現(xiàn)變量功能。在此變量原理的基礎(chǔ)上設(shè)計(jì)了一個(gè)由變頻器控制的復(fù)合變量泵。通過(guò)理論和仿真研究表明, 這種復(fù)合變量泵具有結(jié)構(gòu)簡(jiǎn)單、控制靈

2009-04-06 15:03:27 20

20 剖析硬件描述語(yǔ)言VHDL-AMS 的新特性。通過(guò)對(duì)A/D 轉(zhuǎn)換器和D/A 轉(zhuǎn)換器進(jìn)行建模和仿真分析可以看出,VHDL-AMS 突破了VHDL 只能設(shè)計(jì)數(shù)字電路的限制,使得VHDL 可以應(yīng)用于模擬以及混合信

2009-07-08 09:49:23 22

22 VHDL語(yǔ)言及其應(yīng)用是在作者歷時(shí)七年為通信與信息系統(tǒng)、信號(hào)與信息處理專業(yè)研究生講授VHDL語(yǔ)言及其應(yīng)用課程的教學(xué)實(shí)踐基礎(chǔ)上編寫而成的。全書(shū)共分15章,以教授完整的VHDL語(yǔ)言體

2009-07-10 17:21:44 18

18 VHDL語(yǔ)言及其應(yīng)用的主要內(nèi)容:第一章 硬件模型概述第二章 基本的VHDL編程語(yǔ)言第三章 VHDL模型的組織第四章 VHDL綜合工具第五章 VHDL應(yīng)用樣例附錄A VHDL

2009-07-20 12:06:15 0

0 低壓電力線載波通信中信號(hào)傳輸特性分析:

2009-08-06 15:53:21 98

98 VHDL 語(yǔ)言程序的元素:本章主要內(nèi)容:VHDL語(yǔ)言的對(duì)象VHDL語(yǔ)言的數(shù)據(jù)類型VHDL語(yǔ)言的運(yùn)算符VHDL語(yǔ)言的標(biāo)識(shí)符VHDL語(yǔ)言的詞法單元

2009-09-28 14:32:21 41

41 本篇介紹了高速數(shù)字硬件電路設(shè)計(jì)中信號(hào)完整性在通常設(shè)計(jì)的影響。這包括特征阻抗控制、終端匹配、電源和地平面、信號(hào)布線和串?dāng)_等問(wèn)題。掌握這些知識(shí),對(duì)一個(gè)數(shù)字電路設(shè)

2009-10-14 09:30:27 60

60 VHDL基礎(chǔ)教程:VHDL語(yǔ)言及其應(yīng)用目錄:第1章 VHDL基本概念 1.1 數(shù)字系統(tǒng)建模 1.2 建模的域和級(jí) 1.3 建模語(yǔ)言 1.4 VHDL建模的概念 1.5 一個(gè)VHDL設(shè)計(jì)實(shí)例 1 6

2009-10-16 18:17:58 357

357 基于DSP 的架空電導(dǎo)線蠕變量測(cè)試系統(tǒng)研究

摘要本文針對(duì)電纜蠕變特性測(cè)量的需求,描述了架空電導(dǎo)線蠕變量測(cè)試系統(tǒng)的測(cè)試原理與軟硬件組成。該系統(tǒng)充分運(yùn)用DSP 芯片的各

2010-04-02 15:22:38 17

17 vhdl是什么意思

VHDL 語(yǔ)言的英文全名是 Very High Speed Integrated Circuit Hardware Description Language ,即超高速集

2008-09-02 12:55:59 7732

7732 VHDL語(yǔ)言應(yīng)用實(shí)例指導(dǎo)

VHDL中的標(biāo)識(shí)符可以是常數(shù)、變量、信號(hào)、端口、子程序或參數(shù)的名字。使用標(biāo)識(shí)符要遵守如下法則

2009-03-20 14:15:53 2064

2064

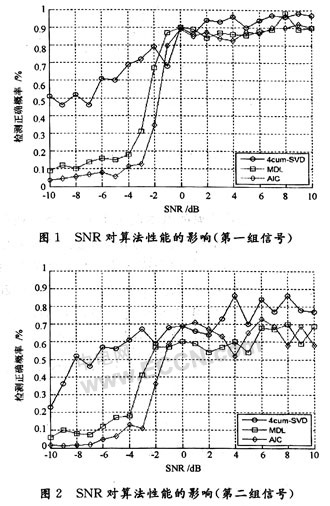

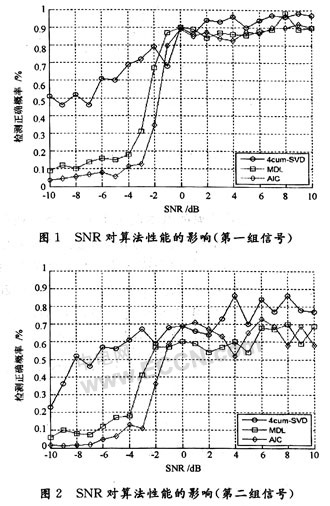

高階累積量在欠定盲源分離中信源數(shù)目估計(jì)的應(yīng)用

0引言盲源信號(hào)分離(Blind Source Separation,BSS)是指從觀測(cè)到的多源混合信號(hào)中分離并恢復(fù)出相對(duì)獨(dú)立的源信號(hào)過(guò)

2010-01-21 17:15:05 1593

1593

摘要: 通過(guò)一個(gè)偶同位產(chǎn)生器邏輯功能的實(shí)現(xiàn)過(guò)程,介紹了VHDL語(yǔ)言中信號(hào)設(shè)置的不同方 式及注意事項(xiàng),并給出了完整的程序代碼。 關(guān)鍵詞: VHDL;程序 1 概述 VHDL是一種快速的 電路

2011-10-06 08:48:28 1091

1091

本文就談?wù)勔粋€(gè)基礎(chǔ)概念:信號(hào)上升時(shí)間和信號(hào)帶寬的關(guān)系。對(duì)于數(shù)字電路,輸出的通常是方波信號(hào)。方波的上升邊沿非常陡峭,根據(jù)傅立葉分析,任何信號(hào)都可以分解成一系列不同頻

2011-11-30 15:48:44 3607

3607

--多進(jìn)制數(shù)字頻率調(diào)制( MFSK )系統(tǒng)VHDL程序 --文件名:MFSK --功能:基于 VHDL 硬件描述語(yǔ)言,完成對(duì)基帶信號(hào)的MFSK調(diào)制 --說(shuō)明:這里MFSK的M為4 --最后修改日期:2004.2.13 library ieee; use ieee.st

2012-05-22 09:21:39 1035

1035 隨著對(duì)IEEE1641標(biāo)準(zhǔn)研究的逐漸深入,信號(hào)的構(gòu)建成為了研究重點(diǎn)。對(duì)信號(hào)模型進(jìn)行同步和門控控制,可以影響到TSF(測(cè)試信號(hào)框架)模型的輸出,從而達(dá)到控制信號(hào)的目的,使測(cè)試需求

2012-11-26 16:28:44 28

28 學(xué)好VHDL的重要性 對(duì)VHDL的 介紹

2016-09-02 16:54:40 17

17 為所定義的整數(shù)限定取值的范圍,然后根據(jù)所定義的范圍決定它是信號(hào)還是變量的二進(jìn)制數(shù)的位數(shù),因?yàn)?b class="flag-6" style="color: red">VHDL綜合器無(wú)法綜合未限定范圍的整數(shù)類型的信號(hào)或變量.

2016-11-21 15:40:34 0

0 VHDL實(shí)用教程,很好的一本教材,適合初學(xué)者

2016-11-11 15:51:00 15

15 VHDL例程 ADC_TLC449采集信號(hào)顯示到數(shù)碼管,感興趣的小伙伴們可以瞧一瞧。

2016-11-10 17:12:34 7

7 vhdl入門

2016-12-16 16:30:02 23

23 在世界范圍內(nèi),關(guān)于VHDL在多個(gè)領(lǐng)域尤其在芯片,系統(tǒng)設(shè)計(jì)方面的應(yīng)用研究已經(jīng)取得眾多矚目成果。而將VHDL與醫(yī)學(xué)相結(jié)合,勢(shì)必成為電子自動(dòng)化設(shè)計(jì)(EDA)一個(gè)全新的研究方向,本文主要研究將EDA通過(guò)VHDL應(yīng)用于醫(yī)學(xué),以對(duì)脈搏的測(cè)量為例,以實(shí)現(xiàn)數(shù)字系統(tǒng)對(duì)人體多種生理活動(dòng)及生理反應(yīng)的直觀精確測(cè)量。

2018-05-23 11:17:00 1729

1729

VHDL中的標(biāo)識(shí)符可以是常數(shù)、變量、信號(hào)、端口、子程序或參數(shù)的名字。VHDL中的數(shù)據(jù)類型可以分成四大類: 標(biāo)量型(SCALAR TYPE):屬單元素的最基本的數(shù)據(jù)類型,通常用于描述一個(gè)單值數(shù)據(jù)對(duì)象

2018-03-30 15:59:52 11

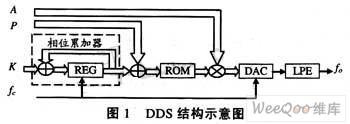

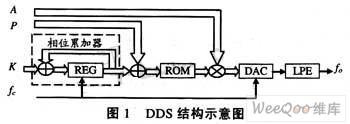

11 語(yǔ)言,可描述硬件電路的功能、信號(hào)連接關(guān)系及定時(shí)關(guān)系,在電子工程領(lǐng)域用來(lái)描述、驗(yàn)證和設(shè)計(jì)電子線路,得到了廣泛應(yīng)用。故將VHDL語(yǔ)言與DDS技術(shù)結(jié)合,設(shè)計(jì)生成BPSK信號(hào)。

2018-10-07 11:00:38 6065

6065

本文檔的主要內(nèi)容詳細(xì)介紹的是VHDL教程之使用VHDL進(jìn)行電子設(shè)計(jì)所需的所有資料包括了:VHDL設(shè)計(jì)基礎(chǔ)知識(shí),VHDL并行語(yǔ)句,VHDL程序?qū)嶓w,VHDL入門,VHDL語(yǔ)言要素,EDA設(shè)計(jì)流程及其工具,IA64 應(yīng)用程序寄存器,LCD液晶顯示漢字字符集表,OCMJ 系列液晶顯示器控制命令集表等

2018-09-25 08:00:00 0

0 VHDL的數(shù)據(jù)類型有多種,它們各自為數(shù)據(jù)對(duì)象定義了一組數(shù)值的集合,以及針對(duì)這些值所允許的操作。VHDL對(duì)運(yùn)算關(guān)系與賦值關(guān)系中各量的數(shù)據(jù)類型有嚴(yán)格的要求。VHDL要求設(shè)計(jì)實(shí)體中的每一個(gè)常數(shù)、信號(hào)、變量、函數(shù)以及設(shè)定的各種參量都必須有確定的數(shù)據(jù)類型,只有相同數(shù)據(jù)類型的量才能互相傳遞和作用。

2018-10-17 08:00:00 0

0 本文檔的主要內(nèi)容詳細(xì)介紹的是VHDL教程之VHDL語(yǔ)言元素的詳細(xì)資料概述一內(nèi)容包括了:1. VHDL語(yǔ)言的客體2 VHDL語(yǔ)言的數(shù)據(jù)類型3 VHDL數(shù)據(jù)類型轉(zhuǎn)換4 VHDL詞法規(guī)則與標(biāo)識(shí)符

2018-11-05 08:00:00 0

0 在VHDL程序中,實(shí)體(ENTITY)和結(jié)構(gòu)體(ARCHITECTURE)這兩個(gè)基本結(jié)構(gòu)是必須的,他們可以構(gòu)成最簡(jiǎn)單的VHDL程序。通常,最簡(jiǎn)單的VHDL程序結(jié)構(gòu)中還包含另一個(gè)最重要的部分,即庫(kù)(LIBRARY)和程序包(PACKAGE)。

2020-04-23 15:43:38 4224

4224 什么是vhdl語(yǔ)言 VHDL 的英文全名是VHSIC Hardware Description Language(VHSIC硬件描述語(yǔ)言)。VHSIC是Very High Speed

2020-04-23 15:58:49 10242

10242 在VHDL程序設(shè)計(jì)中,可以充分利用信號(hào)或變量的系統(tǒng)默認(rèn)值,來(lái)靈活實(shí)現(xiàn)設(shè)計(jì)目標(biāo)。本文從應(yīng)用的角度舉例說(shuō)明了VHDL設(shè)計(jì)中信號(hào)與變量的區(qū)別,以及正確的使用方法,并介紹了為信號(hào)或變量賦予初始值的技巧。

2020-07-16 08:54:12 7500

7500

VHDL中的標(biāo)識(shí)符可以是常數(shù)、變量、信號(hào)、端口、子程序或參數(shù)的名字。使用標(biāo)識(shí)符要遵守如下法則:

2020-07-16 09:00:53 11150

11150 現(xiàn)如今互聯(lián)網(wǎng)可以說(shuō)已經(jīng)成為了日常生活的剛需,在我們的日常生活和工作中是不可或缺的。雖然連接網(wǎng)絡(luò)的方式是多元化的,但Wi-Fi可以說(shuō)是用的最多的。信號(hào)再?gòu)?qiáng)的路由器都會(huì)存在信號(hào)死角,而產(chǎn)生信號(hào)死角最主要的原因就是家居結(jié)構(gòu),例如戶型復(fù)雜、大戶型或是別墅等復(fù)式結(jié)構(gòu)。不知各位是如何解決家中信號(hào)盲區(qū)的呢?

2020-09-15 17:16:55 7063

7063 本文檔的主要內(nèi)容詳細(xì)介紹的是如何使用VHDL硬件描述語(yǔ)言實(shí)現(xiàn)基帶信號(hào)的MPSK調(diào)制。

2021-01-19 14:34:21 2

2 3月1日和中信集團(tuán)協(xié)同委員會(huì)上海區(qū)域分會(huì)簽署全面戰(zhàn)略合作協(xié)議,開(kāi)啟與中信銀行上海分行、中信證券及中信保誠(chéng)人壽上海分公司的全方位深入合作,并獲中信銀行50億元綜合授信額度,

2021-03-11 14:31:23 1290

1290 軟件無(wú)線電中信號(hào)中頻與采樣頻率選擇說(shuō)明。

2021-03-25 09:50:52 13

13 總結(jié)了在高速PCB板設(shè)計(jì)中信號(hào)完整性產(chǎn)生的原因、抑制和改善的方法。介紹了使用IBS模型的仿真步驟以及使用 CADENCE公司的 Allegro SPB軟件,支持IBIS模型對(duì)反射和串?dāng)_的仿真,驗(yàn)證了其改善后的效果,可以直觀地看到PCB設(shè)計(jì)是否滿足設(shè)計(jì)要求,進(jìn)而指導(dǎo)和驗(yàn)證高速PCB的設(shè)計(jì)。

2021-05-27 13:59:31 20

20 CAN系統(tǒng)中信號(hào)終端電阻常見(jiàn)問(wèn)題及解決方法

2021-05-28 10:20:27 19

19 在產(chǎn)品的研發(fā)中,如何捕獲長(zhǎng)時(shí)間測(cè)試中信號(hào)的一個(gè)偶發(fā)異常,是工程師們經(jīng)常遇到的問(wèn)題。本文將為大家提供一種新的方式,僅需一臺(tái)機(jī)器,工程師就可以對(duì)高達(dá)128路信號(hào)進(jìn)行長(zhǎng)時(shí)間可靠性監(jiān)控測(cè)試。

2022-01-02 09:11:00 1330

1330 這些顯示電子系統(tǒng)中信號(hào)波形的動(dòng)圖,有助于幫助我們理解傳輸?shù)臋C(jī)理。

2022-03-22 08:57:48 1571

1571 下面這些顯示電子系統(tǒng)中信號(hào)波形的動(dòng)圖,有助于幫助我們理解傳輸?shù)脑恚窒斫o大家。

2022-11-30 10:59:34 653

653 這些顯示電子系統(tǒng)中信號(hào)波形的動(dòng)圖,有助于幫助我們理解傳輸?shù)臋C(jī)理。

2022-12-06 11:09:17 2235

2235 System Verilog提供兩組通用的數(shù)據(jù)類型:網(wǎng)絡(luò)和變量(nets 和 variables)。網(wǎng)絡(luò)和變量同時(shí)具有類型和數(shù)據(jù)類型特性。類型表示信號(hào)為網(wǎng)絡(luò)或變量,數(shù)據(jù)類型表示網(wǎng)絡(luò)或變量的值系統(tǒng),即2態(tài)或4態(tài)。

2023-02-09 14:40:08 751

751

vhdl描述半加器

2023-02-24 11:08:31 0

0 模型機(jī)控制信號(hào)產(chǎn)生邏輯VHDL 引言: 隨著科技的發(fā)展,數(shù)字系統(tǒng)的設(shè)計(jì)越來(lái)越重要。在數(shù)字系統(tǒng)設(shè)計(jì)的過(guò)程中,模型機(jī)控制信號(hào)的產(chǎn)生邏輯是一個(gè)非常重要的方面。本文將介紹VHDL語(yǔ)言在模型機(jī)控制信號(hào)產(chǎn)生邏輯

2023-09-19 17:16:08 339

339 電子發(fā)燒友網(wǎng)站提供《基于OCDMA的無(wú)源光網(wǎng)絡(luò)中信道噪聲優(yōu)化方法研究.pdf》資料免費(fèi)下載

2023-10-09 14:19:51 0

0

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論