數據采集板作為雷達信號處理系統中的接收前端,必須面對越來越高的要求,為后續信號處理提供可靠的保證。將數據采集板獨立設計提高了通用性,降低了系統的研制時間,因此成為雷達信號處理系統設計的發展趨勢。采用ADC和FPGA設計了基于CPCI總線的數據采集板,實現了8路信號同時中頻采樣及處理,并已應用于雷達系統中。

?

?關鍵詞: 數據采集板;ADC;FPGA;CPCI???

?

?The Design and Realization of the Data Sampling Board?

?

?Abstract:

With the development of modern radar,the data sampling board used as the receiver of a system of radar signal processing must face the increasingly high requirements,and guarantee the reliability of posterior signal processing.The data sampling board is designed specially,which improves the generality and shortens the time for design,so that it has become the development trend of signal processing system design.This paper adopts FPGA and ADC to design a data sampling board for signal processing based on the CPCI Bus,which accomplishes eight channels of IF signal sampling and processing,and has been used in some radar systems.

??

?Keywords: data sampling board;ADC;FPGA;CPCI???

隨著先進雷達功能多樣化、復雜化, 要求研制、裝備周期越來越短, 有必要設計一種通用性強、功能強大的數據采集板, 以支持雷達技術發展的需要, 這無論是在硬件還是軟件編程的實現方面, 都為其可通用性打下堅實的基礎。在實現技術上, 近些年來, 一改以往傳統的模擬處理方法, 多采用數字中頻正交采樣技術, 這種做法直接對模擬中頻信號進行單路采樣, 再以一定方法實現數字下變頻, 得到所需的兩路正交信號。由于兩路信號是經數字處理得到的, 因此可以達到較高的精度,兩路正交信號的幅度和相位一致性都較好。

文中所設計的系統正是基于上述幾點應用而生的, 采用的核心器件是Analog Devices公司的A /D芯片和Altera 高端高密度、低功耗、低成本的FPGAStratix II, 設計了基于CPCI總線的數據采集板, 實現了單板8路信號的中頻采樣及數據的實時處理, 并在某雷達系統中進行了實際應用。

1 系統設計

所要設計的系統可以同時接收8 路中頻模擬信號, 并在FPGA中同時對8路數字信號進行下變頻處理, 得到所需要的檢波信號, 然后送往后端繼續進行處理。實際硬件設計實現中, 系統大致可分為模擬和數字兩部分, 模擬部分實現中頻采樣, 核心器件采用的是AD6645ASQ; 數字部分實現數字下變頻(DDC) ,通過FPGA (EP2S60)來實現。

模擬部分選用美國Analog Devices公司的模數轉換芯片AD6645ASQ, 它是一個完整的14 位集成ADC, 功耗115 W, 芯片結構采用的是串/并行編碼相結合的方法, 兼顧速度與成本, 其主要特性在于:中頻采樣最高能到200MHz; 輸入時鐘和模擬信號都采用差分電平格式, 降低了干擾; 器件信噪比高; 而且其工作溫度范圍(環境) : - 40~ + 85°C[ 7 ] , 能夠滿足一般雷達系統對環境溫度要求 。數字部分選用的是Altera 公司采用112 V,90 nm, 9層金屬走線、全銅SRAM工藝制造的中高端FGPA產品Stratix II系列的EP2S60, 采用全新的邏輯結構: 自適應邏輯模塊(ALM) , 兼有“窄”邏輯結構的高利用率和“寬”邏輯結構的高性能, 實際中可以根據用戶的需求由設計工具自動配置成需要的模式。它內含144個18 ×18的定點硬件乘法器, 24 176個自適應邏輯模塊以及215MB的內嵌RAM, 豐富的硬件資源足以實現其對系統的8路中頻信號進行實時處理成為可能。

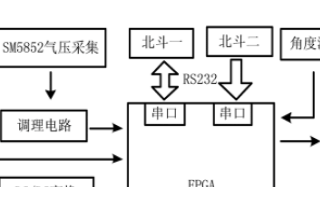

系統硬件總體結構, 如圖1所示。

圖1 系統硬件總體架構

8路模擬信號經由50Ω匹配電路, 通過A /D直接對中頻信號進行采樣和幅度量化, 再由FPGA得到正交雙通道數據的方法來實現正交相干檢波, 處理后數據經并/串轉換送往CPC I_J5 口供后端繼續處理,處理時所需的控制信號同樣由此接口輸入; 各芯片工作所用的時鐘信號由中間的時鐘電路統一產生, 保證各時鐘的相位基本一致。

2 數字正交采樣在數據采集板上的系統實現

211 數據采集板中頻采樣的實現一個中頻窄帶信號可以表示為

30MHz的線性調頻信號, 設計系統時M 值取為2,則時鐘設計所定的fs = 40 MHz, 通過FPGA實測得到中頻采樣數據, 如圖2所示。

圖2 FPGA實測中頻采樣數據

2 12 數據采集板數字下變頻的實現

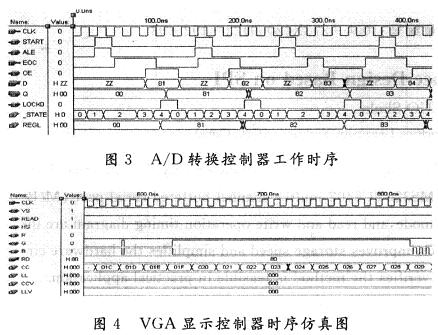

對中頻實信號進行采樣后, 下一步是進行數字混頻和濾波處理, 使信號變為零中頻正交信號(零中頻正交信號即是回波信號的復包絡, 包含了回波的所有有用信息) , 即為數字下變頻, 其作為雷達信號處理中的關鍵技術之一, 這里采用低通濾波法來實現, 低通濾波法包括正交插值、低通濾波和抽樣3個部分。數字下變頻的算法框圖, 如圖3所示。

圖3 數字下變頻算法框圖

? 相比于傳統的模擬處理方法, 本方法從根本上解決I, Q兩路正交誤差和幅度不平衡, 提高了鏡頻抑制比。

?? 其中混頻, 即點乘的實現, 根據中頻帶通采樣定理有

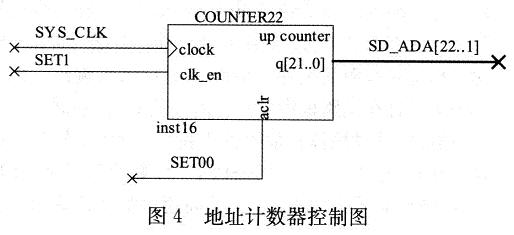

這是以{1, 0, - 1, 0}和{0, 1, 0, - 1}為周期循環的兩個序列。當外部數據進來時根據不同時刻輸出不同的數據, 主要包括原值、原值取反和0。其FPGA實現電路, 如圖4所示。

圖4 數字混頻的FPGA實現電路

在整個正交相干檢波過程中, 除了ADC的量化影響外, 整個正交檢波系統的性能, 由低通濾波器的設計決定。由于鏡頻分量處于濾波器的阻帶, 因而阻帶衰減決定了鏡頻的抑制程度。文中采用的低通濾波器為24階F IR濾波器, 其阻帶衰減> 70 dB鏡頻分量得到了較好的抑制 。24階FIR濾波器的頻率特性, 如圖5所示。

輸入時寬帶寬積為55的線性調頻信號, 實測的I路與Q路波形, 如圖6所示。

把實測數據導到Matlab進行分析, 得到鏡頻抑制比滿足系統的要求, 如圖7所示。

圖7 系統實測數據, 低通濾波法頻率歸一化后的鏡頻抑制比數據采集板實物圖, 如圖8所示。

3 結束語

文中設計的基于CPCI總線的數據采集板, 8路信號同時采集并處理, 兼備強大的數據處理能力和高實時性。整個系統實現的是數字正交采樣, 無論是中頻采樣, 還是數字下變頻, 都有一定的通用性, 在以后類似的應用中, 無需重新設計, 只需通過資源分配和算法的再實現, 足以達到預期的效果, 保證可靠性的同時也大大的縮短了研制周期。

圖8 數據采集板實物圖

實時性。整個系統實現的是數字正交采樣, 無論是中頻采樣, 還是數字下變頻, 都有一定的通用性, 在以后類似的應用中, 無需重新設計, 只需通過資源分配和算法的再實現, 足以達到預期的效果, 保證可靠性的同時也大大的縮短了研制周期。

參考文獻

[ 1 ] Analog Devices. AD6645 14 bit, 80 /105 MSPS A /D ConverterData Sheet [ Z]. USA: Analog Devices, 2005.

[ 2 ] Altera Corporation. Stratix III Handbook [ Z]. USA: Altera Corporation, 2008.

[ 3 ] 鄭君里, 應啟珩, 楊為理. 信號與系統[M ]. 2版. 北京: 人民郵電出版社, 2002.

[ 4 ] 何海興. 多模式雷達中正交檢波和脈沖壓縮的研究與實現[D ]. 西安: 西安電子科技大學, 2007.

[ 5 ] 王本明. 基于CPCI總線的通用FPGA信號處理板設計[D ]. 西安: 西安電子科技大學, 2009.

[ 6 ] 胡成岡. FPGA在雷達信號處理中的應用[D ]. 西安:西安電子科技大學, 2007.

電子發燒友App

電子發燒友App

評論