人為地對雷達進行測試時,有時只對雷達的某個和某些參數感興趣,希望在回波中表征感興趣的參數強一些,這時就應該在回波中去掉雜波和噪聲的影響,而這在實際的外場試飛過程中是不可能實現的,這也是雷達信號模擬器對場外試飛的一大優勢。這種真實的模擬將會更利于專業人員的分析。

FPGA作為高性能數字信號處理系統中的關鍵部件,在雷達信號模擬和雷達信號采集等方面有著巨大的開發潛能,采用這些技術對雷達系統和環境進行模擬,可以多次的使用和調試,并能夠模擬同一情況下雷達的性能,便于詳細分析。我們的設計是采用集成微處理器的FPGA,同時完成信號模擬和時序控制的功能,改變了以往信號處理DSP+FPGA中FPGA作為協處理器的模式[1-3]。整個設計僅需要具有嵌入內核的FPGA和簡單的外圍電路,使系統的集成度更高,由于FPGA在信號處理中并行處理的優勢,系統實時性強。系統采用工業標準的總線結構以及模塊化設計,具有良好的通用性、兼容性以及可擴充性。

1 系統組成

1.1 雷達信號的模擬

雷達信號模擬模塊主要完成對雷達中頻和視頻模擬。其中中頻信號模擬可以模擬產生雷達中頻線性調頻脈沖信號,視頻信號模擬可以模擬一路非相參視頻信號或兩路相參視頻信號。雷達信號模擬模塊內部包括:天線控制、觸發控制、波門控制以及信號產生等子模塊。天線控制模塊根據天線參數產生天線掃描信號;觸發控制模塊根據觸發信號參數產生周期性的觸發脈沖信號;波門控制模塊根據天線掃描信號、觸發脈沖信號以及目標方位、仰角和距離參數在指定方位、仰角和距離上選通波門輸出目標信號,信號產生模塊根據參數設置產生對應幅度。

在雷達的測試系統中,常常需要模擬日標回波;同時,為了測試雷達的抗干擾特性,還需要產生欺騙干擾的信號。DRFM(數字射頻存儲器)由于可以高保真的存儲和復制采樣信號,測試系統不僅可以產生多個假目標,還可以產生距離拖引干擾和速度拖引干擾。

1.2 雜波的模擬

雜波是雷達回波的重要組成部分,只有對雜波有效的建模,并將其疊加在目標信號上,才能使模擬出的雷達回波更接近真實情況。通常該模型用統計隨機過程來描述。

雜波的模擬有2種途徑:

(1)利用Matlab在電腦上產生。首先根據雷達環境和被測雷達參數,選擇合適的雜波模型以及統計特征參數,建立雜波數據庫;然后在計算機中利用零記憶非線性變換法產生雜波隨機序列[4]。目前最常用的雜波幅度分布模型有韋布爾模型、對數正態模型和K分布模型,設計中產生表示雷達雜波幅度的N個數據樣本Z1,Z2,…ZN,這些樣本具有上述某種給定的概率分布和任意給定的功率譜,將這些隨機樣本序列在磁盤上保存下來。PC機上實現隨機序列,具有幅度分布和頻譜特性可選擇的優點。

(2)利用線性反饋移位寄存器產生隨機的數字噪聲。LFSR可以被視為一個線性移位寄存器組,并且每個寄存器的輸入都是它前一個寄存器輸出的一個線性函數。在FPGA中設計一個16 bit隨機數字噪聲模擬模塊,此序列發生器的初始值為0XFFFF,數字噪聲信號的周期為216-1=65 535。基于硬件實現的隨機序列,具有循環周期長、隨機性好、資源消耗少的優點。

在實時模擬時,基于雷達天線波束與雜波區域幾何關系,用戶可以根據情況選擇使用哪種方法產生隨機序列,通過硬件和軟件系統直接模擬雷達的雜波回波信號。

1.3 干擾信號的模擬

雷達干擾信號的模擬能夠模擬真實戰場環境下的一些干擾信號,包括噪聲干擾以及欺騙性干擾,從而可實現對雷達抗干擾性能的檢測。噪聲干擾包括多普勒噪聲干擾、瞄準式噪聲干擾、調頻噪聲干擾;欺騙干擾包括距離欺騙、速度欺騙、假目標等。

噪聲干擾信號的形式比較復雜,主要是通過上位機產生對應的數據,以文本的形式存儲下來。在配置FPGA時,將文本文件作為ROM的初始化文件,在編程過程中以查表的形式生成噪聲干擾信號。

對脈沖雷達距離信息的欺騙主要是通過對收到的雷達照射信號進行延時調制和放大轉發來實現。由于單純的距離質心干擾造成的距離誤差較小,所以對脈沖雷達距離信息的欺騙主要采用距離假目標干擾和距離波門拖引干擾。距離假目標干擾的模擬在FPGA中體現出來的就是2組重復頻率不同的脈沖串,2組脈沖串之間的時間差就對應著延時調制,可以通過計數器控制2個脈沖之間的延遲調制。波門拖引干擾時,通過FPGA控制脈沖寬度和對應的功率水平,最終將目標回波脈沖分為2個脈沖,且假目標的功率水平比真實目標的功率水平要高。

1.4 實測數據的信號重構

國內在雷達數據采集方面的研究日趨成熟,基于PCI、USB接口的數據采集系統都能滿足雷達中視頻采樣的要求,而且可以根據需要將采集的數據存盤或軟件實時回放處理[5-7]。本系統解決的問題是將系統采集到的數據或磁盤陣列上存儲的其他系統采集到的雷達實測數據通過模擬系統重構出雷達回波信號,做到真實環境的可重復再現,為雷達接收系統性能的檢測提供了有利條件。信號重構過程需要知道雷達回波采樣時的采樣率,保證模擬系統DA信號輸出的速率與數據采集時的采樣速率一致,避免采集和恢復速率的不匹配造成雷達信號的非線性失真。同時實測數據幀的組成形式必須是已知的,這樣才能提取雷達信號的同步、方位、仰角等信息,將對應的幅度信息與方位、仰角同步。

2 具體實現

2.1 硬件設計

FPGA采用的是Xilinx公司的100萬門FPGA芯片XC3S1000,其配置芯片為Xilinx公司的4 MB容量PROM芯片XCF04S,以主動串行方式對FPGA進行上電配置。AD、DA分別為ADI公司12位105 MS/s高速模/數轉換芯片AD9432與14位105 MS/s高速數/模轉換芯片AD9764。SRAM采用Cypress公司的256k×16 bit SRA。

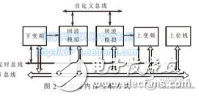

M芯片CY7C1041用于對數據進行大容量緩存,以滿足USB的傳輸需要。USB控制器選用Cypress公司的EZ-USB FX2系列USB2.0芯片CY7C68013,封裝為PQFP128。它支持USB2.0高速傳送,最高速率可達480 Mb/s。系統框圖如圖2所示。

Xilinx 公司簡介

Xilinx 是業界領先的可編程平臺提供商。根據市場分析公司 iSuppli 公司統計,Xilinx 在 2010 財政年度創造了18 億美元的收益,并在半導體行業可編程邏輯器件 (PLD) 領域占有 50% 以上的市場份額。Xilinx 可編程芯片是當今業界領先企業為其數以萬計的產品的設計首選的創新平臺,這些產品能夠顯著改善我們的日常生活質量。

ADI公司簡介

ADI公司是業界廣泛認可的數據轉換和信號調理技術全球領先的供應商,擁有遍布世界各地的60,000客戶,他們事實上代表了全部類型的電子設備制造商。ADI公司作為高性能模擬集成電路(IC)制造商慶祝公司在此行業全球領先40多年,其產品廣泛用于模擬信號和數字信號處理領域。

2.2 FPGA程序設計

FPGA程序主要包括雷達信號模擬模塊、雷達信號采集與傳輸控制模塊和SDK中Microblaze的控制與參數傳遞模塊。雷達信號模擬模塊主要完成對雷達中頻/視頻和雜波信號的模擬,為雷達的接收系統和信號采集模塊提供自檢測試信號。雷達信號采集與傳輸控制模塊主要完成對雷達中頻/視頻信號的采集與傳輸控制,該模塊為系統真實回波的模擬提供了實測數據。參數的傳遞主要由兩部分組成:上位機的信號參數輸入或信號模擬系統自帶的鍵盤掃描輸入與Microblaze核之間的參數傳遞;Microblaze將對應的輸入參數通過中斷調用的形式傳遞給信號或雜波產生模塊。在ISE 9.1環境下通過VHDL硬件語言產生脈沖、LFM等信號,利用EDK 9.1的附件將在ISE 9.1中產生的信號模塊轉化為對應的IP核[8]。在EDK開發中,可以將在ISE中產生的信號模擬的IP核直接添加到工程中,IP核和Microblaze處理器之間通過OPB總線實現信號參數和中斷信號的傳遞,使整個開發過程模塊化。基于FPGA的嵌入式系統設計的EDK開發中有硬件模塊設計和軟件控制2個部分,使整個系統兼容了FPGA并行處理的高速率和軟件編程的簡潔。

2.3 驅動程序設計與使用

FX2的設備驅動程序有2種:一種用來在設備接入時從主機下載固件到RAM中,稱為固件下載驅動程序(wdgtldr.sys);另一種是在設備重新列舉后加載的通用設備驅動程序(ezusb.sys),應用軟件通過該設備驅動程序與FX2通信[9]。

固件下載驅動程序(wdgtldr.sys)是利用Cypress公司提供的固件下載驅動程序源代碼和用戶編譯成功的固件代碼,在Win2000 DDK中創建的。在將固件代碼下載到RAM中后,系統清除內存中的固件下載驅動程序,并進行重新列舉,讓8051固件控制FX2。此時,系統獲得由8051固件提供的新的ID號,認為有新的USB設備接入,并據此加載相應的通用設備驅動程序。通用設備驅動程序一般不需要重新編寫,可以直接使用Cypress公司已經編好的驅動程序ezusb.sys。

3 系統調試結果

利用信號模擬產生一些典型的雷達視頻信號,驗證了系統在工程上的可行性。

圖3為頻率控制字為1 500時的線性調頻脈沖信號,脈寬為10 μs

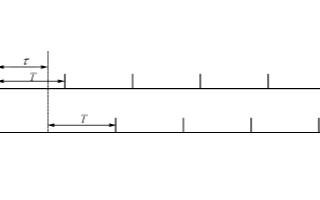

圖4為非相參視頻脈沖串,脈沖寬度為10 μs,重復周期為700 μs

圖5為相參視頻脈沖串,脈沖寬度為10 μs,重復周期為700 μs,多普勒調制頻率為200 Hz。

基于FPGA嵌入式系統的雷達目標模擬器的設計利用了嵌入微處理器FPGA在控制方面的靈活性,在修改參數重新對FPGA進行配置時,只需完成對應的軟件編譯,節省了芯片再配置的時間;完成了相參、非相參、線性調頻脈沖串等雷達中頻、視頻信號的模擬和韋布爾、對數正態、K分布3種典型分布模型的雜波模擬;利用實測雷達回波數據實現了實際雷達回波的重構,該系統產生的信號能夠基本滿足雷達接收系統性能的測試。

?

電子發燒友App

電子發燒友App

評論