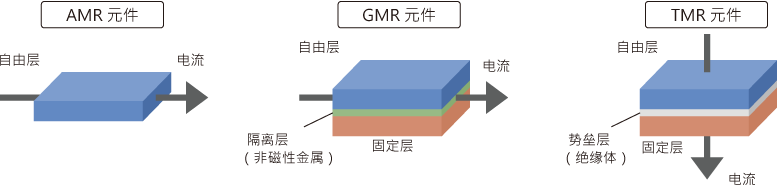

TMR傳感器

2023-08-22 10:36:50 1647

1647

摘要:FPGA異步時(shí)鐘設(shè)計(jì)中如何避免亞穩(wěn)態(tài)的產(chǎn)生是一個(gè)必須考慮的問(wèn)題。本文介紹了FPGA異步時(shí)鐘設(shè)計(jì)中容易產(chǎn)生的亞穩(wěn)態(tài)現(xiàn)象及其可能造成的危害,同時(shí)根據(jù)實(shí)踐經(jīng)驗(yàn)給出了解決這些問(wèn)題的幾種同步策略。關(guān)鍵詞

2009-04-21 16:52:37

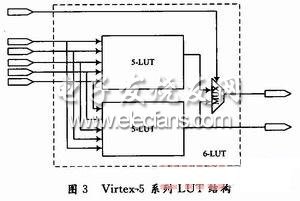

EDA技術(shù)具有什么特征?FPGA是什么原理?FPGA設(shè)計(jì)應(yīng)用及優(yōu)化策略基于VHDL的FPGA系統(tǒng)行為級(jí)設(shè)計(jì)

2021-04-15 06:33:58

TMR - DC/DC Converters - TRACO Electronic AG

2022-11-04 17:22:44

TMR - Radial Ceramic Monolithic Capacitor - TAITRON Components Incorporated

2022-11-04 17:22:44

TMR 0510

2023-03-28 13:12:00

TMR 0522

2023-03-28 13:16:25

TMR 2410

2023-03-28 13:12:00

TMR 2411

2023-03-28 13:12:00

TMR 3-2412E

2023-03-28 13:12:00

TMR 9-2411WI

2023-04-06 23:33:38

您好,我用TIC18F685有一個(gè)TMR0的問(wèn)題。在寫(xiě)期間,我的T0CON寄存器除位3(PSA)外,所有位都已清除。在我寫(xiě)到TMR0H后,我寫(xiě)到TMR0L,然后清除IF并啟動(dòng)計(jì)時(shí)器。表窗口顯示

2020-03-27 08:55:00

嗨,所有的,我正在實(shí)驗(yàn)TMR0,給一個(gè)可變頻率輸出。在我的代碼中,主例程讀取一個(gè)電位計(jì)作為一個(gè)模擬輸入的5V,并輸出值到一個(gè)LCD顯示器。我還有一個(gè)TMR0 ISR,它切換一個(gè)輸出引腳(XOWF

2019-04-12 15:15:31

嗨,伙計(jì)們,我一直在研究一個(gè)計(jì)時(shí)器(TMR3)用來(lái)測(cè)量?jī)蓚€(gè)外部中斷之間的時(shí)間的項(xiàng)目。另一計(jì)時(shí)器(TMR1)用于計(jì)數(shù)是否發(fā)生過(guò)溢出。第一個(gè)中斷啟動(dòng)計(jì)時(shí)器,第二個(gè)中斷關(guān)閉它,并調(diào)用一些后續(xù)計(jì)算的函數(shù)

2018-12-14 16:38:37

AT32F系列 TMR溢出中斷演示AT32F4xx TMR使用更新中斷的方法。

2023-10-27 06:17:46

AT32F系列TMR_OCHigh輸出演示AT32F系列TMR_OCHigh輸出的使用方法。

2023-10-27 07:34:47

AT32F系列TMR_OCToggle輸出演示AT32F系列TMR_OCToggle輸出的使用方法。

2023-10-27 06:20:49

AT32F系列單周期模式演示AT32F系列TMR單周期模式的使用方法。

2023-10-27 06:58:38

AT32F4xx TMR掛起模式演示AT32F系列 TMR門(mén)控模式的使用方法。

2023-10-27 06:21:33

人工智能大熱之前,Cloud或Data Center已經(jīng)開(kāi)始使用FPGA做各種加速了。而隨著Deep Learning的爆發(fā),這種需求越來(lái)越強(qiáng)勁。本文主要討論Cloud巨頭Amazon和Microsoft的FPGA策略。

2019-08-13 08:37:24

EVT v17,Observer模式下,應(yīng)用TMR1 TMR2輸出PWM信號(hào),無(wú)輸出;TMR0 和 TMR3 PWM都正常,請(qǐng)問(wèn)是哪里出了問(wèn)題?嘗試了各種方法都搞不定。

2022-08-09 06:56:14

有人能解釋一下TMR1H和TMR1L是如何計(jì)算的嗎?數(shù)據(jù)表沒(méi)有解釋,既不是DS31012A,也不是AN580。公式是什么?我在4MHz使用內(nèi)部OSC,在異步模式下使用TMR1。 以上來(lái)自于百度翻譯

2018-10-10 16:31:37

利用 FPGA 實(shí)現(xiàn)大型設(shè)計(jì)時(shí),可能需要FPGA 具有以多個(gè)時(shí)鐘運(yùn)行的多重?cái)?shù)據(jù)通路,這種多時(shí)鐘 FPGA 設(shè)計(jì)必須特別小心,需要注意最大時(shí)鐘速率、抖動(dòng)、最大時(shí)鐘數(shù)、異步時(shí)鐘設(shè)計(jì)和時(shí)鐘/數(shù)據(jù)關(guān)系

2012-03-05 14:42:09

大家好。我試圖用PIC16F628A@20MHz的TMR2控制伺服電機(jī)。我把定時(shí)器設(shè)置為每隔1ms溢出(預(yù)分頻器=4;TMR2寄存器=130),然后在中斷例程中,伺服管腳被保持在高或低,因?yàn)榇a顯示

2019-06-17 07:53:32

基于FPGA的三相電流型PWM整流器過(guò)調(diào)制策略的研究

2017-09-30 09:17:14

本帖最后由 mingzhezhang 于 2012-5-23 20:05 編輯

大型設(shè)計(jì)中FPGA的多時(shí)鐘設(shè)計(jì)策略 利用FPGA實(shí)現(xiàn)大型設(shè)計(jì)時(shí),可能需要FPGA具有以多個(gè)時(shí)鐘運(yùn)行的多重

2012-05-23 19:59:34

本示例代碼基于 AT32F403A,展示了如何使用 AT32 的 TMR 和 DMA 動(dòng)態(tài)更新 PWM 占空比。該示例使用 TMR4 的更新事件觸發(fā) DMA1 搬運(yùn)數(shù)據(jù)至 TMR4 的通道 2 數(shù)據(jù)

2023-10-27 06:28:03

你好,對(duì)于我的無(wú)刷直流感應(yīng)控制器,我需要知道PWM定時(shí)器的值,但是這個(gè)定時(shí)器在軟件上是不可讀的。所以我想把PWM定時(shí)器復(fù)制到一個(gè)普通的定時(shí)器,例如TMR4。有沒(méi)有一種簡(jiǎn)單的方法來(lái)同步PMTMR和TMR4?我現(xiàn)在做的是使用PWM1中斷來(lái)重置TMR4值。

2019-10-28 09:34:58

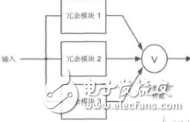

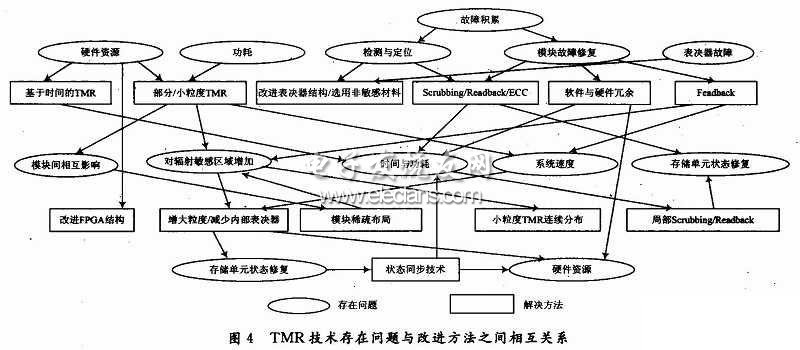

軟故障是是由粒子和PN結(jié)相互作用引起的一種暫態(tài)故障,軟故障對(duì)在基于SRAM的FPGA上實(shí)現(xiàn)的電路具有特別嚴(yán)重的影響。由于三模冗余(TripleModularRedundancy,TMR)技術(shù)簡(jiǎn)單

2019-08-27 07:28:32

AT32F系列32位定時(shí)器演示AT32F系列TMR 32位定時(shí)器的使用方法。

2023-10-27 08:29:55

量化策略里的MAX方法是指min-max嗎

2023-09-19 06:38:27

針對(duì)交互式遺傳算法中收斂速度慢和容易陷入局部收斂的缺點(diǎn),提出遺傳算法算子的一些改進(jìn)策略,即利用定位部分優(yōu)良基因方法,使這些基因較好地遺傳到下一代。改進(jìn)的算法能

2009-04-03 08:38:14 17

17 提出了一種改進(jìn)的模板匹配方法。該方法是在傳統(tǒng)的模板匹配方法的基礎(chǔ)上,通過(guò)對(duì)模板匹配算法的改進(jìn),以達(dá)到更快速的匹配結(jié)果。實(shí)驗(yàn)結(jié)果表明,此方法可以快速測(cè)出管腳個(gè)

2009-09-03 15:15:24 9

9 一種基于本體的PageRank算法的改進(jìn)策略:介紹Google 等搜索引擎應(yīng)用的PageRank 算法的定義、特點(diǎn)及缺陷。針對(duì)PageRank 算法在基于Ontology 的海洋文檔檢索系統(tǒng)應(yīng)用中的問(wèn)題對(duì)其加以改

2009-10-17 23:01:56 15

15 一種改進(jìn)型PWM調(diào)制策略逆變器的研究與應(yīng)用::針對(duì)帶獨(dú)立直流源的級(jí)聯(lián)型多電平逆變器各逆變單元間應(yīng)力分配不均衡的問(wèn)題,提出了一種新的調(diào)制方法。通過(guò)控制各逆變單元開(kāi)關(guān)的

2009-10-27 17:52:04 20

20 TMR繼電器模塊

2009-11-20 17:10:56 20

20 頻率測(cè)量方法的改進(jìn)

2010-10-14 16:41:00 20

20 大型設(shè)計(jì)中FPGA的多時(shí)鐘設(shè)計(jì)策略

利用FPGA實(shí)現(xiàn)大型設(shè)計(jì)時(shí),可能需要FPGA具有以多個(gè)時(shí)鐘運(yùn)行的多重?cái)?shù)據(jù)通路,這種多時(shí)鐘FPGA設(shè)計(jì)必須特別小心,需要注意最大時(shí)鐘速率

2009-12-27 13:28:04 645

645

FPGA芯片選擇策略和原則

由于FPGA具備設(shè)計(jì)靈活、可以重復(fù)編程的優(yōu)點(diǎn),因此在電子產(chǎn)品設(shè)計(jì)領(lǐng)域得到了越來(lái)越廣泛的應(yīng)用。在工程項(xiàng)目或者產(chǎn)品設(shè)計(jì)

2010-02-09 09:13:29 3080

3080 基于FPGA設(shè)計(jì)DSP的實(shí)踐與改進(jìn)

當(dāng)設(shè)計(jì)的系統(tǒng)需要對(duì)數(shù)字信號(hào)進(jìn)行處理時(shí),常采用通用 DSP(Digital Signal Process)處理器,這樣的設(shè)計(jì)方案通用性好,且還有各種較為成熟的

2010-03-01 10:47:56 554

554

利用FPGA實(shí)現(xiàn)時(shí)分多址的方法有很多種,但大多數(shù)方法都對(duì)FPGA芯片資源的占用非常巨大。針對(duì)這一問(wèn)題,提出一種改進(jìn)型方法來(lái)實(shí)現(xiàn)時(shí)分多址。通過(guò)使用FPGA芯片內(nèi)部的雙口隨機(jī)訪問(wèn)存儲(chǔ)器(雙口RAM),利用同一塊RAM采用兩套時(shí)鐘線,地址線和數(shù)據(jù)線,例化雙口RAM的

2011-01-15 15:41:26 29

29 本資料是關(guān)于Altera FPGA的選型及開(kāi)發(fā),內(nèi)容大綱是:Altera的 FPGA體系結(jié)構(gòu)簡(jiǎn)介;Altera的 FPGA選型策略;嵌入式邏輯分析工具SignalTAPII的使用;基于CPLD的FPGA配制方法。

2012-08-15 14:48:34 103

103 TMR3 Dual Timer,PCB學(xué)習(xí)好資料,歡迎下載學(xué)習(xí)。

2016-03-23 10:38:09 0

0 磁場(chǎng)定向控制中SVPWM過(guò)調(diào)制策略的改進(jìn)與實(shí)現(xiàn)

2016-04-13 15:42:35 20

20 實(shí)時(shí)圖像增強(qiáng)算法改進(jìn)及FPGA實(shí)現(xiàn),下來(lái)看看

2016-09-17 07:28:24 14

14 基于改進(jìn)下垂法的光伏微電網(wǎng)并網(wǎng)控制策略研究_孟凡姿

2017-01-02 15:24:00 0

0 統(tǒng)一電能質(zhì)量控制器并聯(lián)側(cè)的改進(jìn)雙滯環(huán)電流控制策略研究_程啟明

2017-01-07 18:12:51 1

1 一種改進(jìn)的NLMS自適應(yīng)濾波器的FPGA實(shí)現(xiàn)_趙茂林

2017-01-08 10:30:29 2

2 一種改進(jìn)的共形陣方向圖綜合方法_夏歡

2017-01-08 11:07:01 0

0 一種改進(jìn)的無(wú)功及諧波電流檢測(cè)方法_毛宇陽(yáng)

2017-01-08 11:20:20 2

2 基于改進(jìn)模糊卡爾曼濾波的感應(yīng)電機(jī)轉(zhuǎn)速估計(jì)策略研究_王鑫博

2017-01-08 11:20:20 1

1 基于有限狀態(tài)機(jī)的五橋臂逆變器改進(jìn)調(diào)制策略_梅楊

2017-01-08 13:58:48 0

0 多策略改進(jìn)RBF神經(jīng)網(wǎng)絡(luò)入侵檢測(cè)方法研究_邵洪濤

2017-03-19 11:29:00 0

0 一種改進(jìn)的關(guān)聯(lián)規(guī)則個(gè)性化推薦方法_饒泓

2017-03-14 17:12:31 2

2 TMR效應(yīng)在時(shí)柵傳感器中的應(yīng)用_魏家琦

2017-03-19 18:58:37 3

3 基于TMR的二線制角度傳感器設(shè)計(jì)_張珂

2017-03-19 19:12:42 4

4 數(shù)字PWM方法的改進(jìn)

2017-09-11 10:29:49 12

12 在二進(jìn)制離散無(wú)記憶信道中極化碼可以達(dá)到其信道極限容量,并且實(shí)現(xiàn)的復(fù)雜度較低,這在通信領(lǐng)域無(wú)疑是一個(gè)重大突破,因此在FPGA中實(shí)現(xiàn)極化碼的譯碼有著非常重要的研究意義。首先介紹了SC

2017-11-15 16:50:25 4340

4340

針對(duì)標(biāo)準(zhǔn)粒子濾波算法存在的粒子退化與貧化問(wèn)題,提出了一種新的改進(jìn)粒子濾波算法。該算法采用無(wú)跡卡爾曼濾波、優(yōu)化組合策略和標(biāo)準(zhǔn)粒子濾波相結(jié)合的方法,運(yùn)用UKF產(chǎn)生重要性密度函數(shù),解決標(biāo)準(zhǔn)PF算法

2017-11-17 17:42:48 10

10 基于SRAM 的FPGA對(duì)于空間粒子輻射非常敏感,很容易產(chǎn)生軟故障,所以對(duì)基于FPGA的電子系統(tǒng)采取容錯(cuò)措施以防止此類故障的出現(xiàn)非常重要。通過(guò)對(duì)敏感電路使用三模冗余( TMR)方法并利用FPGA 的動(dòng)態(tài)可重構(gòu)特性,可以有效的增強(qiáng)FPGA 的抗單粒子性能,解決FPGA對(duì)因空間粒子輻射而形成的軟故障。

2017-11-18 11:40:02 10826

10826

針對(duì)多控制器軟件定義網(wǎng)絡(luò)( SDN)中交換機(jī)遷移策略遷移代價(jià)衡量單一,不能適應(yīng)交換機(jī)流量的變化的情況,提出基于改進(jìn)引力搜索算法的交換機(jī)遷移策略(IGS-SMS)。在決策階段,應(yīng)用基于模糊滿意度

2017-12-03 11:10:07 0

0 基于異步電機(jī)矢量控制弱磁方法, 探討了傳統(tǒng) 1/ :r 方法、考慮轉(zhuǎn)矩電流分量改進(jìn)型的 1/ :r弱磁方法和基于電壓控制策略的轉(zhuǎn)矩最大化弱磁方案

2017-12-04 11:53:22 11

11 離開(kāi)原屬社區(qū)后模塊度增益的計(jì)算方法,完善了該領(lǐng)域的理論研究。針對(duì)魯汶算法對(duì)存儲(chǔ)空間需求高的缺點(diǎn),提出了基于孤立節(jié)點(diǎn)分離策略的改進(jìn)魯汶算法,該算法在每次迭代中將輸入網(wǎng)絡(luò)的孤立節(jié)點(diǎn)提前分離出去,只令其中的連通節(jié)

2017-12-04 16:48:16 0

0 針對(duì)經(jīng)典快速非支配排序遺傳算法(NSGA-Ⅱ)中基于擁擠距離的種群多樣性保持策略不能客觀反映個(gè)體間真實(shí)擁擠程度的問(wèn)題,提出了一種基于自適應(yīng)混合非支配個(gè)體排序策略的改進(jìn)型NSGA-Ⅱ算法(NSGA-

2017-12-19 17:00:15 1

1 對(duì)Jacquin基本分形編碼方法進(jìn)行研究和改進(jìn),提出一種改進(jìn)的分形圖像編碼方法。通過(guò)對(duì)多幅圖像進(jìn)行實(shí)驗(yàn),本文的改進(jìn)方法在圖像壓縮時(shí)間、壓縮比以及峰值信噪比PSNR值上均有提高。

2017-12-20 13:56:20 2

2 針對(duì)狼群算法( WPA)存在的收斂速度慢、易陷入局部最優(yōu)、人工狼交互性不理想等不足,提出一種基于改進(jìn)搜索策略的狼群( MWPA)算法。對(duì)游走行為以及召喚行為引入交互策略,促使人工狼之間進(jìn)行信息交流

2018-01-09 14:08:42 3

3 具有Levy飛行特征的果蠅算法( LFOA)對(duì)RVM核參數(shù)進(jìn)行尋優(yōu),建立了LFOA-RVM分類模型。在適應(yīng)度函數(shù)的評(píng)判下,果蠅種群經(jīng)過(guò)多次迭代對(duì)指定范圍內(nèi)的核參數(shù)進(jìn)行全局搜索尋優(yōu),完成模型建立。四組UCI標(biāo)準(zhǔn)數(shù)據(jù)集的MATLAB仿真實(shí)驗(yàn)結(jié)果表明,改進(jìn)后的多分類決策策略和優(yōu)化方法有效、可靠

2018-01-17 17:54:36 0

0 ( SHEPWM)輸出開(kāi)關(guān)狀態(tài)產(chǎn)生的共模電壓幅值及其對(duì)中點(diǎn)電壓的影響,研究了SHEPWM方法的中點(diǎn)電壓自平衡特性,提出了一種改進(jìn)的SHEPWM控制策略。該控制策略在不影響消除線電壓特定諧波及保持中點(diǎn)電壓自平衡特性的前提下,能有效降低逆變

2018-03-28 14:21:17 3

3 這里將介紹另一款 定時(shí)器 TMR2 模塊,TMR2與前面介紹的TMR0和TMR1相比,最大的差別是只能工作于定時(shí)模式,因此稱它為“定時(shí)器TMR2”。

2018-06-24 16:52:00 5995

5995

FPGA設(shè)計(jì)中,層次結(jié)構(gòu)設(shè)計(jì)和復(fù)位策略影響著FPGA的時(shí)序。在高速設(shè)計(jì)時(shí),合理的層次結(jié)構(gòu)設(shè)計(jì)與正確的復(fù)位策略可以優(yōu)化時(shí)序,提高運(yùn)行頻率。

2019-02-15 15:15:53 849

849 本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA教程之FPGA系統(tǒng)設(shè)計(jì)的主要思路和方法初探資料說(shuō)明包括了:1.FPGA的適用領(lǐng)域及選型FPGA系統(tǒng)設(shè)計(jì)典型流程,2.FPGA邏輯設(shè)計(jì)方法 弓|入ASIC的設(shè)計(jì)方法,3.FPGA設(shè)計(jì)的常用技巧,4.FPGA系統(tǒng)設(shè)計(jì)中的對(duì)與錯(cuò)

2019-04-04 17:19:58 53

53 本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA教程之FPGA系統(tǒng)設(shè)計(jì)與應(yīng)用的詳細(xì)資料說(shuō)明包括了:1.Altera的FPGA體系結(jié)構(gòu)簡(jiǎn)介,2.Altera的FPGA選型策略,3.嵌入式邏輯分析工具SignalTAPII的使用4.基于CPLD的FPGA配置方法

2019-04-04 17:47:03 60

60 本文檔的詳細(xì)介紹的是FPGA設(shè)計(jì)有哪些良好的設(shè)計(jì)方法及誤區(qū)內(nèi)容包括了:1.FPGA的適用領(lǐng)域及選型,2.FPGA系統(tǒng)設(shè)計(jì)典型流程,3.FPGA邏輯設(shè)計(jì)良好設(shè)計(jì)方法一引入ASIC的設(shè)計(jì)方法,4.FPGA設(shè)計(jì)的常用技巧,5.FPGA系統(tǒng)設(shè)計(jì)中的誤區(qū)

2019-04-18 17:30:04 23

23 TMR2的寬度與TMR0一樣的也是8位,一般伴隨著CCP模塊和PWM功能一起出現(xiàn)。 8位寬度的TMR2定時(shí)器有一個(gè)前置預(yù)分頻器和后置預(yù)分頻器,同時(shí)還有一個(gè)周期控制寄存器與它配合一起實(shí)現(xiàn)針對(duì)單片機(jī)指令

2019-09-24 17:18:00 0

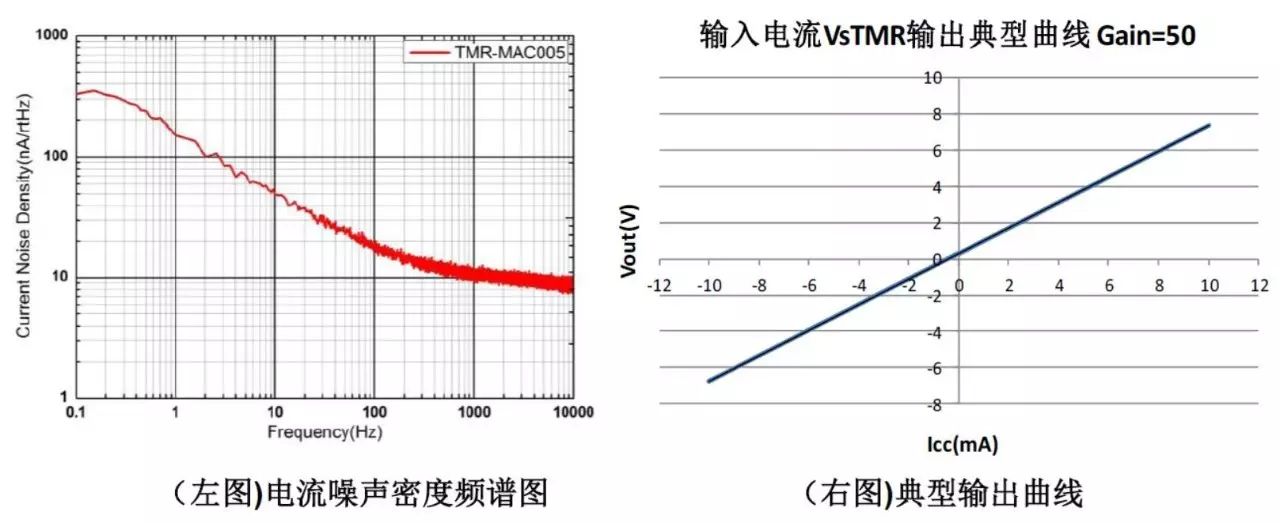

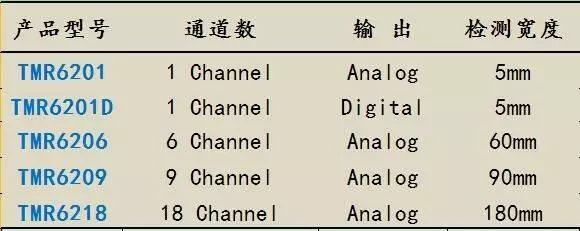

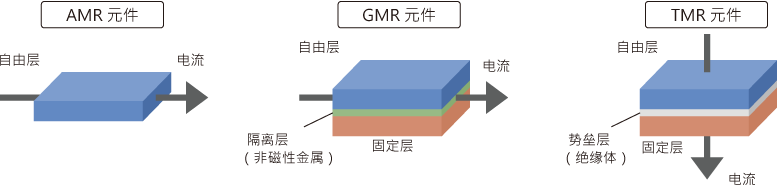

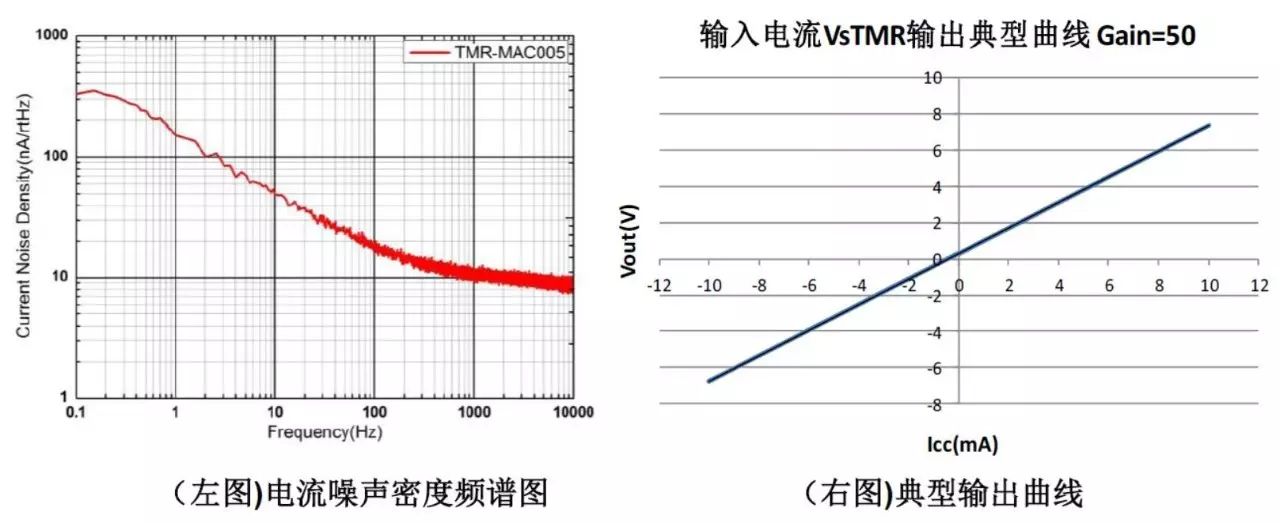

0 專業(yè)的隧道磁阻(TMR)傳感器領(lǐng)先供應(yīng)商江蘇多維科技有限公司(MultiDimension Technology Co., Ltd., MDT)推出正弦/余弦輸出信號(hào)的高精度TMR齒輪編碼器TMR-GE-A系列。

2019-10-28 08:35:43 3176

3176 MDT是首家TMR傳感器的批量供應(yīng)商,可在多個(gè)產(chǎn)品系列供貨,包括TMR磁開(kāi)關(guān)、TMR/AMR線性磁場(chǎng)傳感器、TMR/AMR角度傳感器、TMR齒輪傳感器、TMR磁圖像傳感器、USB磁力計(jì)、TMR旋轉(zhuǎn)

2019-10-28 09:35:59 4217

4217

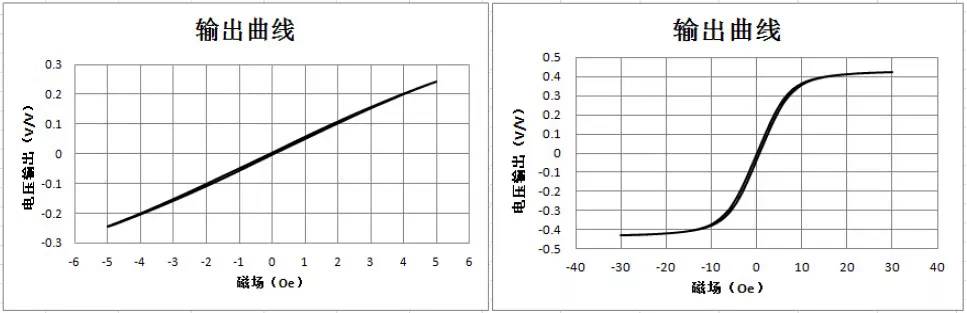

TMR3101是一款非接觸式磁阻絕對(duì)位置編碼器,可用于精確測(cè)量單圈360o內(nèi)的任意角度,也可輸出脈沖信號(hào),作為增量式編碼器使用。TMR3101非接觸式磁絕對(duì)位置編碼器由隧道磁電阻(TMR)角度傳感器和數(shù)字處理芯片集成而成。配合徑向充磁的磁鐵,可完成360°角度測(cè)量和轉(zhuǎn)速測(cè)量。

2019-10-28 10:20:12 4179

4179

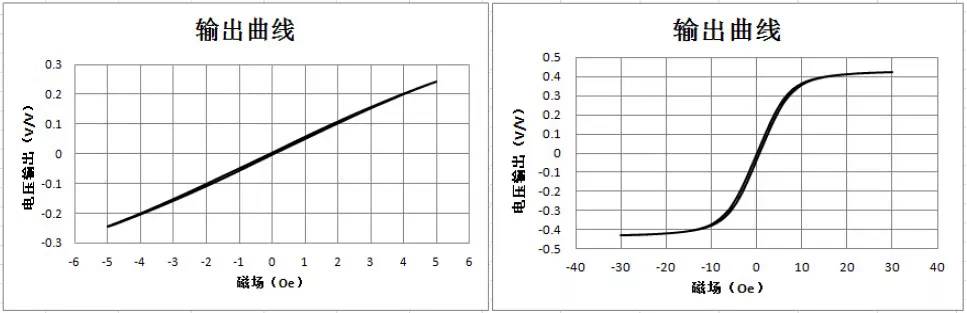

TMR2905采用了一個(gè)獨(dú)特的推挽式惠斯通全橋結(jié)構(gòu)設(shè)計(jì),包含四個(gè)非屏蔽高靈敏度TMR傳感器元件。當(dāng)外加磁場(chǎng)沿平行于傳感器敏感方向變化時(shí),惠斯通全橋提供差分電壓輸出,并且該輸出具有良好的溫度穩(wěn)定性。TMR2905性能優(yōu)越,采用的封裝形式: SOP8(6mm x 5mm x 1.5mm)。

2019-10-28 14:12:40 5113

5113

專業(yè)的隧道磁阻 (TMR) 磁傳感器領(lǐng)先供應(yīng)商江蘇多維科技有限公司 (MultiDimension Technology Co., Ltd., MDT) 日前發(fā)布了三款雙穩(wěn)態(tài) TMR 磁開(kāi)關(guān)傳感器

2019-12-17 09:42:37 2468

2468 三模冗余(TMR)技術(shù)是FPGA設(shè)計(jì)中最著名的錯(cuò)誤掩蔽和單事件效應(yīng)(SEE)保護(hù)技術(shù)之一。這些FPGA設(shè)計(jì)大多采用硬件描述語(yǔ)言,如Verilog和VHDL。TMR技術(shù)包括設(shè)計(jì)模塊的三倍化和為每個(gè)輸出

2020-04-16 08:00:00 3

3 引言:FPGA作為數(shù)字電路三大基石之一,其選型的好壞決定了產(chǎn)品的成本、項(xiàng)目研發(fā)效率、產(chǎn)品上市時(shí)間、產(chǎn)品生命周期等諸多方面。FPGA選型策略可以分為FPGA廠商選擇、FPGA器件家族選擇、器件型號(hào)選擇

2021-03-22 09:25:18 6517

6517 針對(duì)樽海鞘群算法( Salp SwarmΔ lgorithm,SSΔ)在尋優(yōu)過(guò)程中存在的收斂速度較慢、容易陷入局部最優(yōu)的缺點(diǎn),提出了一種改進(jìn)的采用萊維飛行策略的條件化更新的樽海鞘群算法( Levy

2021-05-18 15:36:51 9

9 一種基于自適應(yīng)鄰域策略的改進(jìn)算法

2021-06-27 15:27:41 10

10 容器云中基于改進(jìn)遺傳算法的資源分配策略綜述

2021-06-29 16:02:45 5

5 FPGA_ASIC-一種改進(jìn)的2D-DCT的FPGA實(shí)現(xiàn)(核達(dá)中遠(yuǎn)通電源技術(shù)有限公司招聘文員嗎?)-該文檔為FPGA_ASIC-一種改進(jìn)的2D-DCT的FPGA實(shí)現(xiàn)講解文檔,是一份很不錯(cuò)的參考資料,具有較高參考價(jià)值,感興趣的可以下載看看………………

2021-09-16 10:35:54 4

4 TMR2的寬度與TMR0一樣的也是8位,一般伴隨著CCP模塊和PWM功能一起出現(xiàn)。 8位寬度的TMR2定時(shí)器有一個(gè)前置預(yù)分頻器和后置預(yù)分頻器,同時(shí)還有一個(gè)周期控制寄存器與它配合一起實(shí)現(xiàn)針對(duì)

2021-11-16 12:21:02 1

1 一、結(jié)構(gòu)1、TMR1可以作為通用的定時(shí)器和計(jì)數(shù)器,也可以利用內(nèi)置的低頻時(shí)基振蕩器實(shí)現(xiàn)實(shí)時(shí)時(shí)鐘RTC功能;通過(guò)TMR1與CCP模塊的配合使用,TMR1還可以實(shí)現(xiàn)輸入捕捉和輸出比較功能。TMR

2021-11-16 17:36:05 1

1 趁著一股熱情 來(lái)學(xué)習(xí)tmr模塊, 找到官方的api文檔, 網(wǎng)址:https://nodemcu.readthedocs.io/en/master/en/modules/tmr/?全是鳥(niǎo)語(yǔ)

2021-12-17 17:59:18 10

10 SD-WAN 引入了以前的傳統(tǒng)網(wǎng)絡(luò)技術(shù)不具備的新安全選項(xiàng),使管理和保護(hù)網(wǎng)絡(luò)流量變得更加容易。數(shù)據(jù)泄露和安全威脅是 IT 領(lǐng)導(dǎo)者最關(guān)心的問(wèn)題,但雇用熟練的安全專業(yè)人員比以往任何時(shí)候都更加困難。這促使組織尋找更輕松地改進(jìn)其安全策略的方法。一種選擇是實(shí)施軟件定義的 WAN( SD-WAN )。

2022-09-28 12:16:53 492

492 APM32F003X6_TMR_從Bootloader跳轉(zhuǎn)到APP,TMR4

2022-11-09 21:03:21 0

0 APM32F103C8T6_TMR1_TMR1輸出異常

2022-11-09 21:03:23 0

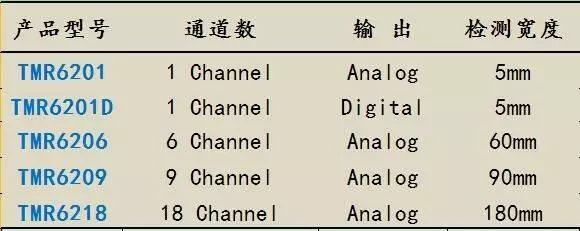

0 多維科技TMR3103和TMR3106角度編碼器芯片產(chǎn)品適用于BLDC無(wú)刷電機(jī)位置檢測(cè)、轉(zhuǎn)速檢測(cè)、閉環(huán)步進(jìn)電機(jī)位置檢測(cè)及多種非接觸式角度檢測(cè)等應(yīng)用。

2023-07-03 14:50:46 1000

1000

電子發(fā)燒友網(wǎng)站提供《基于AoDV改進(jìn)的水下傳感器網(wǎng)絡(luò)多徑路由策略.pdf》資料免費(fèi)下載

2023-10-08 14:38:41 0

0 2023年12月21日消息,專注于隧道磁阻(TMR)技術(shù)的磁傳感器制造商江蘇多維科技有限公司基于高靈敏度TMR技術(shù)推出了TMR3016和TMR3017角度傳感器芯片產(chǎn)品,并已開(kāi)始量產(chǎn)。該芯片采用

2023-12-22 11:24:38 601

601

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論