引言

VGA(視頻圖形陣列)作為一種標準的顯示接口得到廣泛的應用。利用FPGA 芯片和EDA 設計方法,可以因地制宜,根據用戶的特定需要,設計出針對性強的VGA 顯示控制器,不僅能夠大大降低成本,還可以滿足生產實踐中不斷變化的用戶需要,產品的升級換代方便迅速。

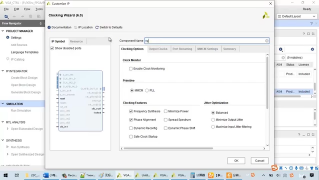

在本設計中采用了Altera 公司的EDA 軟件工具Quartus II ,并以ACEX系列FPGA 的器件為主實現硬件平臺的設計。

1 基于FPGA 的VGA 圖形控制器系統框圖

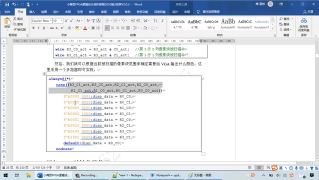

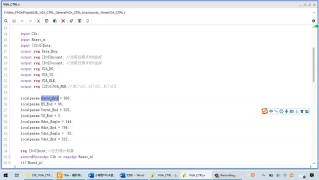

根據自頂向下的程序設計思想,采用模塊化設計,我們對VGA 圖形控制器進行功能分離并按層次設計。利用VHDL 硬件描述語言逐一對每個功能模塊進行描述,并逐個通過編譯仿真,最后下載到硬件平臺調試。本設計的VGA 控制器主要由以下模塊組成:VGA 時序控制模塊、分頻模塊、漢字顯示模塊、圖像控制模塊、ROM讀取模塊等,如圖1 所示。

圖1 基于FPGA 的VGA 圖形控制系統框圖

2 主要功能模塊設計

2. 1 VGA 時序控制模塊

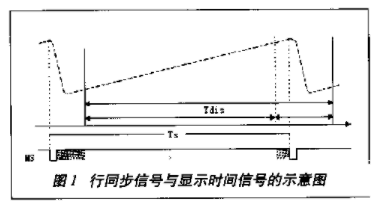

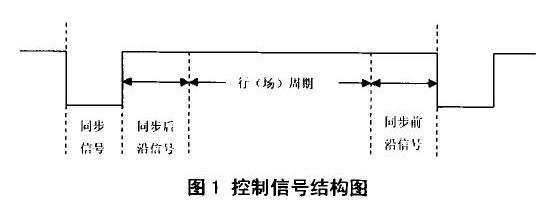

VGA 時序控制模塊是整個顯示控制器的關鍵部分,最終的輸出信號行、場同步信號必須嚴格按照VGA 時序標準產生相應的脈沖信號。對于普通的VGA 顯示器, 其引出線共含5 個信號: G,R ,B (3 基色信號) ,HS(行同步信號) ,VS(場同步信號) 。在5個信號時序驅動時,VGA 顯示器要嚴格遵循“VGA工業標準”, 即640 Hz ×480 Hz ×60Hz 模式。

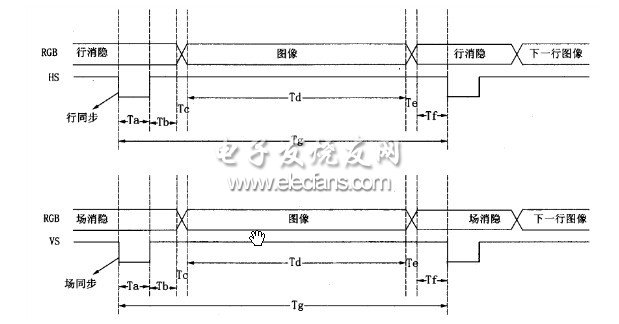

對于VGA 顯示器,每個像素點的輸出頻率為25. 175MHz ,因此采用50MHz 的時鐘信號,經過二分頻模塊,得到25MHz 的輸入時鐘脈沖。依據VGA 時序標準,行同步信號HS ,行周期為31. 78μs ,每顯示行包括800 點,其中640 點為有效顯示區,160 點為行消隱區,每行有一個脈沖,該脈沖的低電平寬度為3. 81μs (即96 個脈沖) ; 場同步信號VS ,場周期為16.683ms ,每場有525 行,其中480 行為有效顯示行,45 行為場消隱區,每場有一個脈沖,該脈沖的低電平寬度為63μs (2 行)。

圖2 VGA 行掃描、場掃描的時序圖

依據這個標準,把輸入的25MHz 時鐘脈沖按照對應的像素點數和掃描行數進行分頻處理,可以得到最后符合時序要求的行頻率和刷新頻率。

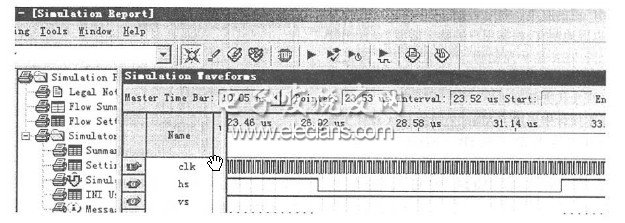

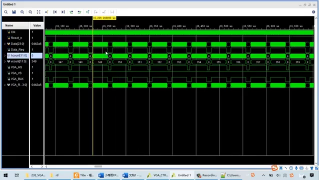

利用Altera 公司的QuartusII 軟件對VHDL 語言描述的VGA 時序控制模塊進行編譯、仿真,可得到行同步信號HS , 場同步信號VS 的時序仿真波形,如圖3 所示。

圖3 時鐘信號仿真圖

由仿真結果波形可以看到,行同步信號的時鐘周期約為31. 9μs ,場同步信號的時鐘周期約為16。

6ms ,達到了VGA 標準時序的要求,可以為CRT 顯示器提供準確的行場同步信號。

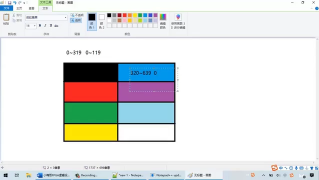

在硬件系統上,通過彩條圖案的生成驗證了時序生成的正確性,可產生豎彩條、橫彩條、棋盤格等多種彩條模式。

2. 2 漢字顯示模塊

漢字生成模塊可實現在顯示器上顯示漢字、字符等。字模信息可以利用字模提取軟件來獲得,得到了漢字的字模信息后,可以通過屏幕上的橫坐標和縱坐標按照字模信息定義像素的顏色,這樣就可以顯示任何字體、任何點陣的漢字,并根據需要決定漢字在屏幕上的位置。至于英文以及其他任何符號的顯示原理與漢字顯示的原理一樣。

顯示器上顯示的漢字精細度取決于顯示屏所分網格的數目多少。設計者可以根據不同要求設定不同的網格數目。Altera 公司的FPGA 器件內均內置— 26 —了嵌入式陣列塊EAB ,通過調用其中的LPM ROM模塊,可任意設置參數,構成內置的ROM存儲器,存放所必要的字模信息,能與漢字顯示模塊配合,顯示出任意漢字。

2. 3 圖形顯示模塊

2. 3. 1 ROM讀取控制模塊

當VGA 顯示器要顯示一幀圖像,需要比較大的數據量,FPGA 芯片內置的ROM 存儲器難以滿足這么大的數據存儲要求,必須把圖像數據存入外部的存儲器中。

外部存儲器可以有多種選擇, 如ROM,、雙口RAM、甚至SDRAM 等,采用何種存儲器將最終決定讀取控制模塊的數據讀取方式。如ROM 可用直接產生地址信號的方式對芯片進行訪問,而SDRAM常常利用DMA 控制方式配合CPU 進行讀寫操作。

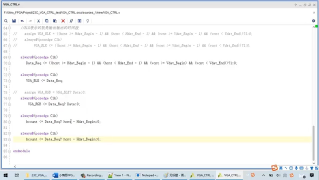

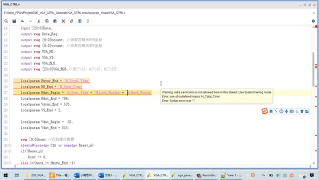

這里采用型號為28C040 的4M EEPROM 外部存儲器,可以在單片內存儲整屏圖像,同時考慮到存儲空間的大小,本設計采用每個像素的顏色位深為3 位,共可顯示8 種顏色。此模塊最終仿真結果如圖4所示。

圖4 地址信號仿真圖

由圖中的仿真結果可以看到,地址信號每兩個時鐘脈沖加1 ,而每兩個時鐘脈沖代表掃描過一個像素點,由此可驗證以上設計的正確性。

2. 3. 2 BMP 圖像數據存入ROM

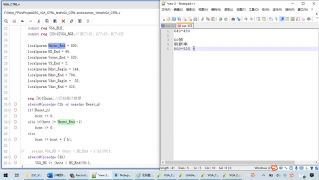

要把一幅圖像的數據寫入ROM,首先必須解決的就是寫入文件的格式問題。一般的方法是通過編程器把Intel Hex ,或者二進制文件。 bin 逐字節寫入ROM。而圖像都具有固定的格式,如BMP , JPEG,GIF 等,其中的BMP 格式圖像是一種很常見的圖像格式,沒有經過壓縮處理,且文件結構相對簡單,易于處理,在本設計中采用了BMP 圖像作為研究對象。將BMP 文件直接轉化為Intel Hex 文件比較困難,因此可先將BMP 格式文件轉化為mif 格式文件,再由Quartus II 直接將mif 文件轉化為Intel Hex 文件,最后再將圖像數據燒寫入ROM中。由于沒有現成的轉換程序,選擇Visual C ++ 自行編寫轉換程序。

Memory Initialization File ( . mif) 格式是Quartus II中ROM的初始化數據文件格式,它記錄方式比較簡單,其中地址和數據都可為十進制或十六進制,冒號左邊是地址值,右邊是對應的數據,并以分號結尾。

相對mif 文件,BMP 格式的位圖文件稍顯復雜,它包括位圖文件頭結構、位圖信息頭結構、位圖顏色表和位圖像素數據四部分。位圖文件的保存順序如下:位圖文件頭→位圖信息頭→位圖顏色表→位圖像素數據。處理位圖時要根據文件的這些結構得到位圖文件大小、位圖的寬、高、實現調色板、得到位圖像素值等等。以目前應用較為廣泛的24 位真彩色圖像為例,其特點是:24 位真彩色圖像存儲文件中不帶有圖像顏色表;圖像中每一像素由RGB 三個分量組成,每個分量各8 位,每個像素需24 位;顏色分量值f red , f green , f blue 的取值范圍都為0 ~ 255。

對于用到顏色表的位圖,圖像數據就是該像素顏色在調色板中的索引值。對于真彩色圖像,圖像數據就是實際的R , G ,B 值,一個像素是由3 個字節24位組成, 前8 位表示B , 中間8 位表示G , 后8 位表示R 。

由于硬件存儲資源的限制,取圖像像素的位深為3 ,總共可顯示8 種顏色。首先把BMP 圖像數據的RGB 分量分別讀出,并且各取1 位,即顏色分量值只能取值‘0’或‘1’。針對24 位真彩色圖像的特點,可對顏色分量值進行粗略取樣,當顏色分量值f red >127 ,取f red = 1 ;反之取f red = 0。同理,顏色分量值f green , f blue 可取得相應的0 ,1二值。

最后在利用Visual C ++ 編寫轉換程序時應注意,BMP 文件是從左至右,從下至上排列的,即讀文件時,最先讀到的是圖像最下面一行的左邊第一個像素,最后讀到的是最上面一行的最右邊一個像素,這與VGA 顯示器的掃描順序恰好相反。

3 結論

經過硬件平臺的驗證,基于FPGA 的VGA 圖形顯示器已達到設計要求,可實現彩條、漢字、小圖像和大圖像的顯示,并可實現FPGA 器件對顯示器的單片控制。

由于受到存儲器件容量的限制,本設計中存儲的圖像數據所采用的像素位深為3 位,共可顯示8種顏色。在實際應用中,可以使用更大的存儲器,最終實現256 色圖像,乃至真彩色圖像的顯示。在此設計基礎上,通過使用SDRAM 等外部存儲器,利用DMA 控制方式,并且配合Altera 的nios 嵌入式軟核CPU ,可以在SOPC 開發平臺上最終實現兼容SVGA ,TVGA 標準等的更復雜顯示控制器。

電子發燒友App

電子發燒友App

評論