同步電路的速度是指同步系統(tǒng)時鐘的速度,同步時鐘愈快,電路處理數(shù)據(jù)的時間間隔越短,電路在單位時間內(nèi)處理的數(shù)據(jù)量就愈大。假設(shè)Tco是觸發(fā)器的輸入數(shù)據(jù) 被時鐘打入到觸發(fā)器到數(shù)據(jù)到達(dá)觸發(fā)器輸出端的延時時間;Tdelay是組合邏輯的延時;Tsetup是D觸發(fā)器的建立時間。假設(shè)數(shù)據(jù)已被時鐘打入D觸發(fā) 器,那么數(shù)據(jù)到達(dá)第一個觸發(fā)器的Q輸出端需要的延時時間是Tco,經(jīng)過組合邏輯的延時時間為Tdelay,然后到達(dá)第二個觸發(fā)器的D端,要希望時鐘能在第 二個觸發(fā)器再次被穩(wěn)定地打入觸發(fā)器,則時鐘的延遲必須大于Tco+Tdelay+Tsetup,也就是說最小的時鐘周期Tmin =Tco+Tdelay+Tsetup,即最快的時鐘頻率Fmax =1/Tmin。FPGA開發(fā)軟件也是通過這種方法來計算系統(tǒng)最高運(yùn)行速度Fmax。因為Tco和Tsetup是由具體的器件工藝決定的,故設(shè)計電路時只 能改變組合邏輯的延遲時間Tdelay,所以說縮短觸發(fā)器間組合邏輯的延時時間是提高同步電路速度的關(guān)鍵所在。由于一般同步電路都大于一級鎖存,而要使電 路穩(wěn)定工作,時鐘周期必須滿足最大延時要求。故只有縮短最長延時路徑,才能提高電路的工作頻率。可以將較大的組合邏輯分解為較小的N塊,通過適當(dāng)?shù)姆椒ㄆ?均分配組合邏輯,然后在中間插入觸發(fā)器,并和原觸發(fā)器使用相同的時鐘,就可以避免在兩個觸發(fā)器之間出現(xiàn)過大的延時,消除速度瓶頸,這樣可以提高電路的工作 頻率。這就是所謂"流水線"技術(shù)的基本設(shè)計思想,即原設(shè)計速度受限部分用一個時鐘周期實現(xiàn),采用流水線技術(shù)插入觸發(fā)器后,可用N個時鐘周期實現(xiàn),因此系統(tǒng) 的工作速度可以加快,吞吐量加大。注意,流水線設(shè)計會在原數(shù)據(jù)通路上加入延時,另外硬件面積也會稍有增加。

8:時序約束的概念和基本策略?

時序約束主要包括周期約束,偏移約束,靜態(tài)時序路徑約束三種。通過附加時序約束可以綜合布線工具調(diào)整映射和布局布線,是設(shè)計達(dá)到時序要求。

附加時序約束的一般策略是先附加全局約束,然后對快速和慢速例外路徑附加專門約束。附加全局約束時,首先定義設(shè)計的所有時鐘,對各時鐘域內(nèi)的同步元件進(jìn)行分 組,對分組附加周期約束,然后對FPGA/CPLD輸入輸出PAD附加偏移約束、對全組合邏輯的PAD TO PAD路徑附加約束。附加專門約束時,首先約束分組之間的路徑,然后約束快、慢速例外路徑和多周期路徑,以及其他特殊路徑。

9:附加約束的作用?

作用:1:提高設(shè)計的工作頻率(減少了邏輯和布線延時);2:獲得正確的時序分析報告;(靜態(tài)時序分析工具以約束作為判斷時序是否滿足設(shè)計要求的標(biāo)準(zhǔn),因 此要求設(shè)計者正確輸入約束,以便靜態(tài)時序分析工具可以正確的輸出時序報告)3:指定FPGA/CPLD的電氣標(biāo)準(zhǔn)和引腳位置。

10:FPGA設(shè)計工程師努力的方向:

SOPC, 高速串行I/O,低功耗,可靠性,可測試性和設(shè)計驗證流程的優(yōu)化等方面。隨著芯片工藝的提高,芯片容量、集成度都在增加,F(xiàn)PGA設(shè)計也朝著高速、高度集 成、低功耗、高可靠性、高可測、可驗證性發(fā)展。芯片可測、可驗證,正在成為復(fù)雜設(shè)計所必備的條件,盡量在上板之前查出bug,將發(fā)現(xiàn)bug的時間提前,這 也是一些公司花大力氣設(shè)計仿真平臺的原因。另外隨著單板功能的提高、成本的壓力,低功耗也逐漸進(jìn)入FPGA設(shè)計者的考慮范圍,完成相同的功能下,考慮如何 能夠使芯片的功耗最低,據(jù)說altera、xilinx都在根據(jù)自己的芯片特點(diǎn)整理如何降低功耗的文檔。高速串行IO的應(yīng)用,也豐富了FPGA的應(yīng)用范 圍,象xilinx的v2pro中的高速鏈路也逐漸被應(yīng)用。 總之,學(xué)無止境,當(dāng)掌握一定概念、方法之后,就要開始考慮FPGA其它方面的問題了。

11:對于多位的異步信號如何進(jìn)行同步?

對以一位的異步信號可以使用“一位同步器進(jìn)行同步”,而對于多位的異步信號,可以采用如下方法:1:可以采用保持寄存器加握手信號的方法(多數(shù)據(jù),控制, 地址);2:特殊的具體應(yīng)用電路結(jié)構(gòu),根據(jù)應(yīng)用的不同而不同 ;3:異步FIFO。(最常用的緩存單元是DPRAM)

12:FPGA和CPLD的區(qū)別?

ASIC:專用集成電路,它是面向?qū)iT用途的電路,專門為一個用戶設(shè)計和制造的。根據(jù)一個用戶的特定要求,能以低研制成本,短、交貨周期供貨的全定制,半定制集成電路。與門陣列等其它ASIC(ApplicaTIon Specific IC)相比,它們又具有設(shè)計開發(fā)周期短、設(shè)計制造成本低、開發(fā)工具先進(jìn)、標(biāo)準(zhǔn)產(chǎn)品無需測試、質(zhì)量穩(wěn)定以及可實時在線檢驗等優(yōu)點(diǎn)。

CPLD FPGA

內(nèi)部結(jié)構(gòu) Product-term Look-up Table

程序存儲 內(nèi)部EEPROM SRAM,外掛EEPROM

資源類型 組合電路資源豐富 觸發(fā)器資源豐富

集成度 低 高

使用場合 完成控制邏輯 能完成比較復(fù)雜的算法

速度 慢 快

其他資源 - PLL、RAM和乘法器等

保密性 可加密 一般不能保密

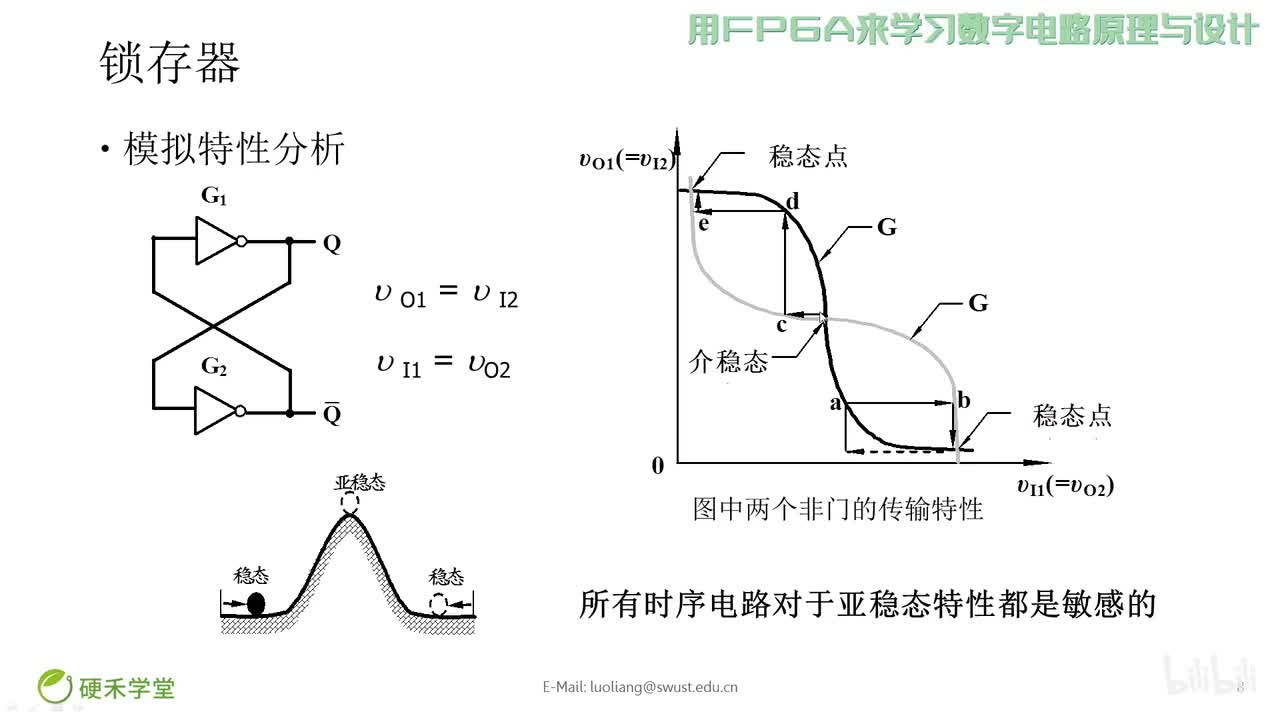

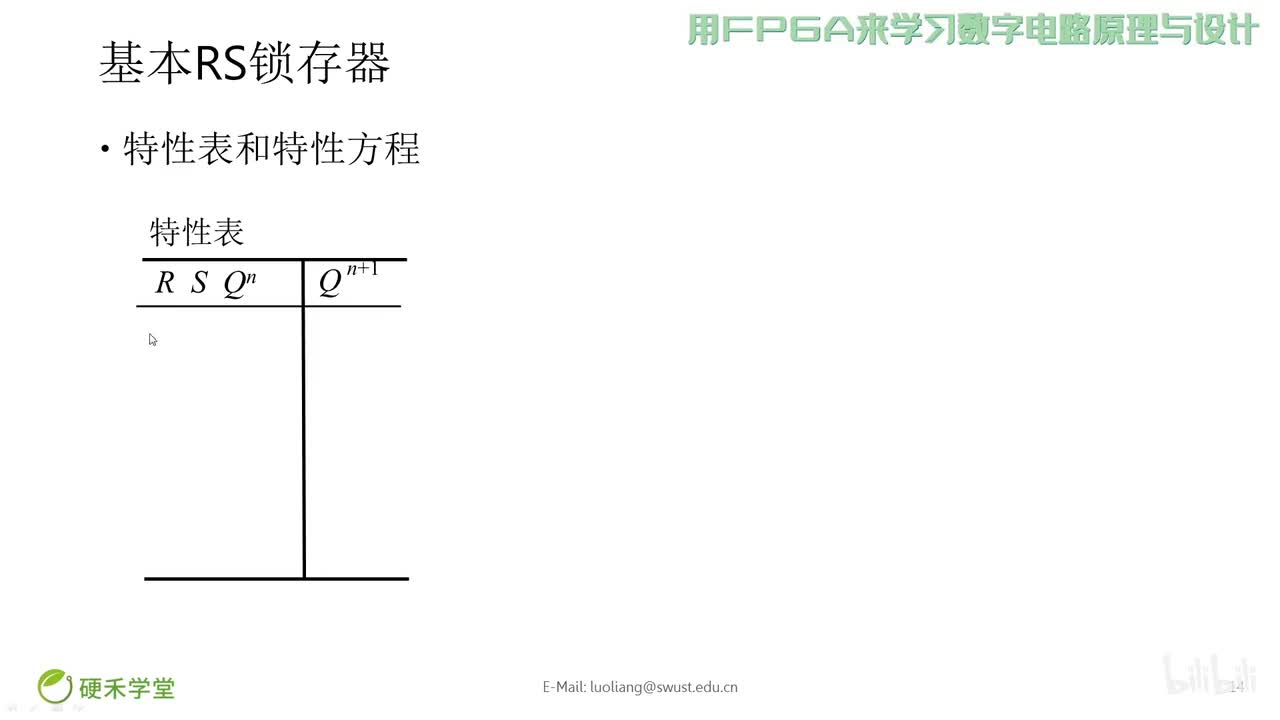

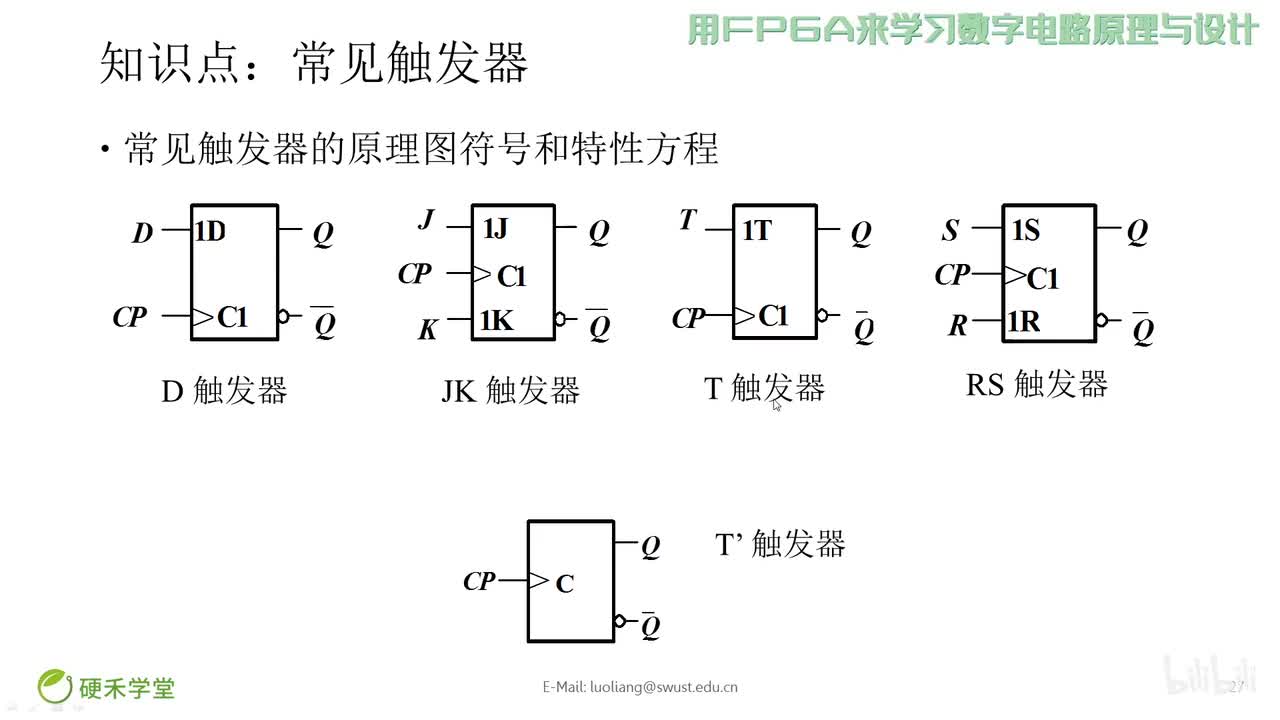

13:鎖存器(latch)和觸發(fā)器(flip-flop)區(qū)別?

電平敏感的存儲期間稱為鎖存器。可分為高電平鎖存器和低電平鎖存器,用于不同時鐘之間的信號同步。

有交叉耦合的門構(gòu)成的雙穩(wěn)態(tài)的存儲原件稱為觸發(fā)器。分為上升沿觸發(fā)和下降沿觸發(fā)。可以認(rèn)為是兩個不同電平敏感的鎖存器串連而成。前一個鎖存器決定了觸發(fā)器的建立時間,后一個鎖存器則決定了保持時間。

14:FPGA芯片內(nèi)有哪兩種存儲器資源?

FPGA芯片內(nèi)有兩種存儲器資源:一種叫block ram,另一種是由LUT配置成的內(nèi)部存儲器(也就是分布式ram)。Block ram由一定數(shù)量固定大小的存儲塊構(gòu)成的,使用BLOCK RAM資源不占用額外的邏輯資源,并且速度快。但是使用的時候消耗的BLOCK RAM資源是其塊大小的整數(shù)倍。

15:什么是時鐘抖動?

時鐘抖動是指芯片的某一個給定點(diǎn)上時鐘周期發(fā)生暫時性變化,也就是說時鐘周期在不同的周期上可能加長或縮短。它是一個平均值為0的平均變量。

16:FPGA設(shè)計中對時鐘的使用?(例如分頻等)

FPGA芯片有固定的時鐘路由,這些路由能有減少時鐘抖動和偏差。需要對時鐘進(jìn)行相位移動或變頻的時候,一般不允許對時鐘進(jìn)行邏輯操作,這樣不僅會增加時 鐘的偏差和抖動,還會使時鐘帶上毛刺。一般的處理方法是采用FPGA芯片自帶的時鐘管理器如PLL,DLL或DCM,或者把邏輯轉(zhuǎn)換到觸發(fā)器的D輸入(這 些也是對時鐘邏輯操作的替代方案)。

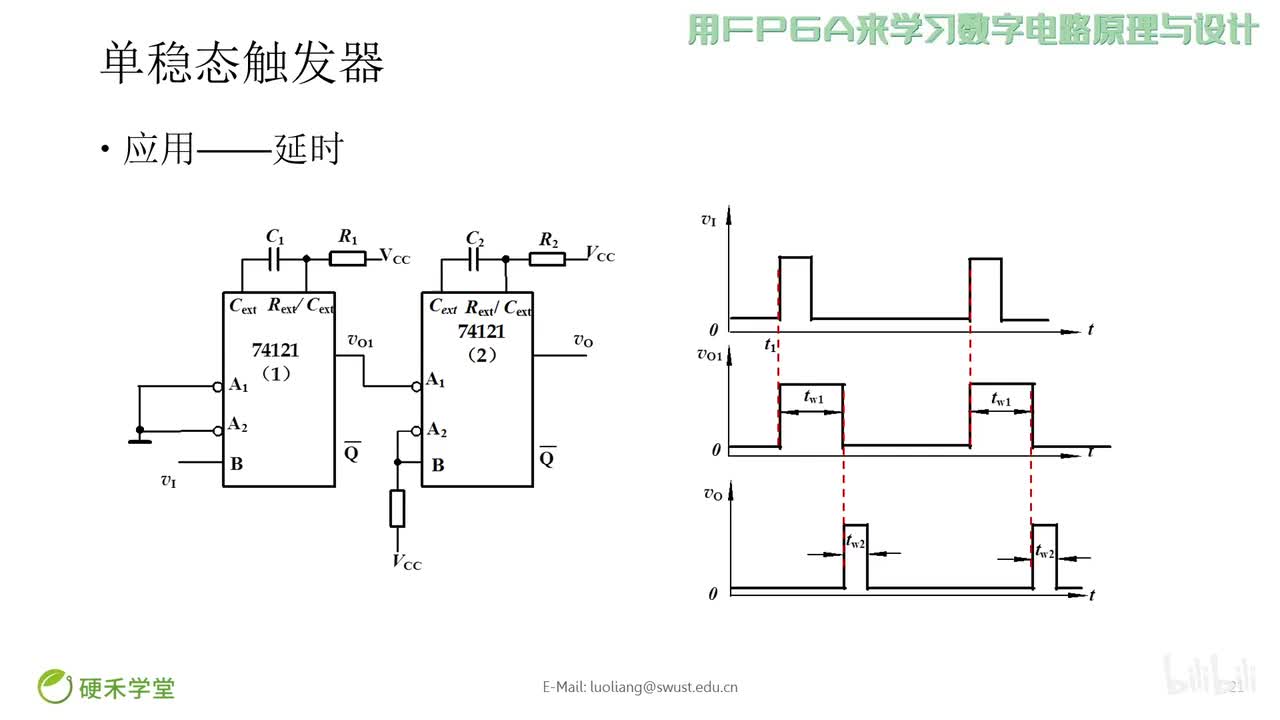

17:FPGA設(shè)計中如何實現(xiàn)同步時序電路的延時?

首先說說異步電路的延時實現(xiàn):異步電路一半是通過加buffer、兩級與非門等(我還沒用過所以也不是很清楚),但這是不適合同步電路實現(xiàn)延時的。在同步 電路中,對于比較大的和特殊要求的延時,一半通過高速時鐘產(chǎn)生計數(shù)器,通過計數(shù)器來控制延時;對于比較小的延時,可以通過觸發(fā)器打一拍,不過這樣只能延遲 一個時鐘周期。

18:FPGA中可以綜合實現(xiàn)為RAM/ROM/CAM的三種資源及其注意事項?

三種資源:block ram;觸發(fā)器(FF),查找表(LUT);

注意事項:1:在生成RAM等存儲單元時,應(yīng)該首選block ram 資源;其原因有二:第一:使用block ram等資源,可以節(jié)約更多的FF和4-LUT等底層可編程單元。使用block ram可以說是“不用白不用”,是最大程度發(fā)揮器件效能,節(jié)約成本的一種體現(xiàn);第二:block ram是一種可以配置的硬件結(jié)構(gòu),其可靠性和速度與用LUT和register構(gòu)建的存儲器更有優(yōu)勢。2:弄清FPGA的硬件結(jié)構(gòu),合理使用block ram資源;3:分析block ram容量,高效使用block ram資源;4:分布式ram資源(distribute ram)

19:Xilinx中與全局時鐘資源和DLL相關(guān)的硬件原語:

常用的與全局時鐘資源相關(guān)的Xilinx器件原語包括:IBUFG,IBUFGDS,BUFG,BUFGP,BUFGCE,BUFGMUX,BUFGDLL,DCM等。關(guān)于各個器件原語的解釋可以參考《FPGA設(shè)計指導(dǎo)準(zhǔn)則》p50部分。

電子發(fā)燒友App

電子發(fā)燒友App

評論