第一編 驗證的重要性

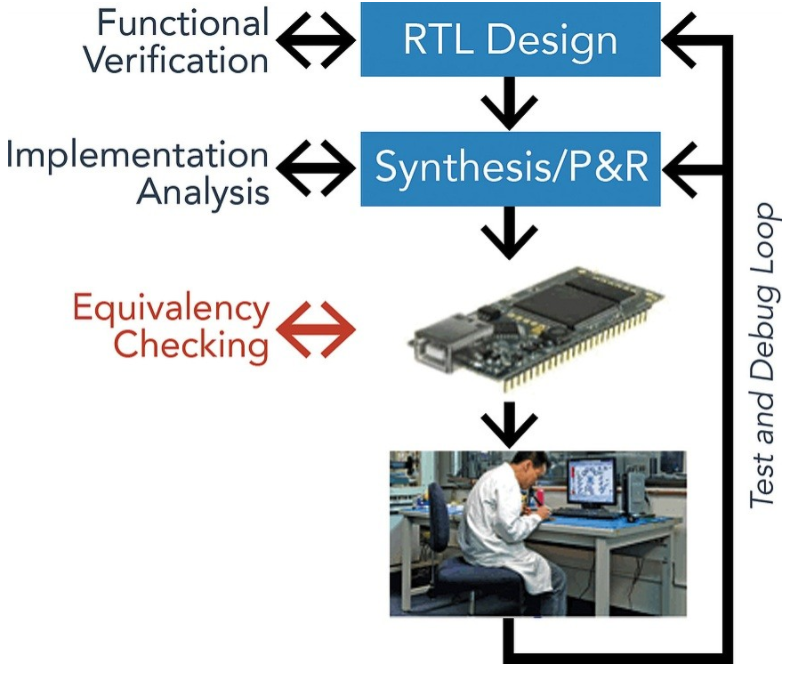

驗證,顧名思義就是通過仿真、時序分析、上板調(diào)試等手段檢驗設(shè)計正確性的過程,在FPGA/IC開發(fā)流程中,驗證主要包括功能驗證和時序驗證兩個部分。為了了解驗證的重要性,我們先來回顧一下FPGA開發(fā)的整個流程。FPGA開發(fā)流程和IC的開發(fā)流程相似,主要分為以下幾個部分:

1)設(shè)計輸入,利用HDL輸入工具、原理圖輸入工具或狀態(tài)機輸入工具等把所要設(shè)計的電路描述出來;

2)功能驗證,也就是前仿真,利用Modelsim、VCS等仿真工具對設(shè)計進(jìn)行仿真,檢驗設(shè)計的功能是否正確;常用的仿真工具有Model Tech公司的ModelSim,Synopsys公司的VCS,Cadence公司的NC-Verilog和NC-VHDL,Aldec公司的 Active HDL VHDL/Verilog HDL等。仿真過程能及時發(fā)現(xiàn)設(shè)計中的錯誤,加快了設(shè)計進(jìn)度,提高了設(shè)計的可*性。

3)綜合,綜合優(yōu)化是把HDL語言翻譯成最基本的與或非門的連接關(guān)系(網(wǎng)表),并根據(jù)要求(約束條件)優(yōu)化所生成的門級邏輯連接,輸出edf和edn等文件,導(dǎo)給CPLD/FPGA廠家的軟件進(jìn)行實現(xiàn)和布局布線。常用的專業(yè)綜合優(yōu)化工具有Synplicity公司的Synplify/Synplify Pro、Amplify等綜合工具,Synopsys公司的FPGA Compiler II綜合工具(Synopsys公司將停止發(fā)展FPGA Express軟件,而轉(zhuǎn)到FPGA Compiler II平臺),Exemplar Logic公司出品的LeonardoSpectrum等綜合工具。另外FPGA/CPLD廠商的集成開發(fā)環(huán)境也帶有一些綜合工具,如Xilinx ISE中的XST等。

4)布局布線,綜合的結(jié)果只是通用的門級網(wǎng)表,只是一些門與或非的邏輯關(guān)系,與芯片實際的配置情況還有差距。此時應(yīng)該使用FPGA/CPLD廠商提供的實現(xiàn)與布局布線工具,根據(jù)所選芯片的型號,進(jìn)行芯片內(nèi)部功能單元的實際連接與映射。這種實現(xiàn)與布局布線工具一般要選用所選器件的生產(chǎn)商開發(fā)的工具,因為只有生產(chǎn)者最了解器件內(nèi)部的結(jié)構(gòu),如在ISE的集成環(huán)境中完成實現(xiàn)與布局布線的工具是Flow Engine。

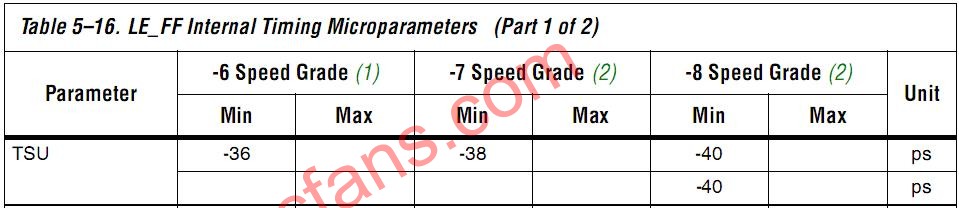

5)時序驗證,其目的是保證設(shè)計滿足時序要求,即setup/hold time符合要求,以便數(shù)據(jù)能被正確的采樣。時序驗證的主要方法包括STA(Static Timing Analysis)和后仿真。在后仿真中將布局布線的時延反標(biāo)到設(shè)計中去,使仿真既包含門延時,又包含線延時信息。這種后仿真是最準(zhǔn)確的仿真,能較好地反映芯片的實際工作情況。仿真工具與綜合前仿真工具相同。

6)生成并下載BIT或PROM文件,進(jìn)行板級調(diào)試。

在以上幾個主要開發(fā)步驟當(dāng)中,屬于驗證的有功能仿真和時序驗證兩個步驟,由于前仿真和后仿真涉及驗證環(huán)境的建立,需要耗費大量的時間,而在STA中對時序報告進(jìn)行分析也是一個非常復(fù)雜的事情,因此驗證在整個設(shè)計流程中占用了大量的時間,在復(fù)雜的FPGA/IC設(shè)計中,驗證所占的時間估計在60%~70%之間。相比較而言, FPGA設(shè)計流程的其他環(huán)節(jié)由于需要人為干預(yù)的東西比較少,例如綜合、布局布線等流程,基本所有的工作都由工具完成,設(shè)置好工具的參數(shù)之后,結(jié)果很快就可以出來,因此所花的時間精力要比驗證少的多。

一般而言,在驗證的幾個內(nèi)容中功能驗證最受重視,研究討論得最多,特別是現(xiàn)在FPGA/IC設(shè)計都朝向SOC(System On Chip,片上系統(tǒng))的方向發(fā)展,設(shè)計的復(fù)雜都大大提高,如何保證這些復(fù)雜系統(tǒng)的功能是正確的成了至關(guān)重要的問題。功能驗證對所有功能進(jìn)行充分的驗證,盡早地暴露問題,保證所有功能完全正確,滿足設(shè)計的需要。任何潛在的問題都會給后續(xù)工作作帶來難以極大的困難,而且由于問題發(fā)現(xiàn)得越遲,付出的代價也越大,這個代價是幾何級數(shù)增長的。這里將以功能驗證為主說明驗證方法、工具、驗證環(huán)境的建立、

做功能驗證時,需要建立驗證環(huán)境,以便對設(shè)計(DUT/DUV,Design Under Test/Verification)施加特定的輸入,然后對DUT的輸出進(jìn)行檢查,確實其是否正確。在實際驗證工作中,一般采用由TESTBENCH 和DUT(design under test)組成的Verification體系。

Verification體系是驗證系統(tǒng)普遍適用的模型,Testbench為DUT提供輸入,然后監(jiān)視輸出,從而判斷DUT工作是否正確。注意到這是一個封閉的系統(tǒng),沒有輸入也沒有輸出。驗證工作的難度在于確定應(yīng)該輸入何種激勵,相應(yīng)的正確的輸出應(yīng)該是怎樣的。

下一篇我們看個具體的例子,一起寫代碼和仿真。

第二篇 分析一個testbench

很多FPGA/IC開發(fā)工具都提供設(shè)計例子,方便使用者學(xué)習(xí)和練習(xí),例如,Xilinx ISE提供了很多設(shè)計實例,放在ISE5.X的安裝目錄下的ISEexamples目錄下,例如CDMA匹配濾波器、Johnson計數(shù)器、PN碼發(fā)生器、頻率計等,這些例子是經(jīng)驗豐富的工程師寫的,我們可以學(xué)到編程思想、代碼風(fēng)格等方面的知識和經(jīng)驗,這些東西可能從學(xué)校老師或一般書籍都學(xué)習(xí)不到。如果你用的不是Xilinx的FPGA,也就是說不使用ISE,那也沒關(guān)系,HDL代碼和testbench的設(shè)計思想和方法是一樣的,你照樣可以從中學(xué)到很多東西。下面以其中一個例子――同步FIFO為例,分析一下我們的第一個testbench,設(shè)計的源代碼可以在ISEexamples目錄下找到, Xilinx還提供了Application Note詳細(xì)介紹了該FIFO的細(xì)節(jié),下載的網(wǎng)址是http://www.xilinx.com/xapp/xapp131.pdf

1.511x8同步FIFO功能簡介

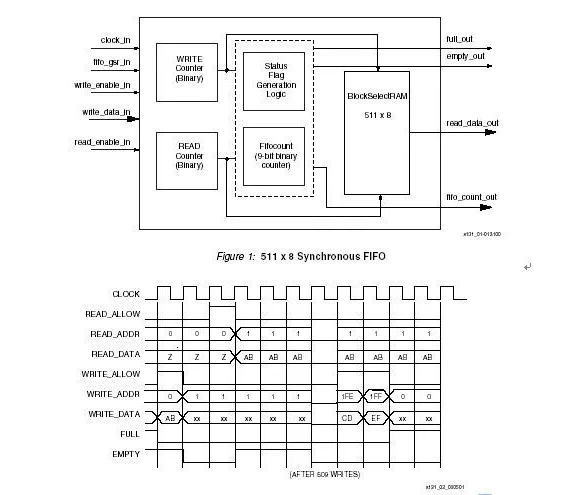

為了對這個511x8同步FIFO進(jìn)行功能驗證,首先要清楚它的功能,只有這樣才能知道需要驗證什么功能,以及如何進(jìn)行驗證,圖1為該同步FIFO的原理框圖。

與異步FIFO相比,同步FIFO的讀、寫時鐘是同一個時鐘,簡化了FIFO的設(shè)計,Empty和Full標(biāo)志的產(chǎn)生也比較容易,同步 FIFO內(nèi)部使用二進(jìn)制計數(shù)器記錄讀地址和寫地址。在異步FIFO中,由于讀寫使用不同的時鐘,也就是說設(shè)計存在兩個時鐘域,為了減少出現(xiàn)亞穩(wěn)態(tài)時產(chǎn)生的錯誤,記錄讀寫地址的計數(shù)器要使用格雷碼,Empty和Full標(biāo)志的產(chǎn)生也比較復(fù)雜。511x8同步FIFO(以下簡稱FIFO)的工作時序如圖2所示。

讀FIFO數(shù)據(jù)時,首先read_allow信號置高,時鐘上升沿到來時read_addr地址處的數(shù)據(jù)將出現(xiàn)在read_data處,同時read_addr加1。讓read_allow信號持續(xù)為高可以完成burst read操作。如果讀出的數(shù)據(jù)是FIFO的最后一個數(shù)據(jù),那么讀操作完成后Empty信號變高。Empty信號為高時讀出來的數(shù)據(jù)是無效的。

寫FIFO數(shù)據(jù)時,首先write_allow信號置高,同時準(zhǔn)備好輸入數(shù)據(jù)write_data,時鐘上升沿到來時,數(shù)據(jù)將寫入 write_addr所指向的地址中,同時write_addr加1。讓write_allow信號持續(xù)為高可以完成burst write操作。如果某一個時鐘上升沿時寫入第511個數(shù),那么下一個時鐘沿到來的時候Full信號變高,表示FIFO已經(jīng)寫滿。

我們再詳細(xì)分析FIFO的工作時序圖。在圖2中,開始時FIFO的讀寫指針均為0,Empty為高表示FIFO處于空的狀態(tài),然后 write_allow置高,時鐘上升沿到來時寫入第一個數(shù)據(jù),Empty變低;一個CLK之后,read_allow置高,時鐘上升沿到來時,讀出數(shù)據(jù),由于是最后一個數(shù)據(jù),所以Empty信號又變?yōu)橛行?高電平)。在時序圖的右半部分,寫入509個數(shù)據(jù)之后,再寫入兩個數(shù)據(jù),F(xiàn)ull信號變?yōu)橛行В硎綟IFO為滿。

這個FIFO還有一個名為fifo_count_out的輸出,從4’b0000~4’b1111,分別表示FIFO滿的程度從不足1/16到15/16,為某些應(yīng)用提供方便。

2.驗證

清楚FIFO的功能之后,我們就可以開始驗證工作了。驗證工作的第一步是整理出FIFO需要驗證的功能點,這些功能點一般直接來源于FIFO應(yīng)該具有的功能,或者來源于它的使用方法。FIFO需要驗證的功能點包括:

1)FIFO復(fù)位后,read_addr和write_addr為0,F(xiàn)ull為0,Empty為1。

2)讀FIFO數(shù)據(jù)時,read_allow信號必須置高,時鐘上升沿到來時read_addr地址處的數(shù)據(jù)將出現(xiàn)在read_data處,同時read_addr加1。

3)讀出FIFO的最后一個數(shù)據(jù)后,Empty信號變高。

4)寫FIFO數(shù)據(jù)時,write_allow信號必須置高,時鐘上升沿到來時,輸入數(shù)據(jù)write_data將寫入write_addr所指向的地址中,同時write_addr加1。

5)如果某一個時鐘上升沿時寫入第511個數(shù),那么下一個時鐘沿到來的時候Full信號變高,表示FIFO已經(jīng)寫滿。

6)fifo_count_out端能正確的指示FIFO滿的程度。

分析Xilinx提供的testbench可以為我們編寫自己的testbench提供很好的參考。FIFO的RTL代碼和 testbench代碼放在ISEexamplesfifo_ver_131和fifo_vhd_131下。以verilog代碼為例, fifo_ver_131中包括了兩個testbench文件,一個是功能仿真testbench文件fifoctlr_cc_tb.tf,另一個是時序仿真(后仿真)testbench文件fifoctlr_cc_tb_timing.tf,這里我們主要分析功能仿真文件,為了方便大家理解,以下(下一帖)為注釋過的功能仿真testbench。大家看testbench的代碼時,對照FIFO需要驗證的功能點,檢查是不是所有功能點都經(jīng)過了驗證。

FIFO的testbench主要包括初始化、驗證initial塊、讀寫task等內(nèi)容,初始化部分主要完成復(fù)位信號、CLK信號等的初始化工作,讀寫task把讀寫、delay等操作模塊化,方便使用。這里主要介紹一下驗證initial塊,也可以說是驗證的主程序,如下所示。

initial begin

delay; //保證驗證環(huán)境正確復(fù)位

writeburst128; //寫入512個數(shù),F(xiàn)ull信號應(yīng)該在寫入511個數(shù)后變高

writeburst128;

writeburst128;

writeburst128;

read_enable = 1; //讀出一個數(shù),F(xiàn)ull信號應(yīng)該變低

writeburst128; //同時讀寫,檢查FIFO操作是否正確

read_enable = 0; //讀操作結(jié)束

endwriteburst; //寫操作結(jié)束

delay;

readburst128; //連續(xù)讀512次,Empty信號應(yīng)在讀出511個數(shù)后變高

readburst128;

readburst128;

readburst128;

endreadburst;

end

這段程序首先延遲5個時鐘周期,等初始化完成之后再開始驗證工作。驗證時,首先寫入512個數(shù),使用波形觀察器可以檢查寫入的過程是否正確,以及Full信號在寫入511個數(shù)后是否變高;然后read_enable = 1,讀出一個數(shù),F(xiàn)ull信號應(yīng)該變低,這樣寫操作和Full信號的驗證就基本完成了;程序接著也啟動了寫操作,由于此時read_enable仍然為高,即讀寫同時進(jìn)行,這是對實際情況的模擬,可以對FIFO的功能進(jìn)行更嚴(yán)格的驗證;最后,連續(xù)讀FIFO 512次,用波形觀察器檢查讀操作是否正確,Empty信號是否在讀出511個數(shù)后變高,如果這些操作都是正確的,那么FIFO的功能就基本正確了。

需要注意的一點是,以上的程序是不可綜合的,因為不是RTL級描述,而是行為級描述(Behavioral Description)。行為級描述的特點是直接描述對象的功能,具有比較高的抽象層次,開發(fā)、運行速度都比RTL代碼要會,因此testbench都是用行為級描述寫的。關(guān)于行為級描述的特點、寫法以后將有專門的章節(jié)論述。

這個testbench的特點是,輸入激勵由testbench產(chǎn)生,輸出響應(yīng)的檢查人工完成,這樣的testbench編寫相對容易,可以加快開發(fā)速度,作為開發(fā)人員自己驗證是非常好的選擇。有些testbench能完成輸入激勵和輸出檢查,不用觀察波形也能完成驗證工作,這樣的 testbench具有更高的自動化程度,使用方便,可重復(fù)性好,當(dāng)設(shè)計比較復(fù)雜而且團隊中有專門的驗證工程師時,一般會有驗證工程師建立一套這樣的 testbench,用于驗證開發(fā)工程師的RTL級代碼,如果發(fā)現(xiàn)問題,開發(fā)工程師修改后在testbench再運行一次所花的時間非常少,開發(fā)復(fù)雜項目時這樣做可以比用波形觀察器節(jié)省很多時間。

3.總結(jié)

驗證一般要通過寫testbench實現(xiàn),從《FPGA驗證》第一篇我們知道,testbench要完成向DUT施加激勵和檢查DUT相應(yīng)是否正確的功能,這就要求我們非常清楚待驗證模塊(DUT)的功能,這樣才知道需要驗證什么、如何施加激勵和如何檢查響應(yīng)是否正確。寫

第三篇 驗證工具介紹

我們做FPGA/IC開發(fā)會用到很多工具,包括代碼輸入、仿真、綜合、布局布線、時序分析等各種各樣工具,熟悉這些工具是成功完成設(shè)計的關(guān)鍵,因為我們的設(shè)計思想需要通過這些工具來實現(xiàn),只有清楚的知道工具的用法、如何設(shè)置參數(shù)、如果檢查工具的輸出結(jié)果,才能使設(shè)計者的想法變?yōu)轱@示,對驗證來說也是如此。

驗證的工具很多,有些是驗證必不可少的,例如仿真器,有些工具可以代替人完成最繁瑣的工作,并能提高功能驗證的可信度,例如linting和代碼覆蓋率工具。這里我們介紹常用驗證工具的特點和用途,以便為工具的使用提供參考。

1)代碼檢查工具

常用的代碼檢查工具有nlint等,nlint根據(jù)設(shè)計的RTL描述代碼結(jié)構(gòu)做靜態(tài)分析,推斷描述代碼存在的邏輯錯誤,但無法決定描述代碼是否能夠現(xiàn)實設(shè)計要求的功能。代碼檢查工具可用于強制代碼遵從編寫規(guī)范,由于代碼檢查工具工具是靜態(tài)驗證工具,因此運行速度快,可以節(jié)省時間。由于Verilog不是強類型語言,使用代碼檢查工具非常必要,可以檢測race conditions 及數(shù)據(jù)寬度不匹配,可保證Verilog正確描述數(shù)據(jù)處理過程,避免造成數(shù)據(jù)的棄位及增位現(xiàn)象,這種錯誤通過仿真并不一定發(fā)現(xiàn)。因為verilog 語言的特點, 對Verilog描述的設(shè)計,Linting tool是一種有益的驗證工具。因為VHDL 語言的特點,對VHDL使用Linting tool的作用不如對Verilog語言那么明顯,但Linting tool還是能發(fā)現(xiàn)一些潛在的問題。

2)仿真器

仿真器是常用的驗證工具,它通過忽略及簡化設(shè)計的物理特性,對設(shè)計的實現(xiàn)進(jìn)行模擬。仿真器通過執(zhí)行RTL級的設(shè)計描述,模擬設(shè)計的物理實現(xiàn),它無法確定設(shè)計真實的物理實現(xiàn)與設(shè)計描述之間的區(qū)別。仿真的結(jié)果取決于設(shè)計描述是否準(zhǔn)確反映了設(shè)計的物理實現(xiàn)。仿真器不是一個靜態(tài)工具,需要編寫激勵和檢查輸出響應(yīng)。激勵由模擬設(shè)計工作環(huán)境的testbench 產(chǎn)生,響應(yīng)為仿真的輸出,由設(shè)計者確定輸出的有效性。

仿真器的類型分為3種類型,Event-driven Simulator(事件驅(qū)動仿真器)、Cycle-Based Simulator(基于周期的仿真器)、Co-Simulator(聯(lián)合仿真器),分別介紹如下:

1.Event-driven Simulator

事件驅(qū)動仿真器是最常用的仿真器,例如modelsim/VCS等都是事件驅(qū)動仿真器,它將信號的變化定義為一個事件,該事件驅(qū)動仿真執(zhí)行,事件驅(qū)動仿真器能準(zhǔn)確地模擬設(shè)計的時序特征,可模擬異步設(shè)計。

2.Cycle-based simulator

Cycle-based simulator仿真器的特點是忽略設(shè)計的時序,假定所有flip_flop的setup和hold時間都滿足要求,在一個時鐘周期,信號僅更新一次,從而信號必須與時鐘同步。仿真速度比事件驅(qū)動仿真器高。基于周期的仿真器的工作過程步驟是,首先編譯電路,將組合邏輯壓縮成單獨的表達(dá)式,根據(jù)該表達(dá)式可確定flop的輸入,然后執(zhí)行仿真,遇到時鐘的有效沿, flip_flop 的值被更新。基于周期的仿真器的缺點是不能仿真異步電路,不能進(jìn)行驗證設(shè)計的時序。

3.Co-Simulators

聯(lián)合仿真器對同一設(shè)計各個部分,分別用不同的仿真器仿真,如即含有同步設(shè)計又含有異步設(shè)計的電路,可用Event-driven Simulator對異步設(shè)計仿真,用Cycle-based Simulator對異步設(shè)計仿真。聯(lián)合仿真器中各個Simulator 的操作是locked-step的,類似于電路的pipeline 操作。其缺點是由于不同仿真器之間需要同步和相互通訊,Co-Simulators的仿真速度受到最慢Simulator的限制,因而影響仿真器的性能,而且在各仿真器傳送的信息會產(chǎn)生多義性。

4.Hardware modeler

硬件模擬器創(chuàng)建一個物理芯片的邏輯模型,向仿真器提供該芯片的行為信息,芯片和仿真器的通信過是首先將物理芯片插入硬件仿真器,然后格式化來自仿真器的數(shù)據(jù),作為該芯片的輸入,最后將該芯片輸出的數(shù)據(jù),包含時序信息,送往仿真器。硬件模擬器可以提供很高的仿真速度,但是設(shè)備價格高昂。需要注意的是,硬件模擬器做的仍然是功能仿真,而不是時序仿真,因為芯片是降頻運行的。

3)波形觀察器

仿真調(diào)試的過程中波形觀察器是必不可少的工具,它能提供信號狀態(tài)和變化的詳細(xì)信息,但是波形觀察器不能用來判斷一個設(shè)計是否通過驗證,因為波形是不可重復(fù)的且無法用于遞歸仿真。

波形觀察器的優(yōu)點是可以觀察仿真的整個過程,有利于設(shè)計及testbench 的診斷,缺點是由于要輸出波形,影響了仿真的速度,因此應(yīng)盡可能限制在波形圖中顯示的信號數(shù)量及時間長度。波形觀察器的另一個作用是波形比較,主要用于 redesign,保證設(shè)計具有cycle-accurate的后向兼容性。在波形比較中,不能僅看表象,需仔細(xì)分析,確認(rèn)波形之間存在的差別是有意義的。例如,有時我們僅關(guān)心波形transitions之間的相對位置,而不關(guān)心它的絕對位置。

以上是比較常用的驗證工具,另外可能用到的驗證工具有:形式驗證工具、靜態(tài)時序分析工具以及Vera、SpecmanE、SystemC等高級語言驗證工具,這些工具在復(fù)雜的IC/FPGA設(shè)計中用得比較多。

電子發(fā)燒友App

電子發(fā)燒友App

評論