編者按:我很榮幸有機會去得到Xilinx的允許去介紹以下內容,這是Xcell Journal第四季度版上的文章。電子發燒友網還專門為廣大FPGA設計工程師提供了《如何成為Xilinx FPGA設計專家基礎篇》創新技術電子書,內容精彩,不容錯過。

電子發燒友網訊:這篇文章是關于如何實現FPGA設計的低功率運行。這是一個全球性的問題,因為,這對無線、軍用移動設備和航空應用等依賴于電池電源的產品來說是非常重要的。這一類的應用覆蓋了飛機、無人機和前線士兵等通信設備。

這是一篇綱要,是關于最新的7系列FPGA在開發周期的每個階段中的低功率設計技術的。

功率問題已經成為FPGA選型的首要考慮因素。電源管理是很多應用設計的關鍵。一些標準指定每個系統的最大功率。例如,設計師必須在設計流程的早起考慮到功率問題,這通常和FPGA的選型同時進行的。

通過減少電源供給線、簡化電源供給設計和熱量管理降低等手段降低FPGA的功率消耗可以簡化板上設計。低功率對延長電池壽命、提高系統可靠性起著重要作用。

功率挑戰

隨著工藝技術的發展,晶體管就如摩爾定律預言那樣變得越來越小了。這個現象帶來的一個弊端就是引致了晶體管的泄露,這就會引起更大的靜態能量消耗——這是FPGA沒有工作的時候產生的電流總量。增強的FPGA性能使時鐘效率變得更高,這個會引致更高的動態功率。靜態功率是由晶體管的泄漏電流決定的,動態功率則是基于可編程裸機和I/O的轉換頻率。隨著這兩種電源消耗的惡化,FPGA隨著產品的更新換代逐漸增大其容量。更多的邏輯意味著在每個設備上高速運行著更多的晶體管以及更多的泄漏。

考慮到以上因素,設計者必須在其設計前期更加注意他們的電源和熱量管理。在設備上面加上一個散熱器并不能解決這些問題。真實情況是設計者必須盡量減少設計里面的邏輯。

讓我們瀏覽一些指南,這可以幫你們了解在FPGA設計過程中為降低功耗而進行的某些操作。很明顯,在設計的早期對這些事情有一個透徹的了解可以獲得最大的回饋。

?

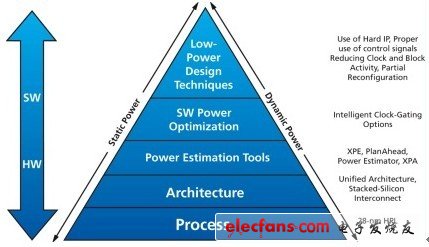

圖一:從設計流程的FPGA選型到低功耗設計技術的過程中闡明不同的意義。

7系列工藝技術

在FPGA的選型過程中,認真考慮工藝技術可以幫助你辨別設備的泄漏和性能。Xilinx的7系列FPGA是基于28HPL(28nm的高性能、低功耗)工藝,覆蓋高性能空間,同時有明顯的功耗降低。選擇基于低泄漏HPL工藝可以降低在FPGA設計過程中的靜態功耗管理方案的復雜程度以及花費。

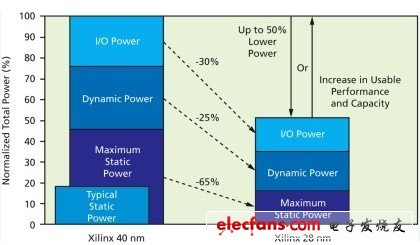

在28HPL技術制造的FPGA相對于7系列的FPGA沒有任何性能優勢,然而某些產品,與FPGA相比,有著多于兩倍的靜態功耗和在減少泄漏方面有著競爭優勢。圖2展示了一個7系列FPGA綜合的能耗降低途徑,相對于上一代40nm的FPGA,可以降低一半的功耗。

?

圖2:Xilinx7系列FPGA的功耗相對于之前的40nm產品降低一半功耗。

為了開發產品及將來將其遷移到一個較小的產品,設計師可以選擇一個比較大的FPGA。選擇一個比較小的FPGA不但可以降低花費,同時會降低系統的功耗。

全系列的FPGA產品都是基于統一的架構。這個統一的架構使不同的FPGA設備的向上或向下遷移變得更簡單,在Xilinx的7系列產品線中的遷移也同樣簡單。如果考慮從Virtex-6或Spartan-6設備遷移到7系列以及在7系列中進行遷移,可以參考“7系列遷移指南”(UG429)。

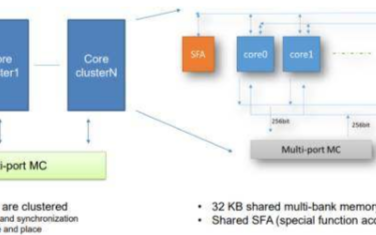

Xilinx的堆疊硅片互聯技術

對于大型的系統,設計者通常會選擇多樣的FPGA,這類型的架構通常需要在不同的FPGA之間要有相當高速度的精妙和艱巨的數據轉移。選擇比較大的7系列FPGA,例如XC7V1500T和XC7V1500T設備,是利用Xilinx的堆疊硅片互聯技術制造的。這可以解決以上的問題。簡而言之,這個SSI技術(堆疊硅片互聯技術)將多裸晶固定在一個硅中介層上面,這可以在它們之間提供成千上萬的連接,這樣就能制造出一個獨立的大設備。堆疊硅片互聯技術的一個好處就是與相同規模的標準單片產品相比,能降低降低靜態功率的最大值。

堆疊硅片互聯技術在I/O互聯功率方面有明顯的減小,與在一板上有多樣化的FPGA相比,SSI技術引以為豪的一點就是相對于一個帶有相同的I/O和收發器的接口,其在I/O互聯功率方面有100X(帶寬/W)的降低。這個明顯的降低是因為他們所有的連接是在芯片上,而不是借助需要的功率去從芯片驅動信號,那樣的話就可以得到不可思議的速度和低功耗。

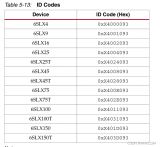

表一:靜態、動態和性能功率比較。

?

?

電壓調節的可選擇性增強

Xilinx的7系列FPGA提供重要的電壓調節選擇。

7系列的FPGA給-3和-2L設備提供了一個比較大的溫度范圍(0-100℃)選擇。由于28HPL工藝的緣故,2LE設備可以工作在1或者0.9V的電壓。這些設備被稱為-2L(1.0V)或者-2L(0.9V)。工作在1.0V的-2L設備有著和-2I和-2C一樣的性能,但卻有著更低的靜態功率。工作在0.9V的-2L設備有著和-1I和-1C一樣的性能,其同時也有著更低的靜態和動態電壓。

在0.9V的電壓下,這些設備電壓的獨自下降可以降低靜態功率大約30%的消耗。降壓同樣會降低性能,但是因為其速度和嚴格的泄漏規格,Xilinx屏蔽這些12L(0.9V)設備。與標準速度水平的設備相比,這種屏蔽方法會給功率帶來55%的降低。

通過選擇-2L系列設備,你可以在動態功率上獲得額外的功率節省。因為動態功率與VCCINT2成比例,在VCCINT減少10%,則會在功率方面提供20%的節省。

功耗估算工具:

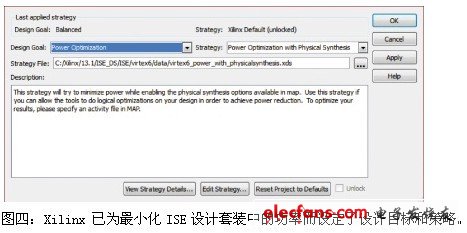

市面上有多種多樣的工具提供給工程師選擇,用來估算在整個研發周期FPGA設計所需要的熱能和電源。圖三展示了FPGA開發過程每個步驟有效的Xilinx工具。

?

在研發剛開始的時候,XPOWER Estimator(XPE)電子制表軟件甚至可以提供草圖設計和項目導入階段之前的早期功耗估算。XPE有助于架構評估和設備選擇,同時它還可以幫助選擇適當的電源和應用所需的熱量管理元器件。

PlanAhead軟件提供RTL階段的設計功率分配估算。設計者可以指定設備操作環境、I/O性能和設計使用限制的默認活動率,這也可同過GUI來完成。PlanAhead軟件接下來就會讀HDL編碼去估算所需的設計資源,同時記錄每個資源靜態分析的功率。隨著對設計意圖的細節的了解深入,RTL功率估算將會比Xpower Estimator電子制表軟件更加精確,其精確度卻并不如Xpower Analyzer。

Xpower Analyzer (XPA)是一個功率分析工具,它提供一個制定工作條件下允許細節分析功耗和熱量信息的綜合性GUI。

你可以在兩種不同的觀點之間切換,以鑒定阻礙型(時鐘樹、邏輯、信號、I/O等)或者超過設計層的功耗。

它們提供一個非常有效的方法去確定障礙的位置,從而進行功率優化。

軟件功率優化

通過最小化同時有效的block RAM端口的數量,你可以利用block RAMs來對功率進行優化設計。這次優化,使-power選擇在 XST 狀態,修改跨越多樣block RAM的RAM和ROM描述。這個優化調整位置線、端口和寫控制信號,這樣就可以最小化在每個時鐘周期里面的有效的block RAM的數量,同時保證你的設計滿足時間限制。

之后,促進效率的最優化而忽略對性能的沖擊。當你了解時序路徑與內存的關系并不重要的時候,將block_power2選項調為ram_style限制。這樣可以節約15%到75%。

同樣,用XST的Area Optimization 模式,這個選擇會使你設計用到的資源數量最小化。應注意的是當區域最優化以后,性能會受到限制。

一個額外的策略是activity-aware最優化,這是intelligent gating的另一種說法。這些算法分析邏輯方程式去檢測每個對結果沒任何影響的時鐘周期源寄存器。軟件利用FPGA邏輯中充足的時鐘啟動(CE)可利用的資源去產生細粒度門信號。在很多方案里,的核心動態功率總體減少超過15%,額外插入的門邏輯并不影響性能。

功率設置的另一種方法是利用capacitance-aware最優化,有兩個關鍵技術:

Group clock loads:這個過程整理同步元素(例如觸發器或者DSP blocks)去最小化每一個時鐘網的范圍,當你把clock loads沿著小部分的水平或者垂直的clock spines放置,軟件會禁止時鐘區域的未使用的分支。這回減少時鐘資源和緩沖要求,這樣就會節省核心動態功率,這個是同過map-power選項控制的。

Group data loads:這個算法最小化你設計中的用線長度,同時還確保你滿足性能需求。因為動態功率隨著你能看到的路線架構的類型,Grouping data loads能夠節省功耗。這個grouping算法,同樣的使在 map – power選項,通過將相同的邏輯擺在一起降低功耗。

ISE 設計組合突出其預期目標和策略,使功率在綜合、map的情況下最優化。這種方法或許是利用所有綜合限制的不默認限制設置的最好替代。然而,在這個情況下,會引起延時。

最好,Xilinx執行工具自動化關掉不需要用到的收發器、鎖相回路、數字時鐘管理模塊和I/O。在7系列,Xilinx也添加不需要用到block RAM的電源門。Block RAM的泄漏只有在你使用特殊設計的block中發生,而不是發生在設備上所有的block RAM。

?

低功耗設計技術

工程師可以搜索到很多降低FPGA設計功耗的貼士和技術,首選是用專用的硬件模塊而不是在CLB中執行相同的裸機。為了減少功耗,你必須在設計中想法設法尋找可能存在的方法。這允許你去用到一個盡可能小的設備,同時減低靜態功耗。

用專用的硬核模塊是降低靜態和動態功率的一個最重要的方法,同時這樣也能夠輕易滿足時間需求。因為相對于一個等效的CLB邏輯,硬核的晶體管數量遠遠比CLB少,因此它能夠降低靜態功耗。

按照通常的做法,你可以嘗試去推斷出盡可能多的資源。你可以通過代碼或者在限制文檔中

為FPGA構造或者硅資源獨自或作為一個整體控制推斷資源量。為了安裝特定的資源,你同樣可以影響Xilinx的 CORE Generator 工具去自定義專用硬件。

除此之外,你可以為其他不顯著的任務明智地采用不會被用到的硬核。DSP48 slice如倍頻器、加法器/累加器、邏輯比較器、模式適配器和計數器那樣處理很多邏輯功能。你可以將block RAMs當作狀態機、數學函數、ROMS和邏輯查找表使用。

控制信號的最佳使用

控制信號(如時鐘、設置、復位、時鐘啟動等的控制同步基礎信號)的使用會影響設備的密度、利用率和性能。遵循一些指導會幫你將功率影響降到最低。

首先,避免在一個累加寄存器或鎖存器上使用一個設置和復位。Xilinx FPGA的觸發器支持異步和同步設置和復位控制。然而,底層觸發器本身每次只能執行設置、復位、預設值或者清除。在RTL編碼里面編進多于一個的功能則會造成執行一個用觸發器SR端口的狀態,其他狀況則是用結構邏輯,這樣就會用到更多的FPGA資源。

如果其中的一個條件是同步,其他的是異步,那么異步狀態將會是唯一一個利用SR端口執行的,同時同步狀態則用結構邏輯實現。總之,最好避免多于一個狀態。此外,如果觸發器的SR端口是同步或者異步,四個觸發器在同意情況下確認的時候,只有一個產生作用。

除此之外,用高邏輯電平控制信號,寄存器的控制端口是高電平。不建議在FPGA設計中用地邏輯電平復位。因為低邏輯電平信號在可以直接驅動寄存器的控制端口之前需要倒置,因此它們用到更多查找表。這個倒置必須通過一個LUT完成,因此會占去一個LUT輸入。

因此,低邏輯電平控制信號可能導致更長的執行時間,同時會引致設備的利用率變低,這會影響時序和功耗。

在HDL編碼或者具體元器件中盡可能用到高邏輯電平控制信號。當在設計的時候不能夠控制一個控制性信號的極性,你應該在編碼的最高層反置信號。I/O邏輯會執行沒有用到任何額外FPGA邏輯的反相器,因此會達到最優的利用、性能和功率。

多余的設置和復位

代碼中多余的設置和復位可以避免SRLs、LUT RAMs、RAMs模塊和其他方面可能涉及的邏輯結構的推斷。盡管設計師會發現這不合適,很多的回路會被設計去自我復位,或者簡化不需要復位。例如,當一個電路只是用來初始化寄存器,復位是不需要的。因為寄存器初始化在配置的時候自動發生。

通過減少設置和復位的使用,隨著設備的利用率的提高,設計師可以得到更好的安排,性能提高和功耗減少。

如果你對低功耗是很在意的,另一個必須關注的領域則是時鐘和模塊活動。你應該充分利用BUFGMUX,BUFGCE和BUFHCE去降低功耗。這些約束條件會在整個時域暫停時鐘。同樣地,對應用來說,這只可以通過使用FPGA寄存器的時鐘啟動接口去暫停設計的一個小區域的時鐘。

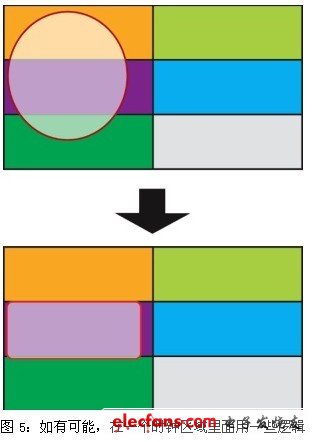

分布在多種時鐘區域的設計利用到更多的時鐘資源,同時其功率損耗也會更大。只要有可能,在一個單獨時鐘域里面間歇地使用邏輯(圖5)。這會幫助你減少功耗。雖然工具會自動完成這個,但有些設計還是需要手動去獲得同樣的效果。

圖5:如有可能,在一個時鐘區域里面用一些邏輯

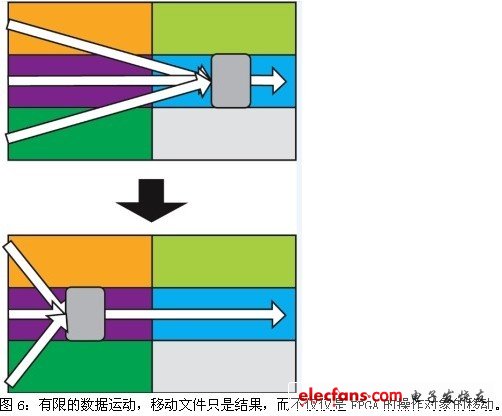

另一個重要的技術是限制數據運動。移動文件只是結果,而不僅僅是在PFGA移動操作對象。用到更少和更短的總線可以使其電容量更小,運行速度更快,同時功耗也不大。在預布局的時候,工程師對設計的引腳和相對應的邏輯放置應該加倍注意。

降低靜態功耗的局部可重構技術

降低靜態功耗的的一個方法是簡單的選用一個更小的設備。通過局部可重構技術,設計師可以從基本上時間片一個FPGA,同時能夠單獨的運行他們的部分設計。因為并不是設計的每一部分都需要100%的時候,所以這些設計之后會需要一個更加小的設備。

局部可重構技術可能會像處理靜態功耗那樣降低動態功耗。例如,許多設計必須快速運行,但最大性能可能只需要很少的時間。為了節省電能,設計師利用局部可重構技術去置換出一個同樣款式的,但帶有低功耗的高性能設計,而不是所有時間內都是最大性能的設計。當系統需要高性能的時候,你可以切換高性能設計。

這個規則同樣適用于I/O標準,尤其是對于那些不需要長時間保持大功率的接口。由于需要比較大的DC電流去激勵,不管工作與否,LVDS都是一個大功率的接口。當設計不需要高性能的時候,設計師可以運用局部可重構技術去將其I/O從LVDS轉換到一個類似LVCMOS的低功耗接口,然后在系統需要高速傳輸的時候將其切換到LVDS的模式。

在低功耗設計的時候充分利用時序約束也是非常重要的。如果你在一個溫度控制環境下操作,記住為了滿足時序需要,你可以忽略這部分。要確保只限制指定的時鐘頻率那部分。這表明一個將要用到的,較快的時鐘頻率不會形成一個更好的設計。顯然,因為減少資源共享、更多的邏輯/寄存器復制、更多的布線和FPGA專用特性的減少,這樣的話就會用到更多的結構資源。所有的這些都能很明顯的影響動態功率。

I/O功耗已經成為整體功耗的最重要一環,一些設計的I/O功耗甚至占了整體功耗的50%,尤其是在內存密集型系統。

可編程的轉換速率和驅動強度降低I/O驅動的的動態功耗。有很多類似HSLVDCI的標準可以在FPGA TO FPGA通信中節省比較大的功耗。

所有Xilinx 7系列設備提供可編程的轉換速率和驅動強度。Xilinx的FPGA數控電阻(DCI)技術,也是三態的。在內存從FPGA寫入數據時,DCI消除端接電源,因此設備只有在讀數據的時候消耗端接電源。

7系列的設備為HSTL和SSTL合并了一個用戶可編程參考接收器電源模式。你在一個I/O-by-I/O基礎上控制這兩個可編程電源模式,這可以通過在功耗和性能中權衡幫你降低DC功耗。

收發器功率描寫

Xilinx為了高性能和低抖動優化了7系列的FPGA收發器。這些收發器提供幾個低功耗的操作特點。使設計師為平衡功耗和性能自定義靈活性的操作和間隔尺寸。

在7系列的FPGA,共享鎖相回路可以節省比較大的功耗。對一個具有相同行率的四路設計(如XAUI),你可以用一個四通道PLL 取代一個單通道PLL來節省功耗。同樣,在某些方案里,因為一個PLL可以在高速率和低速率的范圍里運行,因此最好去選擇一個比較低的操作范圍去節省功耗。

你同樣可以使用一個單獨的TX/RXPOWERDOWN設置。在低功耗模式下的PPL電源休眠是可行的。

開發周期的每一個步驟

在執行編碼之前明白和實施敏感電源設計技術是降低系統功耗的一個最大有效的途徑。在開發周期的相應的階段應用不同的Xilinx工具可以幫助你滿足功耗規格要求,同時在也可以硬件工程師選擇必要電源的數量、型號、大小上面提供相對應的信息。Xilinx 7系列FPGA通過利用工藝技術和結構設計提供了前所沒有的功耗效率。

——電子發燒友網版權所有,轉載請注明出處!

?

?

?

電子發燒友App

電子發燒友App

評論