引言

人工神經網絡在很多領域得到了很好的應用,尤其是具有分布存儲、并行處理、自學習、自組織以及非線性映射等特點的網絡應用更加廣泛。嵌入式便攜設備也越來越多地得到應用,多數是基于ARM內核及現場可編程門陣列FPGA的嵌入式應用。某人工神經網絡的FPGA處理器能夠對數據進行運算處理,為了實現集數據通信、操作控制和數據處理于一體的便攜式神經網絡處理器,需要設計一種基于嵌入式ARM內核及現場可編程門陣列FPGA的主從結構處理系統滿足要求。

1 人工神經網絡處理器

1.1 人工神經網絡模型

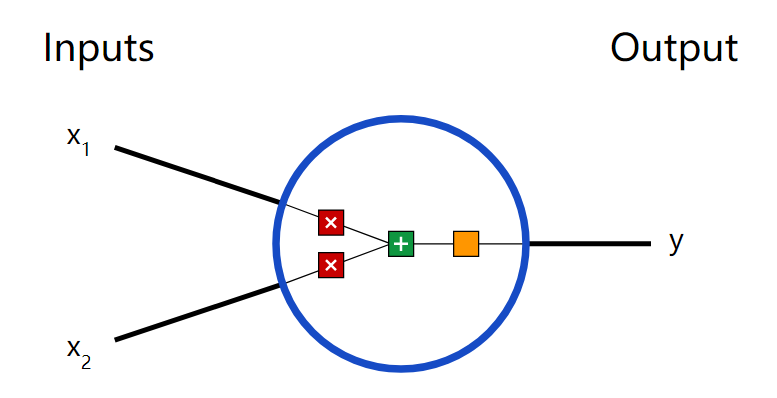

人工神經網絡是基于模仿大腦功能而建立的一種信息處理系統。它實際上是由大量的、很簡單的處理單元(或稱神經元),通過廣泛的互相連接而形成的復雜網絡系統。最早的神經元模型是MP模型,由輸入X、連接權值W和閾值θ、激活函數f和輸出O組成,如圖1所示。

圖1 人工神經元的MP模型

神經元j的輸出為:

式中:netj是神經元j的凈輸入,xi是神經元j的輸入,wij是神經元i到神經元j的權值,θj是神經元j的閾值,f()是神經元凈輸入和輸出之間的變換函數,稱為激活函數。[1]

后來的各種網絡模型基本都由這幾個因素構成,例如圖2的三層BP神經網絡模型。

圖2 三層BP神經網絡模型

三層BP網絡的標準學習算法如下[2],當網絡輸出與期望輸出不等時,存在輸出誤差E,定義如下:

進一步展開,是各層權值wij(隱層到輸出層)、vij(輸入層到隱層)的函數:

要使誤差不斷減小,需對權值進行處理,最終的權值調整的公式為:

三層前饋神經網絡的BP學習算法的向量形式如下,對于輸出層:

容易看出,各層權值調整公式均由3個因素決定,即學習率η、本層輸出的誤差信號δ以及本層出入信號Y(或X)。其中,輸出層誤差信號與網絡的期望輸出與實際輸出之差有關,直接反映了輸出誤差,而各隱層的誤差信號與前面各層的誤差信號都有關,是從輸出層開始逐層反傳過來的。

神經網絡的訓練學習的過程就是通過不斷地調整各個節點的權值,使輸出誤差達到最小,最終獲得穩定可靠的權值,實現網絡的預定功能。

1.2 人工神經網絡的FPGA實現

算法公式實際隱含著各種運算過程,乘累加計算、激活函數及其導數的計算和邏輯運算是3種必不可少的運算,因此FPGA的實現主要是各種運算器的設計和連接。處理器要處理各種類型的數據,樣本數據X(訓練樣本、實際樣本),網絡參數(學習速率η、每層神經元個數n等)和權值W是必不可少的。網絡參數和初始權值用來對網絡初始化,訓練樣本用來訓練網絡學習,最后在網絡應用階段對實際樣本進行處理。

圖3 神經網絡的運算模塊和數據存儲結構圖

圖3展示的是FPGA神經網絡處理器的主體部分:存儲模塊和運算模塊。根據網絡的結構特點,連接權值處于各個神經元節點的連接處,與各自的權值運算結構一一對應,為分布式,所以分布式存儲器WM中存儲權值數據;樣本數據統一從網絡的輸入層進入網絡,故DM中存儲樣本數據;MAE是處理器的運算部分。

2 通信硬件設計

2.1 系統整體架構

系統整體結構框圖如圖4所示,分為ARM端和FPGA端兩個部分。ARM端有兩個功能:一是從內存中讀取已有數據,通過DMA方式下載到FPGA端,按照數據類型將數據下載到不同的存儲設備和存儲空間;二是對FPGA進行控制,主要是各種中斷操作。FPGA端的功能是接收ARM傳送的數據,存儲數據,并在微程序控制器的控制下進行運算處理,最后把結果上傳給ARM。

圖4 系統整體結構框圖

ARM端以S3C44B0X芯片為核心,外部擴展各類設備構成。S3C44B0X 是三星公司的16/32位微處理器,片內集成了ARM7TDMI核,并在此基礎上集成了豐富的外圍功能模塊,為嵌入式設備提供一個低成本高性能的方案。

S3C44B0X擁有4通道的DMA控制器,兩個ZDMA,連接于SSB(三星系統總線);另外兩個BDMA,連接在SSB和SPB(三星外圍總線)之間的接口層。其中ZDMA可從存儲器到存儲器、存儲器到I/O設備和I/O設備到存儲器傳送數據。DMA操作由S/W或來自外部請求引腳(nXDREQ0/1)的請求來啟動。[3]

在DMA操作中,通過配置DMA特殊功能寄存器來實現對DMA的控制,如圖5所示。

圖5 ZDMA 控制器框圖

FPGA端的組成為FPGA芯片和擴展存儲器。按處理數據類型的不同設計不同的存儲結構,具體如下所列。神經網絡的結構參數存放于控制寄存器組,初始權值、穩定權值存放于分布式存儲器,其他參數(學習速率、學習速率調整因子等)存放于專用寄存器組A中,處理結果存放于專用寄存器組B中,樣本數據存放于擴展存儲器SD卡中。

以上所述的存儲體,除擴展存儲器外其他結構都在FPGA芯片內部設計完成。采用這種設計是基于FPGA片上存儲資源的使用情況:①FPGA的配置文件占用;②分布式存儲器占用;③各類寄存器組占用。當樣本數據數量較大時會占用比較大的空間,FPGA芯片將不能滿足,因此不能把樣本數據存儲在片上,而是存儲于擴展存儲器。

2.2 硬件連接

從上面的介紹容易發現,ARM芯片的通信對象是基于SRAM工藝的FPGA芯片上的存儲體。因此,FPGA芯片作為存儲設備時,ARM芯片可直接與其相連。ARM與FPGA硬件連接示意圖如圖6所示。

圖6 ARM與FPGA硬件連接示意圖

ARM與FPGA的片上存儲體的地址總線連接設置為12位,足夠存儲和尋址需求。

數據總線的寬度為28位。神經網絡處理器的數據精度為16位[4],FPGA樣本數據寄存器還有12位外部擴展存儲器的地址數據,因此整個數據總線的寬度為二者之和。除樣本數據寄存器之外的片上存儲體,數據線占用28位數據總線中的低16位。

控制總線包括ARM端的片選線nGCS6和讀/寫控制線。對ARM相應的寄存器進行配置可激活BANK6(FPGA片上存儲體)和讀/寫數據。

根據數據存儲位置的不同,硬件連接可分成兩方面。如圖7所示。

圖 7FPGA端部分硬件連接示意圖

第一,存儲位置為FPGA端的外部擴展存儲器。①ARM與FPGA通過12位地址總線、28位數據總線及控制總線直接相連,數據寫入樣本數據寄存器。②樣本數據寄存器的28位數據按照12位地址數據、16位樣本數據,通過FPGA與外部擴展存儲器之間的12位地址總線、16位數據總線,在存儲控制模塊的控制下,把樣本數據寫入擴展存儲器。因此,把樣本數據寄存器分為兩部分,低16位為樣本數據,高12位為該樣本數據在外部擴展存儲器的存儲地址,如下所示。

第二,存儲位置為FPGA的片上存儲體。ARM與FPGA通過12位地址總線、28位數據總線中的低16位、控制總線直接相連,控制寄存器組、專用寄存器組、分布式存儲器連接在這些總線上面。

片上集成存儲系統采用統一編址的方式,其優勢在于可以通過ARM芯片的DMA方式進行數據傳輸,既可以提高傳輸速率又能夠釋放CPU。外部擴展存儲器因為只受FPGA控制而采用獨立編址,但地址域的設計接續片上集成存儲系統的地址,如此方便操作。

3 ZDMA控制設計

ARM端與FPGA端的數據通信如圖8所示,分為3個階段:

① 網絡初始化階段的數據通信:配置網絡初始化數據。a)需對網絡訓練執行階段②,b)否則執行階段③。

② 網絡訓練階段的通信:下載訓練樣本數據,訓練完成上傳穩定的權值。

③ 實際應用階段的通信:下載實際樣本數據,上傳處理結果。

每一個階段都是在ZDMA的方式下進行。每一個階段完成后都會進入中斷,提示本階段完成并進行下一步操作。

圖8 數據通信階段流程圖

3.1 下載數據時ZDMA的配置

按照是否為樣本數據,通信可分為兩個階段:一是面向FPGA片上集成存儲系統的非樣本數據通信,二是面向FPGA片外擴展存儲器的樣本數據通信。

本設計使用ZDMA0、ZDMA1兩個通道中的一個。與ZDMA有關的特殊功能寄存器有:

ZDMA控制寄存器(①ZDCONn):主要用于對DMA通道進行控制,允許外部DMA請求(nXDREQ)。

ZDMA0/1初始源/目的地址和計數寄存器、ZDMA0/1當前源/目的地址和計數寄存器。

ZDMAn初始/當前源地址寄存器(②ZDISRC、③ZDCSRC):初始源地址為數據在ARM芯片內存的存放地址;當前源地址為即將傳輸的數據的內存地址,值為初始源地址+計數值。

ZDMAn初始/當前目的地址寄存器(④ZDIDES、⑤ZDCDES):分為兩個階段:第一階段傳輸非樣本數據時初始目的地址為BANK6的起始地址;當前目的地址是變化的,為初始目的地址+計數值。第二階段傳輸樣本數據時初始目的地址也是當前目的地址,為樣本數據寄存器的地址。

ZDMAn初始/當前目的計數寄存器(⑥ZDICNT、⑦ZDCCNT):初始值為0,當前值隨著傳輸數據的個數逐一遞增,直至達到所有數據的數量。樣本數據和非樣本數據的傳輸分兩個階段進行,各自獨立。

從這個過程中可以看出,配置ZDMA時需考慮FPGA端存儲結構體多樣性的問題。

3.2 上傳數據時ZDMA的配置

神經網絡處理器的穩定權值和處理結果存儲在FPGA上統一編址的專用寄存器組B中,不存在存儲結構體多樣性的問題,所以上傳數據時ZDMA的配置相對簡單:

初始源地址即專用寄存器組B的起始地址,每傳送一次數據專用寄存器組的地址指針+1并作為當前源地址。

初始目的地址為要存放數據的內存塊的起始地址,每傳送一次數據內存塊地址指針+1并作為當前目的地址。

計數寄存器的初始值為0,每傳送一次數據其值+1,達到設定的目標值時數據上傳即完成。

結語

本文首先介紹了人工神經網絡的模型和算法以及FPGA的實現,并通過對網絡結構的分析設計了FPGA端的數據存儲系統。然后分析了ARM端和FPGA端各自的功能,在此基礎上把兩者結合在一起,設計了一種利用ARM的ZDMA方式相互通信的方案。

電子發燒友App

電子發燒友App

評論