彼得·蒂爾在其大名鼎鼎的《從0到1》中曾經(jīng)說過:對未來明確的樂觀可以讓你創(chuàng)造出想要的未來,而對未來明確的悲觀則讓人走入山寨。對于引領全球FPGA發(fā)展的賽靈思來說,他們就是以明確的樂觀創(chuàng)造出了自己想要的未來。我還記得去年應邀在北京采訪賽靈思全球戰(zhàn)略與市場營銷高級副總裁Steve Glaser時, 他所描繪的賽靈思歷經(jīng)5年的公司轉型及發(fā)展戰(zhàn)略藍圖前景一片光明。如今他們開始享用轉型的紅利了—— 除了FPGA 所服務的傳統(tǒng)市場, 一個新趨勢值得業(yè)界關注 – FPGA 在超級數(shù)據(jù)中心的主流應用在加速!

美國時間11月30日,在全球云計算領頭羊亞馬遜在拉斯維加斯所主辦的AWS re:Invent 2016盛會上, AWS CEO Andy Jassy做了主題演講,并且發(fā)布了一系列新品。其中有一個引人注目發(fā)布就是Amazon EC2 F1實例----它采用了賽靈思16nm UltraScale+ 現(xiàn)場可編程門陣列(FPGA),致力于加速基因、金融分析、視頻處理、大數(shù)據(jù)、安全和機器學習推斷等工作負載。用戶可定制FPGA硬件加速,開發(fā)者可以開發(fā)、仿真、調試、編譯等工作。Amazon EC2 F1實例是第一個用于FPGA應用加速的可編程硬件云實例, 也是賽靈思在超大規(guī)模數(shù)據(jù)中心市場應用中贏得的有一個成功案例。也是 在亞馬遜之前,百度于今年 10 月宣布,其已設計出用以加速機器學習推斷的賽靈思 UltraScale? FPGA 池。至此, 全球7家超級數(shù)據(jù)中心中的三家已經(jīng)選擇了賽靈思FPGA作為應用加速器,F(xiàn)PGA在超級數(shù)據(jù)中心漸成主流,并有可能帶來更多變革,賽靈思5年轉型漸見成效!

?

?

“從一家純FPGA企業(yè) 到ALL PROGRAMMABLE(全可編程)企業(yè)的戰(zhàn)略轉型,所帶來的是產(chǎn)品和編程模式的突破,促成了今天賽靈思在很多新興領域的快速發(fā)展,如ADAS、AR/VR、深度學習、機器視覺、無人機等等。 過去一年也是我們在數(shù)據(jù)中心市場迅速發(fā)展的一年, 取得了一系列的里程碑式成就。”賽靈思戰(zhàn)略與市場營銷高級副總裁Steve Glaser在近日接受電子創(chuàng)新網(wǎng)等媒體專訪時表示。

?

?

1、為什么數(shù)據(jù)中心需要FPGA來加速?

在加速應用方面,可以選擇的有CPU、GPU、X86CPU+Altera FPGA集成方案,為什么超級數(shù)據(jù)中心還是青睞 FPGA方案?

隨著社交媒體的快速發(fā)展,全球云數(shù)據(jù)中心日新月異,但今天的 CPU 沒能跟上機器學習、數(shù)據(jù)分析和視頻處理等各種計算密集型應用的需求步伐,加上網(wǎng)絡和存儲方面的瓶頸越來越嚴重,超大規(guī)模云、電子商務和社交網(wǎng)絡數(shù)據(jù)中心面臨越來越多面的挑戰(zhàn),例如在處理 4K 視頻、機器學習和自然語言理解時,這類數(shù)據(jù)處理需要超密集的并行處理,往往超出了傳統(tǒng) CPU 的處理能力極限。號稱“超七大”數(shù)據(jù)中心公司的阿里巴巴、亞馬遜、百度、臉書(Facebook)、谷歌、微軟和騰訊對這個問題異常敏感,在這些公司中,這些新應用往往需要數(shù)千臺加速應用服務器來支持。但基于CPU的加速服務器能效偏低,因此數(shù)據(jù)中心紛紛部署FPGA技術。

因為FPGA 是可編程的,能針對任何新型應用和算法進行硬件優(yōu)化,因而FPGA可以成為高度靈活的云計算環(huán)境的完美補充。FPGA特有的可重配置和可重編程特性,是FPGA的最大優(yōu)勢。利用動態(tài)可重配置技術,F(xiàn)PGA能在一秒之內快速切換成不同的設計方案,面對下一個工作負載進行硬件優(yōu)化。因此, FPGA 能為復雜多變的超大規(guī)模數(shù)據(jù)中心應用提供所需的靈活性、應用廣度和能效,這些是 CPU 和定制 ASIC 所無法企及的。

“我們認為FPGA在云端將成為主流應用。而AWS的發(fā)布,進一步證明了這一趨勢正在發(fā)生且勢不可擋。”Steve Glaser強調。

?

?

2、賽靈思FPGA如何滿足超級數(shù)據(jù)中心需求?

為更好地滿足數(shù)據(jù)中心(主要是超級數(shù)據(jù)中心)這一新興市場的需求,賽靈思近期宣布推出可重配置加速堆棧,初步針對三大計算密集型應用:機器學習、數(shù)據(jù)分析和流媒體視頻直播。賽靈思的可重配置加速堆疊方案不僅可最大化加速器利用率,降低總擁有成本,而且能夠提供--比x86服務器CPU高40倍、比其它FPGA競爭方案高出2-6倍的計算效率。

借助這個新型的、用于數(shù)據(jù)中心工作負載加速的可重配置加速堆棧,賽靈思期望加速 FPGA 在數(shù)據(jù)中心中的更廣泛應用。該產(chǎn)品專為世界最大的“超七大”數(shù)據(jù)中心而設計。賽靈思的戰(zhàn)略是既要充分利用 FPGA 的靈活性、性能和計算效率,同時又要讓該技術隨著業(yè)務需求變化易于開發(fā)、部署和演進。

Steve Glaser 表示“通過和像百度、亞馬遜這樣公司的密切合作,在過去很多年里我們學到了很多他們在應用我們產(chǎn)品和技術的時候遇到的一些障礙,以及他們在開發(fā)和部署的時候遇到的挑戰(zhàn)。于是,我們就把這些所學都結合到我們新推出的可重配置加速堆棧當中。我們相信現(xiàn)在我們面臨著前所未有的需求,而且已經(jīng)有能力來加速賽靈思的FPGA在超大規(guī)模數(shù)據(jù)中心中的主流應用。”

賽靈思可重配置加速堆棧: 解決超級數(shù)據(jù)中心發(fā)展最快的三種工作負載,賽靈思針對超大規(guī)模數(shù)據(jù)中心領域發(fā)展最快的三種工作負載推出該加速堆棧戰(zhàn)略。其一是機器學習,其作為底層算法和新應用而興起,不斷幫助改善廣告宣傳、客戶互動和新的客服。其二是高清視頻流,尤其是在游戲即服務市場。在這個市場中視頻編解碼加速要求的計算性能超過了標準的 x86 CPU 所提供的性能水平。其三,超大規(guī)模應用中廣泛使用的 SQL 查詢加速。

據(jù)介紹,專為云級應用而設計的最新賽靈思可重配置加速堆棧, 為應用開發(fā)人員和平臺設計人員在云級部署時全面發(fā)揮賽靈思 FPGA 的優(yōu)勢,提供了最快的開發(fā)和部署途徑。該堆棧包括庫、框架集成以及附帶部署參考設計的開發(fā)板,支持 OpenStack,并提供符合業(yè)界標準的用戶體驗。

大家可以先看看賽靈思的可重配置加速堆棧介紹

“賽靈思的方案不僅可最大化加速器利用率,降低總擁有成本,而且能夠提供比其它FPGA競爭方案高出2-6倍的計算效率。”賽靈思云計算戰(zhàn)略市場開發(fā)總監(jiān)Andy Walsh指出。

?

?

?

?

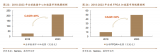

“上圖是一個對比例子,分別完成機器學習數(shù)據(jù)分析。共有兩個方案,第一個方案是用CPU,方案二是用CPU+FPGA加速器方案。這兩個方案總體性能一致,方案A用CPU來加速,但和方案二比它的效率要低很多。方案2用1個服務器再加上16個低功耗FPGA,就能夠達到方案1 24個至強處理器的性能。而它的成本只有1/10,占用空間只有1/10,它的功耗也只有1/10!”Steve 強調。

?

?

據(jù)介紹,專為云級應用而設計的最新賽靈思可重配置加速堆棧, 為應用開發(fā)人員和平臺設計人員在云級部署時全面發(fā)揮賽靈思 FPGA 的優(yōu)勢,提供了最快的開發(fā)和部署途徑。該堆棧包括庫、框架集成以及附帶部署參考設計的開發(fā)板,支持 OpenStack,并提供符合業(yè)界標準的用戶體驗。它不僅可最大化加速器利用率,降低總擁有成本,而且能夠提供比其它FPGA競爭方案高出2-6倍的計算效率。

?

?

Andy還結合實例對比了賽靈思可重配置加速堆棧方案和其他方案。

?

?

“ 橫軸是應用廣度,也就是加速器能夠非常好的來加速多少應用。縱軸是加速器利用率,也就是加速器有多靈活,性能有多優(yōu)越,可以進行多少池化的部署以及隨時保持全力運轉并且空置的情況。在橫軸,我們看最遠端的是賽靈思的FPGA,因為它是可以編程的,而且可以優(yōu)化,可以進行重新配置。”Andy強調,“在另一端GPU的利用率也不錯,但它不能夠編程優(yōu)化,而且也不能進行重新配置。定制ASIC與它類似,例如谷歌的GPU可以用來執(zhí)行某一項任務時表現(xiàn)非常好,但它的應用廣度遠遠不能滿足超大規(guī)模數(shù)據(jù)中心的要求。”

而在中間的就是英特爾的CPU+FPGA集成方案,“英特爾的至強處理器很有優(yōu)勢,把它和FPGA集成也有很多局限性,尤其是在功耗密度方面比如能夠實現(xiàn)這樣封裝的FPGA類似很有限,只能是一些中小型FPGA,這樣方只能解決一些中小型加速問題。”他強調,“它另外還有一個非常重要局限是跟賽靈思FPGA、GPU以及定制的ASIC相比---這些器件都非常容易進行池化(FPGA的池化配置,也就是指有很多個FPGA在一個單一的節(jié)點或幾個節(jié)點作為一個集合來運行。),但要把芯片中的一個非常小的元素實現(xiàn)規(guī)模化和池化,按照1:1的封裝比例是非常困難的。”

?

這個圖縱軸是加速器利用率,橫軸是計算效率(性能/功耗)以數(shù)據(jù)中心最重要的工作負載機器學習和推斷來考核。賽靈思FPGA在推斷導向精度方面效率很高,Altera的FPGA也有高的利用率但是它的計算效率要低于賽靈思的FPGA。為什么會出現(xiàn)這樣的情況?這就要從兩家公司DSP的架構定位說起了。

3、賽靈思FPGA贏在DSP架構、內存和工藝!

Steve Glasev強調在開發(fā)下一代DSP內核的時候,賽靈思定義了一種高效的DSP內核,賽靈思的 DSP48E2 設計用于在一個時鐘周期內高效地完成一個乘法累加算法 , 多達 18x27 位的乘法和多 達 48 位的累加,如下圖所示。

?

?

使用 MACC 模式的 DSP Slice

在運行 INT8 深度學習時,較寬的 27 位寬自然占有優(yōu)勢。在傳統(tǒng)應用中,預加法器一般用于高效實現(xiàn) (A+B) x C 計算,但這類計算在深度學習應用中很少見。將 (A+B) x C 的結果拆分為 A x C 和 B x C,然后在獨立的 數(shù)據(jù)流中進行累加,使之適用于典型深度學習計算的要求。

對 INT8 深度學習運算來說,擁有 18x27 位乘法器很占優(yōu)勢。乘法器的輸入中至少有一個必須為最小 24 位,同時進位累加器必須為 32 位寬,才能在一個 DSP Slice 上同時進行兩個 INT8 MACC 運算。27 位輸 入能與 48 位累加器結合,從而將深度學習求解性能提升 1.75 倍(1.75:1 即為 DSP 乘法器與 INT8 深度 學習 MACC 的比率)。其他廠商如Altera所提供的 FPGA 在單個 DSP 模塊中只提供 18x19 乘法器,DSP 乘法器與 INT8 MACC 之比僅為 1:1。

“Altera早做下一代DSP開發(fā)的時候,本來它的DSP定點效率就要低于賽靈思,它后來做出的決定使得它比原來落后賽靈思的差距又擴大了,比賽靈思的效率低了100%,所以在8位一個周期里我們可以操作運算兩次,而它只能一次,所以在DSP架構方面,賽靈思的比它的效率提升兩倍,但實際上我們最高效率可以比它大6倍,所以除了這個DSP以外,我們還有其他兩個優(yōu)勢。”Steve 表示,“在我們存儲器層級上,我們引入一個XRAM架構,另外一個優(yōu)勢是我們的工藝領先Altera一代。”

4、深度學習我最強!

今年以來,由于涉及到人工智能,深度學習變得炙手可熱,深度學習是機器學習研究中的一個新的領域,其動機在于建立、模擬人腦進行分析學習的神經(jīng)網(wǎng)絡,它模仿人腦的機制來解釋數(shù)據(jù),例如圖像,聲音和文本。深度學習的是通過多層神經(jīng)網(wǎng)絡來實現(xiàn)的,通過組合低層特征形成更加抽象的高層表示屬性類別或特征,以發(fā)現(xiàn)數(shù)據(jù)的分布式特征表示。

得益于全球科技界在生物識別、數(shù)據(jù)處理領域的突破,深度學習也獲得了極大發(fā)展,1962年Hubel和Wiesel通過對貓視覺皮層細胞的研究,提出了感受野(receptive field)的概念,1984年日本學者Fukushima基于感受野概念提出的神經(jīng)認知機(neocognitron)可以看作是卷積神經(jīng)網(wǎng)絡的第一個實現(xiàn)網(wǎng)絡,也是感受野概念在人工神經(jīng)網(wǎng)絡領域的首次應用。

卷積神經(jīng)網(wǎng)絡(CNN)是人工神經(jīng)網(wǎng)絡的一種,已成為當前語音分析和圖像識別領域的研究熱點。它的權值共享網(wǎng)絡結構使之更類似于生物神經(jīng)網(wǎng)絡,降低了網(wǎng)絡模型的復雜度,減少了權值的數(shù)量。該優(yōu)點在網(wǎng)絡的輸入是多維圖像時表現(xiàn)的更為明顯,使圖像可以直接作為網(wǎng)絡的輸入,避免了傳統(tǒng)識別算法中復雜的特征提取和數(shù)據(jù)重建過程。卷積網(wǎng)絡是為識別二維形狀而特殊設計的一個多層感知器,這種網(wǎng)絡結構對平移、比例縮放、傾斜或者共他形式的變形具有高度不變性。

?

?

?

?

在卷積神經(jīng)網(wǎng)絡(CNN)領域,目前用的最多的也是賽靈思的FPGA!Steve表示賽靈思FPGA獨特的DSP架構讓其特別適合完成多級卷積神經(jīng)網(wǎng)絡,例如已經(jīng)估值超過10億的深鑒科技就是利用賽靈思的FPGA提升機器學習推斷效率。

“他們主要是做三項工作,第一項是專注神經(jīng)系統(tǒng)模型的訓練,也就是去除冗余。第二是把精簡過的模型又進一步壓縮使得它變得更小,運行的時候能提高效率。第三個非常重要,這讓他們的研究成果位于業(yè)界尖端 ,就是如何讓一些精度降低的數(shù)據(jù)在運營時不會影響到模型的精確性。這個精度降低的數(shù)據(jù)類型對于大規(guī)模機器學習有非常大的影響。”Andy強調,“這些成果和賽靈思的解決方案非常相關,因為最終研究結果表明,這種加速效果在機器學習推斷方面甚至超過了GPU!這個成果也在Hot chips大會上發(fā)布了!”

?

?

而從亞馬遜F1計算實例的客戶來看,也多是和機器學習相關,“我們在亞馬遜彈性計算云(EC2)上實現(xiàn)了FPGA即服 務(FPGA-as-a-Service) 在每個F1實例計算池上可配置多達8個FPGA 數(shù)據(jù)分析、視頻、安全、機器學習。”Andy指出。

?

?

計劃采用F1實例的企業(yè)通過FPGA獲得的效率大幅提升,例如edico genome是做個體基因測序診斷的,通常只要幾小時就可以做一些健康檢查來檢測出基因缺陷,用于支持治療尤其是新生兒的治療。基因測序需要很多不同的計算,所以FPGA非常合適。

“NGCODSC是一家規(guī)模非常小的公司,但是取得了非常驚人的成就,這給我們的啟發(fā)是小公司如何充分利用全球最大的云資源來加速在市場的發(fā)展。”Andy補充說。

?

?

據(jù)介紹,賽靈思可重配置加速堆棧有三個層次,第一是平臺開發(fā),在平臺層面首先有一個開發(fā)板,可以進行非常迅速的評估、開發(fā)和對標,同時這個開發(fā)板也可以作為一個設計參考,還可以作為一個生產(chǎn)板,支持以云為基礎的開發(fā)環(huán)境。

第二層是應用層,針對關鍵負載如機器學習、數(shù)據(jù)分析和視頻轉碼進行優(yōu)化,賽靈思進行框架集成,選取一些普及率非常高的框架,例如機器學習領域的Caffe,可以進行深節(jié)點庫和Caffe集成,視頻轉碼的框架是FFMPEG。這個應用層還集成了SQL框架。

第三層是配置層,在Openstack已經(jīng)成為超大規(guī)模數(shù)據(jù)中心管理平臺的事實標準下,賽靈思的可重配置堆棧也有支持Openstack的套件。

“對于應用的開發(fā)者來說,他們只要有框架可以使用就好,他們不需要去研究這個平臺是什么樣的設計,他們只希望有非常簡單易用效率非常高的框架就好,這也是我們可重配置加速堆棧的設計目的。”Andy強調。

他以機器學習為例來講解賽靈思可重配置加速堆棧的使用---首先是拿到機器學習一個框架,然后對它進行修改,包括它有一個編譯選項可以用于賽靈思的深度神經(jīng)網(wǎng)絡。這個深度神經(jīng)網(wǎng)絡可以執(zhí)行像圖像識別,還有比較機械性的機器學習內容,深度神經(jīng)網(wǎng)絡又和我們數(shù)據(jù)函數(shù)庫進行合作,在GEMM這個庫里,所有這些都可以為開發(fā)者提供支持。“我們的可重配置加速堆棧并不是一個成套的交鑰匙工程,而是可以幫助所有超大規(guī)模數(shù)據(jù)中心企業(yè)用他們自己的架構來管理他們要做的工作。他們會對我們的開發(fā)板進行修改,最后來制成自己的客戶板。”Andy指出。“他們也會在我們的庫里再加上他們自己機器學習的應用。當然除了我們的框架外,他們還可以使用不同的框架,比如谷歌青睞tenserflow,亞馬遜喜歡Maxnet等等,實際上我們替他們先完成80%的工作,還有20%是有待他們優(yōu)化、細化,來實現(xiàn)自己定制化的目的。”

5、Steve Glaser: 加速賽靈思FPGA在超級數(shù)據(jù)中心中的主流應用

Steve Glasev認為FPGA未來在超級數(shù)據(jù)中心將成主流應用,尤其是及機器學習方面,在這方面GPU強在訓練,而FPGA強在推斷。“從去年開始,大家開始理解機器學習訓練看重的是浮點運算,需要非常高的性能,而且是高功耗計算,這個是GPU非常擅長的。但是一旦大規(guī)模部署訓練模型,就必須要大幅度的提高效率,需要新的推斷引擎來大大提升效率,比如3到4倍,同時還要最小限度損失精確性這就是FPGA的強項所在了。”他強調,“未來至少95%的機器學習的計算都是用于推斷,只有不到5%是用于對模型訓練,這是兩者的區(qū)別。”

“目前,F(xiàn)PGA在數(shù)據(jù)中心應用最大的瓶頸就是在采用方面的便利程度,因為很多的應用開發(fā)者非常希望能夠在自己最喜歡的框架下進行編程,所以我們也推出了可重配置加速堆棧,這是一個開端,但我們還沒有完全達到自己的目的。我們已經(jīng)知道市場的需求是什么,大家已經(jīng)開始知道怎么動手來做了,這是好的開始。”他表示。

另外,還有個趨勢,除Amazon EC2 F1實例之外,AWS還宣布了FPGA開發(fā)者亞馬遜機器映像(FPGA Developer Amazon Machine Image(AMI))開發(fā)工具,AMI為包括賽靈思Vivado? Design Suite和Vivado許可證在內的開發(fā)工具和腳本預先構建,這意味著未來FPGA開發(fā)可以架在云端了!開發(fā)者以后可以省去很多l(xiāng)icense費用,這樣一來,未來甚至可以把ASIC原型驗證也搬到云端?

大家以腦洞大開一下想象FPGA未來如何改變我們的生活?

電子發(fā)燒友App

電子發(fā)燒友App

評論