相信很多編程新手村的同學(xué)們都會(huì)有一個(gè)疑問:C 語(yǔ)言如何調(diào)用函數(shù)的呢?局部變量的作用域?yàn)槭裁磧H限于函數(shù)內(nèi)?這個(gè)調(diào)用不是指C 語(yǔ)言上的函數(shù)調(diào)用的語(yǔ)法,而是在內(nèi)存的視角下,函數(shù)的調(diào)用過程。本文將從C 語(yǔ)言

2020-12-11 16:21:13 3432

3432 如果需要在C語(yǔ)言調(diào)用系統(tǒng)指令,經(jīng)常使用system函數(shù),操作簡(jiǎn)單方便,很容易理解。

2022-09-06 14:50:32 415

415 C語(yǔ)言使用函數(shù)調(diào)用,我們?cè)偈煜げ贿^了,但是函數(shù)調(diào)用在內(nèi)存中究竟發(fā)生了什么真的清楚嗎?只有搞清楚內(nèi)存里的內(nèi)幕,才算完全搞懂函數(shù)的調(diào)用。

2022-09-07 11:47:55 654

654 現(xiàn)在編寫一個(gè)簡(jiǎn)單的應(yīng)用程序,提示用戶輸入整數(shù),通過移位的方式將其與 2 的幕 (21?2?) 相乘,并用填充前導(dǎo)空格的形式再次顯示每個(gè)乘積。輸入-輸出使用 C++。匯編模塊將調(diào)用 3 個(gè) C++ 編寫的函數(shù)。程序?qū)⒂?C++ 模塊啟動(dòng)。

2022-10-11 09:52:20 672

672 學(xué)習(xí)spinal HDL還需要學(xué)習(xí)對(duì)應(yīng)的Scala語(yǔ)言,但是spinal HDL直接貼近硬件編程,不知道對(duì)于學(xué)習(xí)spinal HDL有什么好的建議?

2024-01-21 11:11:57

unsigned是什么意思?signed是什么意思?HDL語(yǔ)言中的unsigned與signed的主要區(qū)別是什么?

2021-09-24 07:02:38

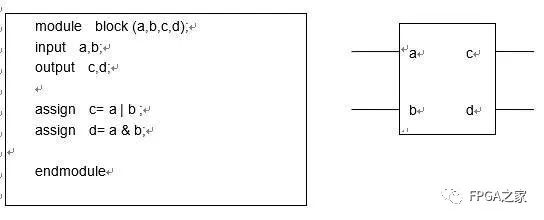

在C語(yǔ)言里面我們可以用for循環(huán)反復(fù)串行調(diào)用某個(gè)函數(shù)N次,那么在Verilog中能否和C語(yǔ)言一樣,定義一個(gè)值之后,能夠并行生成這么多的模塊并調(diào)用,比如說我寫了一個(gè)子模塊XX(input,output

2014-08-13 15:44:26

編寫keil文件時(shí),怎么在一個(gè)主函數(shù)中編寫多個(gè).c文件,進(jìn)行調(diào)用。

2015-07-10 17:08:24

如何用C語(yǔ)言編寫MB88347的程序

2020-08-11 20:00:04

Verilog HDL語(yǔ)言100例詳解希望對(duì)大家有所幫助

2016-09-01 15:58:09

嵌入式開發(fā)Verilog教程(二)——Verilog HDL設(shè)計(jì)方法概述前言一、Verilog HDL語(yǔ)言簡(jiǎn)介1.1 Verilog HDL語(yǔ)言是什么1.2前言在數(shù)字邏輯設(shè)計(jì)領(lǐng)域,迫切需要一種共同

2021-11-08 09:30:31

Verilog HDL語(yǔ)言有什么優(yōu)越性Verilog HDL語(yǔ)言在FPGA/CPLD開發(fā)中的應(yīng)用

2021-04-23 07:02:03

的復(fù)雜性可以介于簡(jiǎn)單的門和完整的電子數(shù)字系統(tǒng)之間。數(shù)字系統(tǒng)能夠按層次描述,并可在相同描述中顯式地進(jìn)行時(shí)序建模。Verilog HDL 語(yǔ)言具有下述描述能力:設(shè)計(jì)的行為特性、設(shè)計(jì)的數(shù)據(jù)流特性、設(shè)計(jì)的結(jié)構(gòu)

2020-11-30 19:03:38

,用這種語(yǔ)言編寫的模型能夠使用Ve r i l o g仿真器進(jìn)行驗(yàn)證。語(yǔ)言從C編程語(yǔ)言中繼承了多種操作符和結(jié)構(gòu)。Verilog HDL提供了擴(kuò)展的建模能力,其中許多擴(kuò)展最初很難理解。但是

2018-07-03 05:19:30

Verilog HDL硬件描述語(yǔ)言

2013-01-13 14:40:20

如何在一個(gè)module中調(diào)用另一個(gè)module中的reg變量,是否可以調(diào)用wire變量?

2016-08-04 11:39:13

Verilog_HDL硬件描述語(yǔ)言 FPGA的資料

2013-02-26 14:03:42

如上!arm中編寫程序?qū)崿F(xiàn)串口通訊,用c語(yǔ)言編寫。請(qǐng)大神指教!

2014-05-15 16:48:59

labview里可以調(diào)用其他語(yǔ)言的驅(qū)動(dòng)嗎,用delpgi編寫的

2008-11-04 21:12:02

verilog+hdl硬件描述語(yǔ)言 初學(xué)者的福音 幫助廣大初學(xué)者步入此行

2013-08-12 23:47:12

Verilog HDL 的特點(diǎn)Verilog HDL 語(yǔ)言不僅定義了語(yǔ)法,而且對(duì)每個(gè)語(yǔ)法結(jié)構(gòu)都定義了清晰的模擬、仿真語(yǔ)義。使用這種語(yǔ)言編寫的模型可以方便地使用 Verilog 仿真器進(jìn)行驗(yàn)證

2018-09-18 09:33:31

和運(yùn)算符2.3.1 標(biāo)志符2.3.2 數(shù)據(jù)類型2.3.3 模塊端口2.3.4 常量集合2.3.5 運(yùn)算符和表達(dá)式2.4 Verilog HDL語(yǔ)言的描述語(yǔ)句2.4.1 結(jié)構(gòu)描述形式2.4.2 數(shù)據(jù)流描述

2012-04-24 09:23:33

郁悶了,表示只看過VHDL語(yǔ)法但沒寫過。暫且不說VHDL模塊的內(nèi)容,我應(yīng)該如何在測(cè)試平臺(tái)中例化它并對(duì)它進(jìn)行測(cè)試呢?稍微查了一下,其實(shí)很簡(jiǎn)單,只要把VHDL中的組件名、端口統(tǒng)統(tǒng)拿出來,按照verilog

2018-07-03 12:58:49

郁悶了,表示只看過VHDL語(yǔ)法但沒寫過。暫且不說VHDL模塊的內(nèi)容,我應(yīng)該如何在測(cè)試平臺(tái)中例化它并對(duì)它進(jìn)行測(cè)試呢?稍微查了一下,其實(shí)很簡(jiǎn)單,只要把VHDL中的組件名、端口統(tǒng)統(tǒng)拿出來,按照verilog

2018-07-09 01:14:18

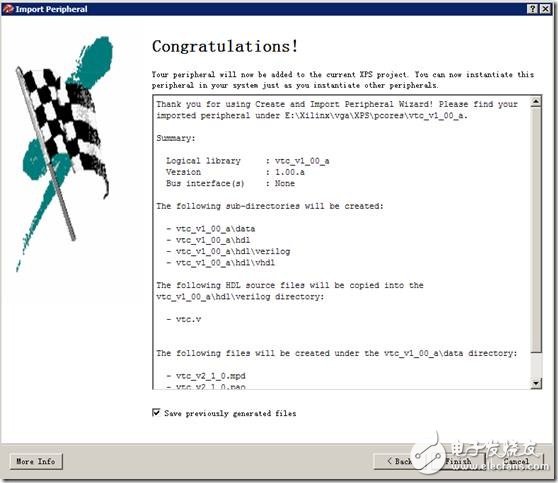

大家好,快速問題:有沒有辦法只使用XPS連接RocketIO和Microblaze軟核處理器用于virtex4 FGPA?我只是沒有看到RocketIO的IP阻止。如果沒有,連接它們的最簡(jiǎn)單方法是什么?

2020-06-18 16:11:48

你好,誰(shuí)能給我一個(gè)關(guān)于如何在XPS中使用axi_hwicap的描述?我想將它與Microblaze和Spartan6-lx45設(shè)備一起使用。什么是來自axi_hwicap的Instanz的Pin

2019-07-03 06:25:34

您好Xilinx社區(qū),我對(duì)使用SmartXplorer方法試圖改善設(shè)計(jì)時(shí)間感興趣。我似乎能夠在命令行工具上找到大量信息,并且我了解如何從命令行運(yùn)行程序等。但是,我似乎無(wú)法找到的是如何在XPS項(xiàng)目

2018-10-17 14:14:28

本文將介紹如何在PS中調(diào)用Zynq內(nèi)部的XADC模塊進(jìn)行片內(nèi)溫度和電源電壓測(cè)量。先了解XADC的相關(guān)知識(shí),再通過實(shí)例體會(huì)XADC的用法,學(xué)習(xí)XADC API函數(shù)的使用。XADC介紹XADC中文全稱

2021-12-27 06:18:43

大家好!我是新手,想問下如何在labview中調(diào)用Matlab程序呢?謝謝

2012-05-05 17:10:47

請(qǐng)問如何在labview中調(diào)用matlab的小波分析工具箱?

2011-03-30 14:53:56

大家好,想問如何在mixly中調(diào)用DF的激光粉塵傳感器,好像mixly中沒有粉塵傳感器的應(yīng)用模塊?

2020-07-15 05:26:29

是5位模式。我決定編寫一個(gè)代碼來生成值,而不是在LCD上看到它我會(huì)創(chuàng)建一個(gè)文本文件并將結(jié)果寫入該文件。任何人都可以告訴我如何在verilog中編寫代碼,這將允許我給出一個(gè)特定的頻率,以便我可以繞過信號(hào)發(fā)生器的使用并在代碼中輸入各種頻率值并獲得不同的結(jié)果?謝謝

2019-10-29 09:40:37

如何在應(yīng)用程序中調(diào)用ROM bootlaoder

2016-06-13 11:47:27

輸出)。如何在我的C代碼中編寫寫入GPIO的代碼,以便我可以捕獲數(shù)據(jù)以存儲(chǔ)在寄存器中,同時(shí)還可以在Chipscope上查看它?我已經(jīng)設(shè)置了Chipscope,并且能夠在執(zhí)行LED測(cè)試時(shí)查看SDK中的外圍設(shè)備測(cè)試中的數(shù)據(jù)線。我是嵌入式設(shè)計(jì)和MicroBlaze的新手,所以任何人都可以獲得的幫助將不勝感激。

2019-10-25 09:10:48

最近在學(xué)習(xí)labview調(diào)用DLL文件的方法,目前已經(jīng)知道如何使用VI生成DLL文件供labview調(diào)用,現(xiàn)在想學(xué)習(xí)使用C語(yǔ)言或是C++編程形成DLL文件,以實(shí)現(xiàn)labview調(diào)用。 尋求C語(yǔ)言編寫

2015-09-07 11:09:49

Verilog模型有哪幾種?Verilog HDL模型是由哪些模塊構(gòu)成的?如何用Verilog HDL語(yǔ)言描述D型主從觸發(fā)器模塊?

2021-10-19 08:36:32

HDL發(fā)展?fàn)顩r是怎樣的?常見的幾種代表性的HDL語(yǔ)言硬件描述語(yǔ)言HDL得未來發(fā)展

2021-04-28 06:44:25

正弦振蕩用verilog HDL如何編寫

2016-04-15 22:00:31

verilog HDL語(yǔ)言

2017-06-06 23:43:36

匯編調(diào)用C1、用c編寫函數(shù) int jc(int n),其功能是返回n!,保存為1c.c,編寫匯編程序1s.S,調(diào)用jc函數(shù),計(jì)算5!,并將結(jié)果存入0x20009000處。答案:(1)C語(yǔ)言int jc(int n){int i,ans=1;for(i=1;i

2021-12-20 07:59:23

)領(lǐng)域中的一種半定制電路而出現(xiàn)的,既解決了定制電路的不足,又克服了原有可編程器件門電路數(shù)有限的缺點(diǎn)。HDL硬件描述語(yǔ)言(HDL)是一種用來設(shè)計(jì)數(shù)字邏輯系統(tǒng)和描述數(shù)字電路的語(yǔ)言,常用的主要有VHDL、Verilog HDL、System Verilog 和 System C。VHDL是一種用于電路設(shè)計(jì)的高級(jí)

2021-12-22 07:39:43

用verilog語(yǔ)言編寫PwM生成模塊

2016-05-16 13:41:22

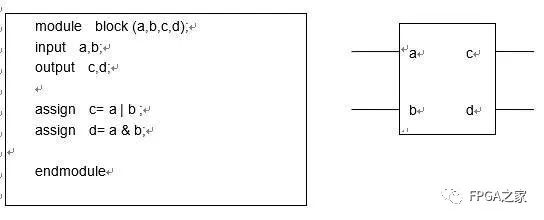

是在描述硬件,即用代碼畫圖。在 Verilog 語(yǔ)言中,always 塊是一種常用的功能模塊,也是結(jié)構(gòu)最復(fù)雜的部分。筆者初學(xué)時(shí)經(jīng)常為 always 語(yǔ)句的編寫而苦惱.

2021-07-29 07:42:25

X-HDL:軟件簡(jiǎn)介—SoftWare Description: X-HDL v3.2.55 VHDL/Verilog語(yǔ)言翻譯器

一款VHDL/Verilog語(yǔ)言翻譯器。可實(shí)現(xiàn)VHDL和Verilog語(yǔ)言的相互智能化轉(zhuǎn)化。這分別是windows、linux、solaris版本。

2006-03-25 12:00:47 355

355 采用 Verilog HDL 語(yǔ)言在Altera 公司的FPGA 芯片上實(shí)現(xiàn)了RISC_CPU 的關(guān)鍵部件狀態(tài)控制器的設(shè)計(jì),以及在與其它各種數(shù)字邏輯設(shè)計(jì)方法的比較下,顯示出使用Verilog HDL語(yǔ)言的優(yōu)越性.關(guān)鍵詞

2009-08-21 10:50:05 69

69 Verilog HDL 華為入門教程

本文主要介紹了Verilog HDL 語(yǔ)言的一些基本知識(shí),目的是使初學(xué)者能夠迅速掌握HDL設(shè)計(jì)方法,初步了解并掌握Verilog HDL語(yǔ)言的基本要素,能

2010-02-11 08:35:38 140

140 實(shí)驗(yàn)2 : 編寫一個(gè)以C 語(yǔ)言為基礎(chǔ)的DSP程序一.實(shí)驗(yàn)?zāi)康?.學(xué)習(xí)用標(biāo)準(zhǔn)C語(yǔ)言編制程序;了解常用的C語(yǔ)言程序設(shè)計(jì)方法和組成部分。2.學(xué)習(xí)編制連接命令文件

2009-03-17 00:13:13 3275

3275

摘 要:通過設(shè)計(jì)實(shí)例詳細(xì)介紹了用Verilog HDL語(yǔ)言開發(fā)FPGA/CPLD的方法,并通過與其他各種輸入方式的比較,顯示出使用Verilog HDL語(yǔ)言的優(yōu)越性。

2009-06-20 11:51:28 1857

1857

Verilog HDL語(yǔ)言實(shí)現(xiàn)時(shí)序邏輯電路

在Verilog HDL語(yǔ)言中,時(shí)序邏輯電路使用always語(yǔ)句塊來實(shí)現(xiàn)。例如,實(shí)現(xiàn)一個(gè)帶有異步復(fù)位信號(hào)的D觸發(fā)器

2010-02-08 11:46:43 4468

4468 Verilog HDL語(yǔ)言簡(jiǎn)介

1.什么是Verilog HDLVerilog HDL是硬件描述語(yǔ)言的一種,用于數(shù)

2010-02-09 08:59:33 3609

3609 VHDL和Verilog HDL語(yǔ)言對(duì)比

Verilog HDL和VHDL都是用于邏輯設(shè)計(jì)的硬件描述語(yǔ)言,并且都已成為IEEE標(biāo)準(zhǔn)。VHDL是在1987年成為IEEE標(biāo)準(zhǔn),Verilog HDL

2010-02-09 09:01:17 10317

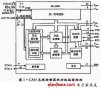

10317 在此利用Verilog HDL設(shè)計(jì)了一款CAN總線控制器,首先根據(jù)協(xié)議把整個(gè)CAN總線控制器劃分為接口邏輯管理、寄存器邏輯和CAN核心模塊3個(gè)模塊,然后用Verilog HDL硬件描述語(yǔ)言設(shè)計(jì)了各個(gè)功能模塊

2012-07-31 14:25:24 7806

7806

Verilog_HDL的基本語(yǔ)法詳解(夏宇聞版):Verilog HDL是一種用于數(shù)字邏輯電路設(shè)計(jì)的語(yǔ)言。用Verilog HDL描述的電路設(shè)計(jì)就是該電路的Verilog HDL模型。Verilog HDL既是一種行為描述的語(yǔ)言也是一種結(jié)

2012-10-08 14:48:31 0

0 電子發(fā)燒友網(wǎng)核心提示 :硬件描述語(yǔ)言HDL是一種用形式化方法描述數(shù)字電路和系統(tǒng)的語(yǔ)言。 利用這種語(yǔ)言,數(shù)字電路系統(tǒng)的設(shè)計(jì)可以從上層到下層(從抽象到具體)逐層描述自己的設(shè)

2012-10-15 10:36:08 3385

3385 本書以實(shí)例講解的方式對(duì)HDL語(yǔ)言的設(shè)計(jì)方法進(jìn)行介紹。全書共分9章,第1章至第3章主要介紹了Verilog HDL語(yǔ)言的基本概念、設(shè)計(jì)流程、語(yǔ)法及建模方式等。

2012-11-28 13:32:57 943

943 本文簡(jiǎn)單介紹在使用Verilog HDL語(yǔ)言時(shí)文件的調(diào)用問題之include使用方法介紹及舉例說明,詳見本文...

2013-01-24 14:40:42 6412

6412

Verilog HDL程序設(shè)計(jì)與實(shí)踐著重介紹了Verilog HDL語(yǔ)言

2015-10-29 14:45:47 21

21 Verilog HDL硬件描述語(yǔ)言

有需要的下來看看

2015-12-29 15:31:27 0

0 本章介紹Verilog HDL語(yǔ)言的發(fā)展歷史和它的主要能力。verilog相關(guān)教程材料,有興趣的同學(xué)可以下載學(xué)習(xí)

2016-04-25 16:09:32 14

14 本章給出了一些用Verilog HDL編寫的硬件建模實(shí)例。verilog相關(guān)教程材料,有興趣的同學(xué)可以下載學(xué)習(xí)

2016-04-25 16:09:32 25

25 本文主要介紹了Verilog HDL 語(yǔ)言的一些基本知識(shí),目的是使初學(xué)者能夠迅速掌握HDL設(shè)計(jì)方法,初步了解并掌握Verilog HDL語(yǔ)言的基本要素,能夠讀懂簡(jiǎn)單的設(shè)計(jì)代碼并能夠進(jìn)行一些簡(jiǎn)單設(shè)計(jì)的Verilog HDL建模。

2016-07-15 15:27:00 0

0 ;第4章至第6章主要討論如何合理地使用Verilog HDL語(yǔ)言描述高性能的可綜合電路;第7章和第8章重點(diǎn)介紹了如何編寫測(cè)試激勵(lì)以及Verilog的仿真原理;第9章展望HDL語(yǔ)言的發(fā)展趨勢(shì)。

2016-10-10 17:04:40 566

566 Verilog HDL硬件描述語(yǔ)言,感興趣的小伙伴們可以瞧一瞧。

2016-11-11 11:20:11 11

11 基于FPGA Verilog-HDL語(yǔ)言的串口設(shè)計(jì)

2017-02-16 00:08:59 35

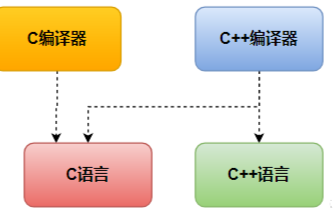

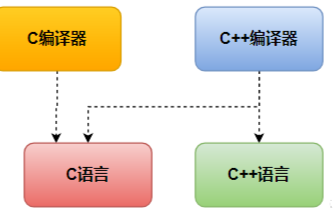

35 之間的調(diào)用 本節(jié)提供一些示例,顯示如何從C++調(diào)用C和匯編語(yǔ)言代碼,以及從C和匯編語(yǔ)言調(diào)用 C++ 代碼。其中包括調(diào)用約定和數(shù)據(jù)類型。主要包括下面內(nèi)容: 相互調(diào)用的一般規(guī)則; C++語(yǔ)言的特定信息

2017-10-19 09:24:28 2

2 基于Verilog HDL語(yǔ)言的電路設(shè)計(jì)、仿真與綜合 (一)頂層模塊 本程序采用結(jié)構(gòu)化設(shè)計(jì)方法,將其分為彼此獨(dú)立又有一定聯(lián)系的三個(gè)模塊,如圖1所示:

2017-11-28 14:36:03 16

16 關(guān)于c語(yǔ)言編寫的算法程序

2018-04-09 17:47:47 12

12 眾所周知,相比于其他編程語(yǔ)言,C語(yǔ)言在編寫嵌入式編程中有著絕對(duì)的優(yōu)勢(shì)。但它總也有缺點(diǎn)的:它的時(shí)序性比較差,不容易編寫精準(zhǔn)的延時(shí)。而在編寫嵌入系統(tǒng)驅(qū)動(dòng)程序時(shí),常常需要比較精確的軟件延時(shí),這使得C語(yǔ)言的“劣勢(shì)”暴露了出來,一般都只能通過嵌入?yún)R編的方式實(shí)現(xiàn)。

2018-05-23 16:33:00 1497

1497 本文檔的主要內(nèi)容詳細(xì)介紹的是常用模塊的Verilog HDL設(shè)計(jì)詳細(xì)資料免費(fèi)下載。

2018-10-16 11:12:54 20

20 本文主要介紹了Verilog HDL 語(yǔ)言的一些基本知識(shí),目的是使初學(xué)者能夠迅速掌握HDL 設(shè)計(jì)方法,初步了解并掌握Verilog HDL語(yǔ)言的基本要素,能夠讀懂簡(jiǎn)單的設(shè)計(jì)代碼并能夠進(jìn)行一些簡(jiǎn)單設(shè)計(jì)的Verilog HDL建模。

2019-02-11 08:00:00 95

95 Verilog HDL作為現(xiàn)在最流行的FPGA開發(fā)語(yǔ)言,當(dāng)然是入門基礎(chǔ)。

2019-02-18 14:47:00 10320

10320 Verilog HDL是一種硬件描述語(yǔ)言,以文本形式來描述數(shù)字系統(tǒng)硬件的結(jié)構(gòu)和行為的語(yǔ)言,用它可以表示邏輯電路圖、邏輯表達(dá)式,還可以表示數(shù)字邏輯系統(tǒng)所完成的邏輯功能。

2019-11-20 07:00:00 5088

5088 本文檔的主要內(nèi)容詳細(xì)介紹的是三態(tài)門原理HDL語(yǔ)言DSP和ARM總線的仿真及Modelsim使用教程資料主要內(nèi)容包括了:1 ModelSimSE的使用流程,2 一個(gè)Verilog計(jì)數(shù)器仿真詳細(xì)

2019-07-09 16:49:27 10

10 HDL和VHDL的使用比率大概是80%和20%,在中國(guó),大多數(shù)電子行業(yè)企業(yè)都采用Verilog。而模塊化的設(shè)計(jì)讓Verilog HDL語(yǔ)言具有思路清晰、邏輯關(guān)系明確、可讀性強(qiáng)等特點(diǎn),模塊化的設(shè)計(jì)在 Verilog HDL語(yǔ)法設(shè)計(jì)中也成為主流。

2020-03-25 08:00:00 4

4 Verilog HDL和VHDL是目前兩種最常用的硬件描述語(yǔ)言,同時(shí)也都是IEEE標(biāo)準(zhǔn)化的HDL語(yǔ)言。

2020-08-25 09:14:34 8605

8605 HDL是一種硬件描述語(yǔ)言,以文本形式來描述數(shù)字系統(tǒng)硬件的結(jié)構(gòu)和行為的語(yǔ)言,用它可以表示邏輯電路圖、邏輯表達(dá)式,還可以表示數(shù)字邏輯系統(tǒng)所完成的邏輯功能。 Verilog HDL和VHDL是世界上最流行

2020-08-26 09:14:31 53468

53468 HDL語(yǔ)言具有大量成熟的模塊,從某種角度說Verilog HDL更具生命力。 本文整理了一下Verilog HDL語(yǔ)言技術(shù)要點(diǎn),并分享給大家。如發(fā)現(xiàn)有錯(cuò)誤,歡迎留言指正。

2020-09-01 11:47:09 4002

4002

? ? 1C與C++相互調(diào)用 在一個(gè)嵌入式系統(tǒng)中大部分的底層和驅(qū)動(dòng)層更多的是采用C語(yǔ)言來進(jìn)行開發(fā),而上層應(yīng)用、服務(wù)更多的采用C++等高級(jí)語(yǔ)言來進(jìn)行面向?qū)ο蟮确矫娴拈_發(fā)方式,那么就存在一個(gè)上層調(diào)用底層

2021-01-18 11:05:06 2835

2835

本章講述在Verilog HDL中編寫表達(dá)式的基礎(chǔ)。 表達(dá)式由操作數(shù)和操作符組成。表達(dá)式可以在出現(xiàn)數(shù)值的任何地方使用。 4.1 操作數(shù) 操作數(shù)可以是以下類型中的一種: 1) 常數(shù) 2) 參數(shù)

2021-03-05 15:20:10 2470

2470 利用Verilog_HDL語(yǔ)言設(shè)計(jì)出租車計(jì)費(fèi)器案例。

2021-04-09 16:22:16 61

61 1、 關(guān)于如何在VHDL模塊調(diào)用一個(gè)Verilog模塊 在VHDL模塊聲明一個(gè)要與調(diào)用的Verilog模塊相同名稱的元件(component),元件的名稱和端口模式應(yīng)與Verilog模塊的名稱和輸入

2021-04-30 14:06:04 8673

8673

摘要:本節(jié)主要介紹主調(diào)模塊,以及GUI模塊的編寫。 主調(diào)模塊 終于到了主調(diào)模塊了,之前的章節(jié)主要介紹了參數(shù)計(jì)算,波導(dǎo)查值,以及HFSS封裝和調(diào)用等,所有準(zhǔn)備工作已就緒,只差一個(gè)“主體”將這些模塊調(diào)用

2021-06-30 15:23:45 1475

1475 Verilog HDL是一種以文本形式描述數(shù)字系統(tǒng)硬件的結(jié)構(gòu)和行為的硬件描述語(yǔ)言,也可描述邏輯電路圖、邏輯表達(dá)式等。Verilog HDL和VHDL是目前主流的、最受歡迎的兩種硬件描述語(yǔ)言。

2021-07-23 14:36:55 9911

9911 本文主要簡(jiǎn)單介紹php是什么語(yǔ)言編寫的?下面就跟小編一起來看看吧!

2021-07-26 09:41:07 4601

4601 除了匯編語(yǔ)言工程和C語(yǔ)言工程,許多嵌入式工程既包含C語(yǔ)言又包含匯編語(yǔ)言。由于Keil MDK的默認(rèn)啟動(dòng)代碼是用匯編編寫的,但是又是獨(dú)立的一個(gè)啟動(dòng)代碼是匯編實(shí)現(xiàn),一般其他程序都是C語(yǔ)言實(shí)現(xiàn)。 我們一起

2021-11-12 11:04:35 2469

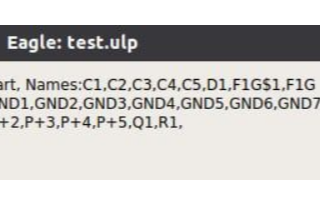

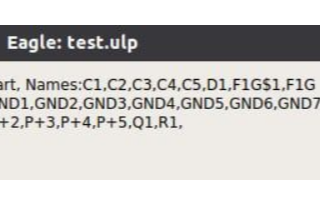

2469 在本教程中,您將學(xué)習(xí)如何在 EAGLE CAD 中編寫您的第一個(gè) ULP,以便為您的 CAD 工具添加新功能。

2022-05-10 15:29:21 1786

1786

各種硬件描述語(yǔ)言 (HDL) 在過去幾年中不斷增強(qiáng),確定哪種語(yǔ)言適合哪種設(shè)計(jì)的復(fù)雜性也隨之增加。許多設(shè)計(jì)人員和組織正在考慮是否應(yīng)該從一種 HDL 切換到另一種HDL。

2022-11-02 09:13:50 623

623 在 Vivado 中進(jìn)行HDL代碼設(shè)計(jì),不僅需要描述數(shù)字邏輯電路中的常用功能,還要考慮如何發(fā)揮Xilinx器件的架構(gòu)優(yōu)勢(shì)。目前常用的HDL語(yǔ)言有三種。 (1)VHDL 語(yǔ)言的優(yōu)勢(shì)有: 語(yǔ)法規(guī)則更加

2022-12-28 17:05:01 2375

2375 Vivado 軟件提供了HDL編寫中常用的示例,旨在幫助初學(xué)者更好地理解和掌握HDL編程,這里分享一下verilog代碼示例。

2023-05-16 16:58:06 627

627 Verilog HDL是一種用于數(shù)字系統(tǒng)設(shè)計(jì)的語(yǔ)言。用Verilog HDL描述的電路設(shè)計(jì)就是該電路的Verilog HDL模型也稱為模塊。Verilog HDL既是一種行為描述的語(yǔ)言也是一種結(jié)構(gòu)

2023-05-22 15:52:42 557

557

Verilog HDL是一種用于數(shù)字系統(tǒng)設(shè)計(jì)的語(yǔ)言。用Verilog HDL描述的電路設(shè)計(jì)就是該電路的Verilog HDL模型也稱為模塊。Verilog HDL既是一種行為描述的語(yǔ)言也是一種結(jié)構(gòu)

2023-05-22 15:53:23 531

531

Verilog是一種硬件描述語(yǔ)言(HDL),廣泛應(yīng)用于數(shù)字電路設(shè)計(jì)和硬件驗(yàn)證。在Verilog中,模塊是構(gòu)建電路的基本單元,而模塊端口對(duì)應(yīng)方式則用于描述模塊之間信號(hào)傳遞的方式。本文將介紹

2024-02-23 10:20:32 190

190

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論