見縫插圓我們昨天已經用C語言實現了,今天將實現一個見縫插針的游戲。

2022-12-05 11:02:12 463

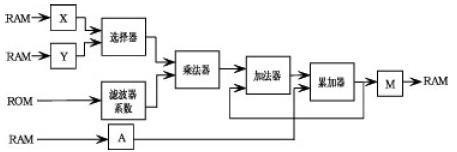

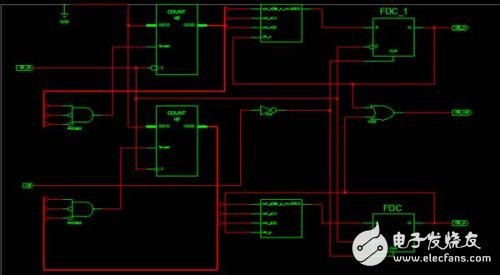

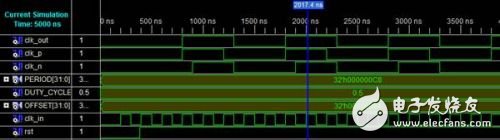

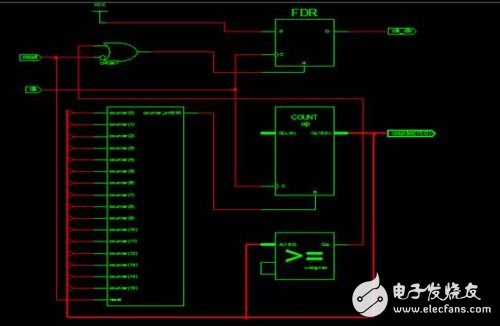

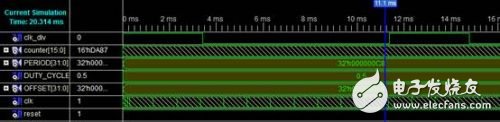

463 的OCC。像是拔牙操作一類的分頻我們今天不討論。今天討論的任意分頻器在許多的數字IC設計與FPGA面試筆試題中都有考察,所以在實(tou)現(xue)了以后做本次學習記錄,供大家參考。1. 先入為主 我們來宏觀的看本次分頻器的內容,會比較容易理解。關鍵功能點的電路如圖1所示:...

2022-02-09 07:34:15

計數器一個復位信號,使得下一個時鐘從零開始計數。以此循環下去。這種方法可以實現任意的偶數分頻。module div_6(inputi_clk,inputi_rst_n,output reg o_clk); // log2(6) = 2.5850

2013-05-01 08:44:05

我使用ADUC7061做的信號采集,現在客戶需要實現EEPROM功能來保存3-5個數據,請問如何使用C語言實現?不使用外部EEPROM 專用IC。

2024-01-12 06:56:45

C++語言實現火車排序功能.doc

2017-08-05 22:01:19

C語言實現FFT(快速傅里葉變換)

2013-10-25 21:33:41

C語言實現常用排序算法是什么?

2021-10-19 06:41:46

C語言實現數字信號處理算法

2012-08-16 23:17:38

C語言實現的泛型函數swap():交換兩個變量中的數據.

2022-01-20 07:10:47

CRC算法和c語言實現

2012-08-20 19:21:44

器的設計用Verilog+HDL語言設計分頻器和32位計數器任意分頻的verilog語言實現Verilog HDL的分頻器設計FPGA眾多分頻資料,不容錯過[hide] [/hide]`

2012-02-03 15:02:31

;humi_ge=humi_dat%10;temp_bai=temp_dat/100;temp_shi=temp_dat/10%10;temp_ge=temp_dat%10;end這個程序大神們看一下,我在ISE中不能綜合但是在Quartus2中能綜合,請問用verilog 實現任意整數的除法和取模怎么辦?

2013-10-08 08:47:49

PID控制算法的C語言實現(完整版)

2019-08-10 09:40:19

PID控制算法的C語言實現(完整版)

2020-02-06 17:08:52

PID控制算法的C語言實現(完整版)

2020-04-02 11:39:13

PID控制算法的C語言實現(完整版)

2020-05-01 11:03:55

絕大部分DBMS都支持SQL語言,LabVIEW數據庫工具包實現的實質也是基于SQL語言,它為不熟悉SQL語言的用戶把SQL語言封裝了起來,以方便他們使用。所以,我們也可以利用SQL語言實現數據庫記錄的查詢。

2014-07-01 21:25:32

等等奇數類分頻,那應該怎么辦呢?在這里,夢翼師兄為大家介紹一種可以實現任意整數分頻的方法。實現原理這種方法同樣也是利用了計數器來實現,當然我們是使用狀態機來實現的。我們首先定義分頻時鐘高電平的個數

2019-12-11 10:15:33

凹槽凸輪輪廓線的解析設計及C語言實現

2013-06-04 10:44:03

從零開始計數。以此循環下去。這種方法可以實現任意的偶數分頻。第二,奇數倍分頻:奇數倍分頻常常在論壇上有人問起,實際上,奇數倍分頻有兩種實現方法:首先,完全可以通過計數器來實現,如進行三分頻,通過待分頻時鐘

2019-06-14 06:30:00

利用變體隊列實現任意復雜數據集合傳遞(很方便),大家可以看看。原創是來自@zhihuizhou 【labview我來告訴你】實現任何LabVIEW數據類型集合的簡潔方式。我在此基礎上加了一些,方便大家理解這樣的好處。

2020-02-11 15:39:21

【摘要】:介紹了基于FPGA的任意分頻系數的分頻器的設計,該分頻器能實現分頻系數和占空比均可以調節的3類分頻:整數分頻、小數分頻和分數分頻。所有分頻均通過VHDL語言進行了編譯并且給出了仿真圖。本

2010-04-26 16:09:01

基于Proteus和C語言實現一共四個題目,有沒有人愿意嘗試一下?

2021-07-14 06:20:45

用原理圖做頂層模塊,各個分模塊怎么用verilog語言實現?求指導,求實例,求參考書!謝謝

2012-08-31 17:03:11

液晶屏漢字顯示的原理是什么?如何實現任意漢字的顯示?有哪些步驟?

2022-01-19 07:17:06

如何實現任意波形頻域變換器設計?

2022-02-15 06:30:36

如何使用C語言實現模糊PID控制?

2021-09-24 08:54:18

單片機實驗:使用c語言實現LED流水燈目的:實現一個簡單的流水燈程序仿真軟件:Portues編程軟件:KeilPortues 原理圖繪制:需要用到的模塊:單片機:AT89C51電容

2021-11-30 07:52:33

從零開始計數。以此循環下去。這種方法可以實現任意的偶數分頻。第二,奇數倍分頻:奇數倍分頻常常在論壇上有人問起,實際上,奇數倍分頻有兩種實現方法:首先,完全可以通過計數器來實現,如進行三分頻,通過待分頻時鐘

2019-07-09 09:11:47

如何利用DDS去實現任意信號波形的產生?怎樣設計信號源硬件電路?

2021-04-07 06:16:32

如何利用c語言實現中文“大”字的顯示?

2021-11-02 06:25:39

老大看到OOP編程很好,就讓我學,怎么用C語言實現OOP編程的,請大俠指點

2019-10-30 03:45:28

1 用C語言實現面向對象編程GOF的《設計模式》一書的副標題叫做“可復用面向對象軟件的基礎”,從標題就能看出面向對象是設計模式基本思想。由于C語言并不是面向對象的語言,C語言沒有直接提供封裝、繼承

2021-07-12 07:24:18

幀同步是什么工作原理?如何用VHDL語言實現幀同步的設計?

2021-04-08 06:33:59

請問如何采用CPLD和單片機實現任意波形發生器的設計?

2021-04-22 06:29:10

小白求助,求基于Proteus和C語言實現的程序和仿真

2021-10-19 06:20:34

學校要求的課程設計基于VHDL實現任意小數分頻

2014-04-24 09:09:31

如何用C語言實現直接尋址,就像匯編里面的mov 0x80,0x60

2014-05-13 16:39:17

最近在做個課題,需要用FPGA中的verilog語言實現BPSK調制,fpga不是很會,望大神指導下,急求代碼啊!謝謝

2013-03-06 18:12:36

各位大神求救啊用verilog語言實現電子鐘

2014-05-04 16:37:51

用verilog_hdl實現任意八位序列檢測

2012-08-18 10:46:48

如何使用Verilog硬件描述語言實現AES密碼算法?

2021-04-14 06:29:10

CRC算法原理及C語言實現:本文從理論上推導出CRC 算法實現原理,給出三種分別適應不同計算機或微控制器硬件環境的C 語言程序。讀者更能根據本算法原理,用不同的語言編寫出獨特

2009-09-23 23:38:50 31

31 在復雜數字邏輯電路設計中,經常會用到多個不同的時鐘信號。介紹一種通用的分頻器,可實現2~256 之間的任意奇數、偶數、半整數分頻。首先簡要介紹了FPGA 器件的特點和應用范

2009-11-01 14:39:19 78

78 用JAVA語言實現RSA公鑰密碼算法:本文闡述了公開密鑰密碼體制RSA算法的原理及實現技術。并在此基礎上,給出了JAVA語言實現的RSA算法源代碼。關鍵詞:ILSA體制;公鑰;密鑰

2010-02-10 10:27:15 58

58 用VHDL語言實現3分頻電路

標簽/分類:

眾所周知,分頻器是FPGA設計中使用頻率非常高的基本設計之一,盡管在目前大部分設計中,廣泛使用芯片廠家集成的鎖相

2007-08-21 15:28:16 5527

5527 IIR數字濾波器設計-在FPGA上實現任意階IIR數字濾波器

摘 要:本文介紹了一種采用級聯結構在FPGA上實現任意階IIR數字濾波器的方法。此

2008-01-16 09:45:39 2276

2276

用C語言實現FFT算法

/*****************fft programe*********************/#include "typedef.h" #include "math.h"

struct compx EE(struct compx

2008-10-30 13:39:56 6179

6179

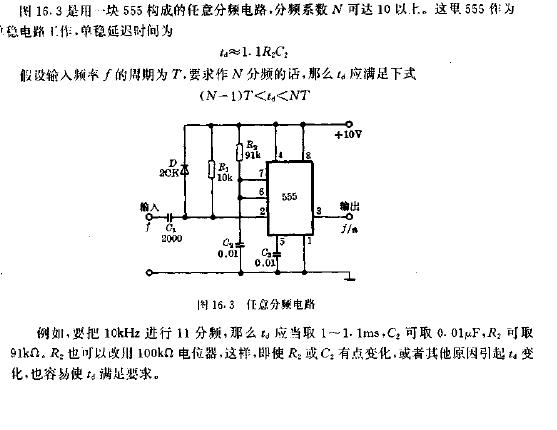

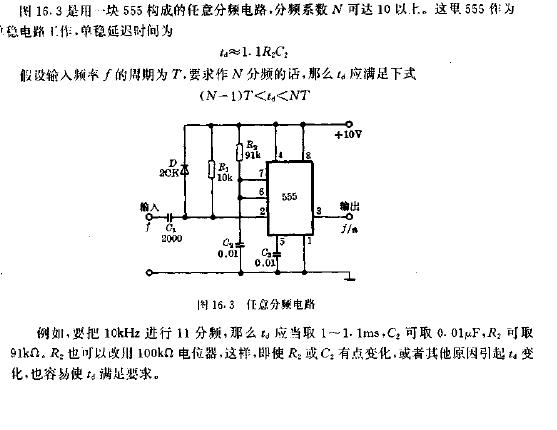

任意分頻電路圖

2009-04-09 12:02:35 2758

2758

用VHDL語言實現3分頻電路(占空比為2比1)

分頻器是FPGA設計中使用頻率非常高的基本設計之一,盡管在目前大部分設計中,廣泛使用芯片廠家集成的鎖

2009-06-22 07:46:33 7831

7831 Verilog HDL語言實現時序邏輯電路

在Verilog HDL語言中,時序邏輯電路使用always語句塊來實現。例如,實現一個帶有異步復位信號的D觸發器

2010-02-08 11:46:43 4468

4468 給出了一種基于FPGA的分頻電路的設計方法.根據FPGA器件的特點和應用范圍,提出了基于Verilog的分頻方法.該方法時于在FPGA硬件平臺上設計常用的任意偶數分頻、奇數分頻、半整數分頻

2011-11-09 09:49:33 355

355 2012-09-19 21:13:06 38

38 5 1 系列單片機中模擬串行口的C 語言實現.pdf

2015-10-29 11:34:19 4

4 Delphi教程之在DBGrid中實現任意方向查找,學習Delphi的必備資料。

2016-03-31 11:29:41 3

3 FPGA學習資料,有興趣的同學可以下載看看。

2016-04-07 14:58:43 0

0 FPGA學習資料,有興趣的同學可以下載看看。

2016-04-07 15:26:16 0

0 DSP算法的c語言實現,又需要的朋友下來看看。

2016-05-09 10:59:26 0

0 C語言實現運算器的原理 完整編程代碼C language implementation of the principle of the operator complete programming code

2016-07-08 11:33:08 4

4 用 Verilog實現基于FPGA 的通用分頻器的設計時鐘分頻包括奇數和偶數分頻

2016-07-14 11:32:47 45

45 卡爾曼濾波算法C語言實現 可以運行STM32 和 arduino上 已測試成功

2016-09-27 16:34:16 67

67 PID控制算法的C語言實現一 PID算法原理

2016-11-05 15:45:14 0

0 C++語言實現火車排序功能

2017-01-05 11:27:10 2

2 最近正在準備找工作,由于是做FPGA開發,所以verilog實現技術分頻電路是一道經常出現的題目,三分頻,五分頻電路等等;經過一下午時間總結出了一個通用電路,可以實現任意奇數分頻電路。

2017-02-09 14:21:08 2571

2571 分頻器是FPGA設計中使用頻率非常高的基本設計之一,盡管在目前大部分設計中,廣泛使用芯片廠家集成的鎖相環資源,如賽靈思(Xilinx)的DLL.來進行時鐘的分頻,倍頻以及相移。

2017-02-11 12:33:40 10916

10916 分頻器是FPGA設計中使用頻率非常高的基本設計之一,盡管在目前大部分設計中,廣泛使用芯片廠家集成的鎖相環資源,如賽靈思(Xilinx)的DLL.來進行時鐘的分頻,倍頻以及相移。

2017-02-11 13:36:36 12409

12409

DDS是從相位的概念直接合成所需波形的一種頻率合成技術。不僅可以產生不同頻率的正弦波,而且可以控制波形的初始相位。本文為大家介紹基于Verilog實現的DDS任意波形發生器。

2018-01-08 11:58:19 6454

6454

4個重要算法C語言實現源代碼

2018-06-10 08:00:00 12

12 三分頻,五分頻,七分頻等等奇數類分頻,那究竟怎么辦呢?在這里,讓我介紹一個可以實現任意整數分頻的方法,這個辦法也是同樣利用了計數器來計算,當是跟偶數分頻不一樣的地方是任意整數分頻利用了兩個計數器來實現。 設計原理 : 本

2018-06-13 11:21:48 12390

12390

分頻器是一種基本電路,通常用來對某個給定頻率進行分頻,得到所需的頻率。整數分頻器的實現非常簡單,可采用標準的計數器,也可以采用可編邏輯器件設計實現。但在某些場合下,時鐘源與所需的頻率不成整數倍關系,此時可采用小數分頻器進行分頻。

2019-11-20 07:05:00 6652

6652 論文分析了雙模前置小數分頻器的分頻原理和電路實現。結合脈沖刪除技術,提出了一種適于硬件電路實現的任意小數分頻的設計方案 ,用 VerilogHDL語 言編程 ,在 QuartusII下對 此方案進 行 了仿 真 ,并用 Cyclone 系 列 的 EP1C12Q240C8芯 片來 實 現 。

2019-08-02 08:00:00 5

5 本文檔的主要內容詳細介紹的是使用C語言實現靜態網頁的代碼免費下載。

2019-11-22 16:20:15 2

2 使用verilog語言,實現電子時鐘,包含功能時,分的調整,整點音樂和led花樣顯示

2020-07-01 08:00:00 5

5 本文檔的主要內容詳細介紹的是使用verilog語言實現數字鐘的工程文件合集免費下載。

2020-03-02 08:00:00 10

10 本文檔的主要內容詳細介紹的是使用C++語言實現的解題的實例說明。

2020-04-21 11:50:45 6

6 本文檔的主要內容詳細介紹的是如何使用Verilog語言實現持續賦值方式定義的2選1多路選擇器程序免費下載。

2020-10-28 16:54:27 14

14 本文檔的主要內容詳細介紹的是如何使用Verilog語言實現持續賦值方式定義的2選1多路選擇器程序免費下載。

2020-10-28 16:54:27 6

6 本文檔的主要內容詳細介紹的是使用單片機實現串口通訊的C語言實驗文件

2021-03-25 14:53:24 5

5 CRC校驗算法原理及c語言實現

2021-11-30 10:04:07 8

8 累加校驗和C語言實現

2021-11-29 18:06:11 10

10 這里我想主要介紹下在C語言中是如何實現的面向對象。知道了C語言實現面向對象的方式,我們再聯想下,C++中的class的運行原理是什么?

2022-10-12 09:12:27 1578

1578 今天我們將用C語言實現一個小球跳躍躲避方塊的游戲。

2022-12-08 09:06:34 702

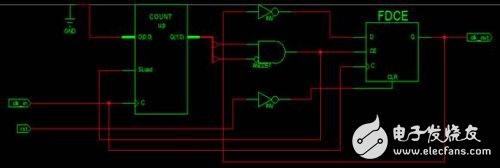

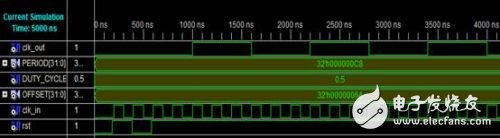

702 在verilog程序設計中,我們往往要對一個頻率進行任意分頻,而且占空比也有一定的要求這樣的話,對于程序有一定的要求,現在我在前人經驗的基礎上做一個簡單的總結,實現對一個頻率的任意占空比的任意分頻。

2023-01-05 09:33:41 1606

1606 電子發燒友網站提供《基于VHDL語言實現遠程防盜報警設計.pdf》資料免費下載

2023-11-08 14:33:11 0

0

電子發燒友App

電子發燒友App

評論