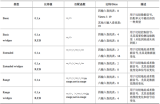

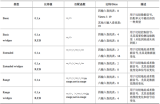

本章小結第8章 Xilinx可編程邏輯器件設計技巧8.1 概述8.2 可編程邏輯器件的時鐘設計8.3 同步設計與提高器件工作速度8.4 存儲器設計8.5 可編程邏輯器件FPGA的配置8.6

2012-02-27 14:43:30

可編程邏輯器件到底是干什么用的呢,簡單的說,就是通過重新寫程序,重新注入到這個器件中達到實現其它的功能。最常見的當屬電腦了。電腦本身除了加法,減法和簡單的邏輯運算四種。比如要是想實現一個功能讓電腦

2014-04-15 10:02:54

可編程邏輯器件FPGA/CPLD結構與應用.ppt

2017-01-21 20:34:49

可編程邏輯器件(prog ramm able logic device,PLD)件的功能不是固定不變的,它可根據用戶的需要而進行改變,即由編程的方法來確定器件的邏輯功能。可編程邏輯器件自 20 世紀

2019-02-26 10:08:08

可編程邏輯器件實驗指導書

2009-09-16 15:11:22

可編程邏輯器件是如何發展的?

2021-04-29 06:23:22

PLD比學習單片機要簡單的多,有數字電路基礎,會使用計算機,就可以進行PLD的開發。不熟悉PLD的朋友,可以先看一看可編程邏輯器件的發展歷程。開發PLD需要了解兩個部分:1.PLD開發軟件 2.PLD

2009-06-20 10:38:05

PLD可編程邏輯器件 英文全稱為:programmable logic device 即 PLD。PLD是做為一種通用集成電路產生的,他的邏輯功能按照用戶對器件編程來確定。一般的PLD的集成度很高

2021-07-22 09:05:48

` 本帖最后由 eehome 于 2013-1-5 09:47 編輯

XILINX可編程邏輯器件設計技術詳解第1章 可編程邏輯器件設計流程導論11.1 設計流程概述11.2 設計輸入和綜合

2012-04-24 09:18:46

專家都是如何使用超低功耗的復雜可編程邏輯器件(CPLD)的?從他們的嵌入式設計中的I/O子系統中學到了什么?

2021-04-08 06:31:20

為什么復雜可編程邏輯器件需要重新上電才能工作?如何去解決AVR單片機上電復位不可靠的問題?

2021-07-07 06:53:08

- 固定邏輯器件和可編程邏輯器件。一如其名,固定邏輯器件中的電路是永久性的,它們完成一種或一組功能 -- 一旦制造完成,就無法改變。另一方面,可編程邏輯器件(PLD)是能夠為客戶提供范圍廣泛的多種邏輯容量

2009-05-29 11:36:21

分享一款不錯的基于可編程邏輯器件PLD的數字電路設計方案

2021-04-30 06:34:54

摘要:介紹了可編程邏輯器件在數字信號處理系統中的應用。并運用VHDL語言對采用Lattice公司的ispLSI1032E可編程邏輯器件所構成的乘法器的結構、原理及各位加法器的VHDL作了詳細的描述

2019-06-28 06:14:11

怎么實現基于可編程邏輯器件的數字電路設計?

2021-05-06 08:36:18

本文以乘法器的設計為例,來說明采用可編程邏輯器件設計數字系統的方法。

2021-04-29 06:22:10

數字電子技術-- 可編程邏輯器件[hide][/hide]

2017-03-05 10:51:17

數字電子技術--可編程邏輯器件[hide][/hide]

2017-05-01 22:29:19

本文提出一種利用復雜可編程邏輯器件(Complex Programmable Logic Device,CPLD)設計技術[3]實現專用鍵盤接口芯片的方案。

2021-04-15 06:55:36

清華的可編程邏輯器件實驗講義cpld-2004-8-6-4

2012-08-16 17:06:20

如何選擇PLC可編程邏輯器件?

2021-04-27 06:39:03

可編程邏輯器件設計

(264頁,nlc格式)

2006-03-25 16:41:01 66

66 XC6SLX100-3FGG484C FPGA現場可編程邏輯器件 XILINX 現場可編程門陣列

2022-08-04 11:37:16

本文通過詳細介紹PLD 器件在積分式A/D 轉換器數字控制部分的設計,說明可編程邏輯器件(PLD)主要是復雜可編程邏輯器件(CPLD)在數字邏輯系統設計中良好的移植性及穩定性。

2009-08-29 10:17:43 28

28 一種基于可編程邏輯器件的等精度頻率計的設計原理、硬件組成和軟件實現關鍵詞:可編程邏輯器等精度 頻率 周期 脈寬 占空比

2009-09-07 16:05:34 31

31 可編程邏輯器件應用設計技巧100問:1. 么是.scf?答:SCF文件是MAXPLUSII的仿真文件, 可以在MP2中新建.2. 用Altera_Cpld作了一個186(主CPU)控制sdram的控制接口, 發現問題:要使得s

2009-10-01 19:00:00 41

41 可編程邏輯器件資料:Cyclone Device Handbook, Volume 1Stratix III Device Handbook, Volume 1MAX II Device Handbook

2009-12-08 16:32:17 0

0 可編程邏輯器件基礎及應用實驗指導書

《可編程邏輯器件基礎及應用》是一門側重掌握可編程邏輯器件的基本結構和原理的課程。重點是使學生掌握基于可編程

2010-03-24 14:22:46 29

29 第三十二講 可編程邏輯器件及應用第10章 可編程邏輯器件及應用10.1 概述10.1.1 PLD器件的基本結構10.1.2 PLD器件的分類10.1.3 PLD器件的優點一、

2009-03-30 16:37:51 1333

1333

【摘 要】 介紹了可編程邏輯器件的結構、優點,及其在一種高準確度A/D轉換器中的應用。設計中采用了通用陣列邏輯芯片GAL16V8。

2009-05-15 22:30:08 781

781

什么是PLD(可編程邏輯器件)

PLD是可編程邏輯器件(Programable Logic Device)的簡稱,FPGA是現場可編程門陣列(Field Programable Gate Array)

2009-06-20 10:32:32 14283

14283

基于可編程邏輯器件的數字電路設計

0 引 言

可編程邏輯器件PLD(Programmable Logic De-vice)是一種數字電路,它可以由用戶來進行編程和進行配置,利用它可以

2009-11-16 10:46:41 1473

1473

7.1 可編程邏輯器件的基本原理 7.2 可編程邏輯器件的設計技術 7.3 可編程邏輯器件的編程與配置

2012-05-23 10:46:19 142

142 Xilinx可編程邏輯器件的高級應用與設計技巧 作者:孫航;出版社:電子工業出版社 內容簡介:介紹了Xilinx器件的結構和特性;以及ISE及其輔助設計工具,嵌入式處理器的原理與設計,

2012-11-28 14:18:01 249

249 可編程邏輯器件簡介,相關詳細學習。

2016-04-26 16:55:36 0

0 可編程邏輯器件學習,壓縮包內共10篇學文檔

2016-09-02 16:54:40 38

38 可編程邏輯器件FPGA/CPLD結構與應用

2016-12-11 23:38:39 0

0 數字電子技術--可編程邏輯器件

2016-12-12 22:07:22 0

0 數字電子技術-- 可編程邏輯器件

2016-12-12 22:07:22 0

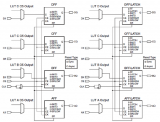

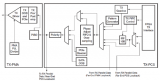

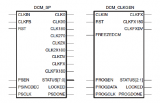

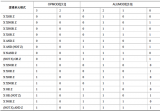

0 PicoBlaze微控制器支持最大256個輸入口和256 個輸出口,PicoBlaze與輸入和輸出有關的信號在“PicoBlaze微控制器接口信號”部分有詳細說明,包括PORT_ID[7:0]、IN_PORT[7:0]、OUT_PORT[7:0]、READ_STROBE WRITE_STROBE。

2017-02-11 05:23:03 310

310

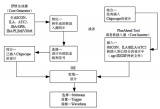

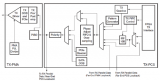

PicoBlaze微控制器實際上包含兩個部分,分別是內核KCPSM3 和指令存儲器ROM。

2017-02-11 05:26:11 354

354

通常情況下,如果對性能要求不是太高,最好是讓PicoBlaze在低頻下工作,因為它所處理的外設一般為低速設備,例如,串行通信,按鍵等。另外,低頻工作也會減少等待周期,降低系統功耗。

2017-02-11 05:29:11 622

622

1. PICOBLAZE 嵌入式系統,包括1 個8 位的方波輸出口,一個驅動兩位7 段LED 的輸出口,一個時鐘輸入和一個中斷輸入。

2017-02-11 05:34:11 572

572

我們知道,PicoBlaze微控制器只提供一個中斷輸入口,如果設計中需要多個中斷,可以在FPGA中用邏輯實現。

2017-02-11 05:59:39 379

379

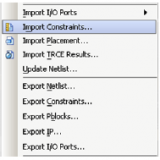

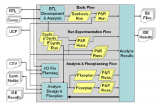

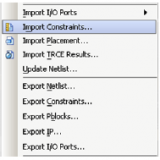

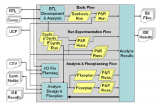

可以將綜合后網表文件導入PlanAhead,然后在PlanAhead 中完成關鍵時鐘,以及相關聯的I/O 端口的分配。

2017-02-11 06:08:00 546

546

在ISE 中可以進行時序分析,在PlanAhead 中同樣也可以進行時序分析。下面介紹用PlanAhead 進行時序分析的步驟。

2017-02-11 06:13:11 437

437

FloorPlanning 工具是PlanAhead 的一個組成部分,用它可以對FPGA 設計進行分析,首先找到設計中的時序問題或者擁塞的問題,然后再通過使用PloorPlanning 約束,以指導實現工具產生更優的結果。

2017-02-11 06:18:30 572

572

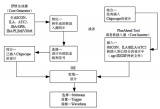

本節將簡單介紹在PlanAhead工具中如何應用ChipScope核和分析工具進行邏輯調試與驗證。先通過一個向導將ChipScope核插入設計中,選擇待測試的網線,并進行例化、連接和綜合,最后,導入布局和時序報告,產生位流文件,用ChipScope分析器進行驗證。

2017-02-11 06:24:35 678

678

設計者可以在【Clock Regions】窗口、【I/O Ports】窗口或者【Package Pins】窗口選擇一個或多個對象,或者單擊按鈕取消所有選擇,再運行【Tools】→【Clear Placement Constraints】命令

2017-02-11 06:56:38 519

519

FPGA和PCB設計人員保留一定數量FPGA引腳作為測試引腳,FPGA設計者在編寫FPGA代碼時,將需要觀察的FPGA內部信號定義為模塊的輸出,在綜合實現時再把這些信號鎖定到保留的測試引腳上,最后連接示波器或邏輯分析儀的探頭到這些測試腳進行觀測。

2017-02-11 07:11:33 561

561

ChipScope Pro 提供了多種不同功能的調試內核,通常分成三類:邏輯調試內核、誤比特率測試核和集成總線分析核。用戶根據系統的調試要求,應用不同的調試內核,方便快速地找到設計中存在的問題。

2017-02-11 07:13:07 577

577

Xilinx針對不同類型的調試IP核,提供了不同的核生成器。本節重點介紹Xilinx Core Generator Tool(Xilinx IP核生成器)所支持的ChipScope Pro調試IP核ICON、ILA、VIO和ATC2及其屬性

2017-02-11 07:14:11 761

761

雙擊【Xilinx Core Generator】,打開現有的IP核工程項目或者創建一個新的IP核工程。【View by function】→【Debug & Verification】→【ChipScope Pro】

2017-02-11 07:15:31 483

483

下面通過一個簡單8位計數器的例子,了解如何在工程中添加ChipScope Pro內核生成器的各個IP核,對FPGA內部節點和邏輯進行觀測。在該實例中,我們將調用一個ICON、一個ILA和一個VIO。

2017-02-11 07:19:40 766

766

ChipScope Pro 分析工具(Analyzer tool)直接與ICON、ILA、IBA、VIO及IBERT核相連,用戶可以實時地創建或修改觸發條件。

2017-02-11 07:25:00 1486

1486

ChipScope Pro內核插入器的文件后綴名為cdc。在ISE工程中可以創建一個新的cdc程序,也可以在實現流程中激活內核插入器。

2017-02-11 07:29:12 765

765

PlanAhead工具是Xilinx提供的一個集成的、可視化的FPGA設計工具,它可以被應用于FPGA設計過程中的不同階段,常見的應用包括用PlanAhead進行RTL源代碼的開發、I/O引腳規劃

2017-02-11 07:29:13 1702

1702

這里介紹如何用PlanAhead進行RTL代碼開發與分析。需要說明一點,本章所用的所有實例都可以在PlanAhead的安裝目錄E:\Xilinx\11.1\PlanAhead\testcases\PlanAhead_Tutorial下找到,本節使用的是source文件夾中的文件。

2017-02-11 07:34:36 618

618

PlanAhead允許導入多種不同類型的源文件,包括HDL和NGC核。在RTL編輯器中可以打開、編輯、開發RTL源文件。下面我們介紹【Sources】源文件視圖和RTL編輯器的使用。

2017-02-11 07:38:11 882

882

下面通過一個簡單的實例介紹如何創建PlanAhead項目,進行I/O規劃。

2017-02-11 07:48:11 301

301

最大化【Package Pins】,如圖10-45 所示, 和按鈕配合,完成對器件引腳的排序,如圖中我們將所有VREF 引腳排在一起,選中所有VREF 引腳,右鍵功能選擇【Set Prohibit】,禁止所有VREF 引腳的分配。

2017-02-11 07:51:11 563

563

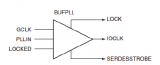

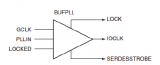

除了全局時鐘緩沖器外,Spartan-6還包含驅動高速I/O時鐘區域的時鐘緩沖器。

2017-02-11 08:39:11 1198

1198

Spartan-6的時鐘布線網絡包括由BUFGMUX驅動的全局時鐘網絡和由I/O時鐘緩沖器(BUFIO2)、PLL時鐘緩沖器(BUFPLL)驅動的I/O區域時鐘網絡。

2017-02-11 08:42:11 658

658

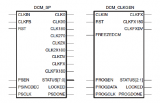

Spartan-6 CMT是一個靈活、高性能的時鐘管理模塊。它位于芯片中央、垂直的全局時鐘網絡旁。如圖2-17所示,它包含一個PLL和兩個DCM。

2017-02-11 08:43:50 727

727

Spartan-6 器件最多包含6 個CMT,12 個PLL。PLL 的主要用途是作為頻率合成器,產生更寬范圍的頻率輸出,在與CMT 中的DCM 連接時,具有良好的濾波功能。

2017-02-11 08:45:12 1145

1145

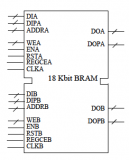

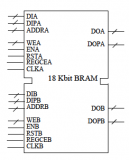

Spartan-6中的BRAM存儲18Kbit數據,能配置成兩個獨立的9Kbit BRAM或者一個18Kbit BRAM。每個RAM可以通過兩個端口尋址,也可以配置成單口RAM。BRAM包含輸出寄存器以增加流水線性能。BRAM 在器件中按列排列,其數量取決于Spartan-6 器件的容量。

2017-02-11 08:49:36 640

640

所有的Spartan-6 FPGA有高性能的可配置SelectIO驅動器與接收器,支持非常廣泛的接口標準。可以通過編程控制I/O的輸出強度、斜率以及片上終端OCT。

2017-02-11 08:53:11 6490

6490

為了適應越來越復雜的DSP運算,Spartan-6在Spartan 3A DSP模塊DSP48A 基礎上,不斷進行功能擴展,推出了功能更強大的DSP48A1 SLICE。

2017-02-11 08:53:13 992

992

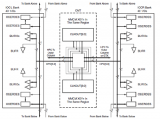

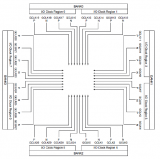

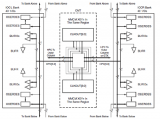

Spartan-6器件具有2或4個專用嵌入式多端口存儲器控制器模塊(MCB),實現了到4個常見存儲器標準的簡單連接:DDR3、DDR2、DDR 和LPDDR(移動DDR)。

2017-02-11 09:01:36 703

703

Spartan-6 FPGA系列為消費、汽車、無線和其他價格敏感或大批量市場,提供了低風險和低成本的串行連接解決方案。

2017-02-11 09:02:37 694

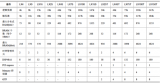

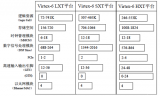

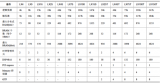

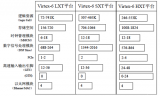

694 Spartan-6 LX平臺面向邏輯、DSP資源以及存儲模塊進行了優化,能夠以較低的功耗滿足更高的帶寬和性能需求;而Spartan-6 LXT面向邏輯、DSP以及存儲資源進行優化,同時提供低功耗3.125Gbit/s串行收發器,可以實現PCI-e、SATA等高速串行接口。

2017-02-11 09:03:36 509

509

Virtex-6是Xilinx 在2009年2月推出的新一代旗艦產品,采用了第三代Xilinx ASMBL架構、40nm 工藝,提供多達760000 個邏輯單元,為業界成本最低、功耗最低、密度最高、性能最高、帶寬最大的FPGA。

2017-02-11 09:04:30 466

466

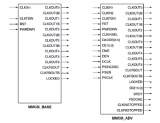

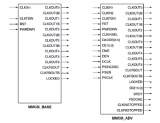

CLB是實現時序電路和組合電路的主要邏輯資源。

2017-02-11 09:05:38 549

549

為了更好的控制時鐘,Virtex-6器件分成若干個時鐘區域,最小器件有6個區域,最大器件有18個區域。每個時鐘區域高40個CLB。在時鐘設計中,推薦使用片上專用的時鐘資源,不推薦使用本地時鐘(如邏輯產生的時鐘)。

2017-02-11 09:10:11 1165

1165

除了豐富的時鐘網絡以外,Xilinx還提供了強大的時鐘管理功能,提供更多更靈活的時鐘。Xilinx在時鐘管理上不斷改進,從Virtex-4的純數字管理單元DCM,發展到Virtex-5CMT(包含

2017-02-11 09:14:01 1030

1030

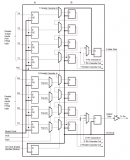

Virtex-6中嵌入BRAM,大大拓展了FPGA的應用范圍和應用的靈活性。BRAM可被配置為單端口RAM、雙端口RAM、內容地址存儲器(CAM)以及FIFO等常用存儲結構。

2017-02-11 09:16:12 974

974

為了適應越來越復雜的DSP運算,Virtex-6中嵌入了功能更強大的DSP48E1 SLICE,簡化的DSP48E1模塊如圖5-16所示。

2017-02-11 09:17:13 1391

1391

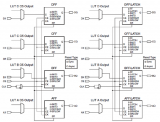

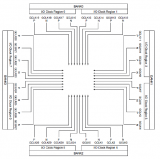

Virtex-6每個I/O片(I/O Tile)包含兩個IOB、兩個ILOGIC、兩個OLOGIC 和兩個IODELAY,如圖5-24 所示。

2017-02-11 09:21:12 2426

2426

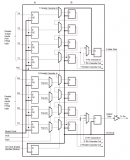

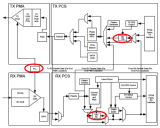

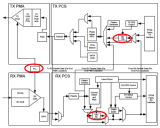

Virtex-6支持多種高速串行接口,其中高速串行模塊GTX收發器可以實現150Mbit/s~6.5Gbit/s的線速率。GTX收發器是芯片與芯片之間、板與板之間進行串行通信的首選解決方案。GTX收發器具有以下特性。

2017-02-11 09:26:11 636

636

Vrtex-6 HXT器件內的GTH模塊比GTX有更高的線速率,用它可以實現最高性能的高速串行收發器。GTH具有如下特性。

2017-02-11 09:27:41 1408

1408

時鐘布線資源具有高速、低SKEW的特點,它對系統設計非常重要,即使系統速率不高,也應該關注時鐘設計,以消除潛在的時鐘危險。

2017-02-11 09:57:13 558

558

Spartan-6的時鐘緩沖器/多路復用器(BUFG或BUFPLL)可以直接驅動時鐘輸入信號到時鐘線上,或者通過多路復用器在兩個不相關的信號甚至異步時鐘信號中切換。

2017-02-11 09:59:11 795

795

可編程邏輯器件(書皮)

2022-07-10 14:34:54 0

0 可編程邏輯器件原理、開發與應用

2017-09-19 16:04:49 19

19 可編程邏輯器件(PLD)是20世紀70年代發展起來的一種新型邏輯器件,是目前數字系統設計的主要硬件基礎。根據可編程邏輯器件結構、集成度以及編程工藝的不同,它存在以下不同的分類方法。

2020-06-10 17:52:19 26761

26761 可編程邏輯器件PLD(Programmable Logic Device)就是一種可以由用戶定義和設置邏輯功能的數字集成電路,屬于可編程 ASIC。

2020-09-04 17:02:17 2383

2383 可編程邏輯器件(PLD--ProgrammableLogic Device):器件的功能不是固定不變的,而是可根據用戶的需要而進行改變,即由編程的方法來確定器件的邏輯功能。

2021-01-21 17:04:00 33

33 可編程邏輯器件PLD課件下載

2021-08-13 10:58:22 31

31 在過去的十年中,可編程邏輯器件(PLD)市場不斷增長,對PLD的需求不斷增加。具有可編程特性且可編程的芯片稱為PLD。PLD也稱為現場可編程器件(FPD)。FPD用于實現數字邏輯,用戶可以配置集成電路以實現不同的設計。這種集成電路的編程是通過使用EDA工具進行特殊編程來完成的。

2022-03-22 12:36:24 5304

5304 電可編程邏輯器件(Electrically Programmable Logic Device,EPLD)是指采用電信號的可擦可編程邏輯器件。

2022-08-22 18:12:37 935

935 常見的可編程邏輯器件分為FPGA、EPLD(CPLD)。下面簡單介紹兩類器件的結構和區別。

2023-03-24 14:18:28 798

798

可編程邏輯器件 (Programmable Loeie Device,PLD)是一種用戶編程實現某種邏輯功能的邏輯器件,主要由可編程的與陣列、或陣列、門陣列等組成,可通過編程來實現一定的邏輯功能

2023-06-06 15:35:59 659

659

可編程邏輯器件 (Programmable Loeie Device,PLD)是一種用戶編程實現某種邏輯功能的邏輯器件,主要由可編程的與陣列、或陣列、門陣列等組成,可通過編程來實現一定的邏輯功能。

2023-06-06 15:37:45 405

405

可編程邏輯器件(Programmable Logic Device,PLD)是一類集成電路器件,可以根據用戶的需求進行編程和配置,以實現特定的邏輯功能。它們具有可編程的邏輯門、時鐘資源和互連結構,可以替代傳統的固定功能邏輯芯片,提供更靈活和可定制的解決方案。

2023-09-14 15:25:55 1108

1108 近日AMD宣布,將停產多種可編程邏輯器件,包括 XC9500XL,CoolRunner XPLA 3、CoolRunner II、Spartan II 和 Spartan 3、3A、3AN、3E、3ADSP ,以及面向商業/工業的“XC”和面向汽車“XA”產品系列。

2024-01-24 17:37:21 451

451

可編程邏輯器件是一種集成電路,具有可編程功能的特性。它們可以根據用戶的需求進行編程,從而實現不同的邏輯功能。

2024-02-26 18:24:03 576

576

電子發燒友App

電子發燒友App

評論