ISE12.2設(shè)計(jì)套件強(qiáng)化了其部分可重配置技術(shù)設(shè)計(jì)流程,并通過智能時(shí)鐘門控技術(shù)降低24% 的 BRAM 功耗。賽靈思部分可重配置技術(shù),是目前唯一經(jīng)行業(yè)驗(yàn)證的可重配置FPGA

2010-07-31 12:39:03 439

439 和軟件設(shè)計(jì)兩個(gè)方面對多重配置進(jìn)行分析,給出了多重配置實(shí)現(xiàn)的具體步驟,對實(shí)現(xiàn)復(fù)雜硬件設(shè)計(jì)工程有一定的參考價(jià)值。##本文通過硬件電路和軟件設(shè)計(jì)兩個(gè)方面對FPGA的多重配置方法進(jìn)行了詳細(xì)介紹,本文所介紹的多重配置方法靈活方便、易于操作、電路簡單,在工程中有很高的應(yīng)用價(jià)值,同時(shí)關(guān)于bit流壓縮的方法也值得參考。

2014-01-24 14:17:22 13670

13670

隨著FPGA 成為系統(tǒng)級解決方案的核心,大型、復(fù)雜設(shè)備常需要多片大規(guī)模的 FPGA。如果使用 PROM 進(jìn)行配置,需要很大的 PCB 面積和高昂的成本.

2015-02-04 11:42:27 7817

7817 上文XILINX FPGA IP之Clocking Wizard詳解說到時(shí)鐘IP的支持動(dòng)態(tài)重配的,本節(jié)介紹通過DRP進(jìn)行MMCM PLL的重新配置。

2023-06-12 18:24:03 5528

5528

AS安全模式建立完畢后,UE和gNB之間會(huì)觸發(fā)RRC重配置流程。

重配置信令流程如圖所示:

那么觸發(fā)重配置流程的目的以及重配置消息中有哪些關(guān)鍵字段呢?

1 RRC重配置流程的目的

2023-05-10 15:44:58

直接把所有電路做在一個(gè)工程中,這樣使用的FPGA芯片容量太龐大,非常昂貴,而且電路膠合控制太復(fù)雜,這時(shí)候我們可以對每種FPGA模型進(jìn)行分別生成配置文件,當(dāng)根據(jù)實(shí)時(shí)狀態(tài)現(xiàn)場更新FPGA電路。這樣就可以采用

2012-04-26 14:27:03

使用的是SPARTAN-3E的開發(fā)板,在fpga配置文件時(shí),.bit文件的下載時(shí),程序可以在線正常運(yùn)行。但使用.mcs文件配置時(shí),ISE上顯示program success,但板子上的FPGA并沒有

2015-03-16 17:05:25

引言針對需要切換多個(gè)FPGA配置碼流的場合,Xilinx公司提出了一種名為System ACE的解決方案,它利用CF(Compact Flash)存儲(chǔ)卡來替代配置用PROM,用專門的ACE控制芯片

2019-06-10 05:00:08

進(jìn)行編程。用戶可以根據(jù)不同的配置模式,采用不同的編程方式。FPGA 的使用非常靈活。目前,大部分的 FPGA 在使用時(shí)都需要外接一個(gè) EPROM 保存其程序,加電時(shí),FPGA 芯片將 EPROM 中

2018-09-06 09:11:58

FPGA都可實(shí)現(xiàn)靜態(tài)重構(gòu)。后者則是指在系統(tǒng)實(shí)時(shí)運(yùn)行中對FPGA芯片進(jìn)行動(dòng)態(tài)配置(即在改變電路功能的同時(shí)仍然保持電路的工作狀態(tài)),使其全部或部分邏輯資源實(shí)現(xiàn)在系統(tǒng)的高速的功能變換和時(shí)分復(fù)用。動(dòng)態(tài)重構(gòu)技術(shù)

2011-05-27 10:22:59

芯片實(shí)物圖

FPGA 發(fā)展歷程在 PLD 未發(fā)明之前,工程師使用包含若干個(gè)邏輯門的離散邏輯芯片進(jìn)行電路系統(tǒng)的搭建,復(fù)雜的邏輯功能實(shí)現(xiàn)起來較為困難。

為了解決這一問題,20 世紀(jì) 70 年代

2023-05-30 20:40:25

Cyclone? IV GX 收發(fā)器支持對收發(fā)器的不同部分進(jìn)行動(dòng)態(tài)重配置,而無需對器件的任何部分?jǐn)嚯姟1菊鹿?jié)提供并講解了用于動(dòng)態(tài)重配置各種模式的實(shí)例。您可以使用 ALTGX_RECONFIG

2017-11-14 10:53:11

`Xilinx FPGA入門連載17:PWM蜂鳴器驅(qū)動(dòng)之復(fù)位與FPGA重配置功能特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm1 復(fù)位

2015-10-26 12:05:15

,FPGA進(jìn)行主串模式。可是斷電之后 重啟 FPGA并沒有從PROM中自動(dòng)加載程序,這是為什么?請大家多指教哈 這問題糾結(jié)小弟兩天了........

2014-10-11 11:16:08

Xilinx PlanAhead工具資料說可以用來部分動(dòng)態(tài)重配置,我現(xiàn)在想對芯片的每一幀中每一位進(jìn)行逐位翻轉(zhuǎn)的動(dòng)態(tài)重配置,使用PlanAhead能夠?qū)崿F(xiàn)么?應(yīng)該怎么理解Planahead的部分重配置,如何應(yīng)用?希望知道的朋友告訴下,對這個(gè)有點(diǎn)迷茫。

2015-06-01 10:11:33

重配置硬件的關(guān)鍵特性,比如并行性、可定制性、靈活性、冗余性和多功能性進(jìn)行了充分的探索。在概念設(shè)計(jì)完成后,我們希望在原型中實(shí)現(xiàn)設(shè)計(jì)。為此,賽靈思 Zynq?-7000 可擴(kuò)展處理平臺(tái)成為了理想選擇。該款

2019-07-05 08:34:21

產(chǎn)生不同的電路功能。因此,FPGA的使用非常靈活。 FPGA有多種配置模式:并行主模式為一片FPGA加一片EPROM的方式;主從模式可以支持一片PROM編程多片FPGA;串行模式可以采用串行PROM編程

2016-12-13 15:22:16

產(chǎn)生不同的電路功能。因此,FPGA的使用非常靈活。 FPGA有多種配置模式:并行主模式為一片FPGA加一片EPROM的方式;主從模式可以支持一片PROM編程多片FPGA;串行模式可以采用串行PROM編程

2016-12-13 18:12:57

的USB電纜對閃存PROM進(jìn)行了編程,但之后沒有配置fpga。我錯(cuò)過了什么?下一個(gè)命令用于生成文件: bitgen -w -g StartupClk:CCLK -g Binary:yes -g

2019-05-29 12:42:35

FPGA的配置,這里不得不提一下他們和CPLD內(nèi)部存儲(chǔ)介質(zhì)的不同。CPLD由于大都是基于PROM或Flash來實(shí)現(xiàn)可編程特性,因此對他們進(jìn)行在線編程時(shí)就已將配置數(shù)據(jù)流固化好了,重新上電后還能夠運(yùn)行固有

2016-07-27 16:45:59

我用的是Spartan-3E系列的芯片。我想有兩種下載方式,方式一是通過JTAG直接給FPGA下載程序,方便調(diào)試。方式二是將程序燒到PROM里面,在上電時(shí)FPGA自動(dòng)從PROM進(jìn)行配置。現(xiàn)在的問題是

2013-10-18 10:06:47

LabVIEW,LabVIEW Real-TIme模塊和LabVIEW FPGA模塊以及PXI-7931R可重配置I/O板卡完成實(shí)時(shí)仿真,并對I/O信號實(shí)現(xiàn)精確、靈活的定時(shí)與同步。HIL仿真要求作為工業(yè)

2019-05-31 09:05:07

相當(dāng)部分的 STM32芯片都帶USB模塊,有時(shí)我們會(huì)考慮利用STM32芯片的USB模塊進(jìn)行程序代碼的下載或升級。USB協(xié)議中有專門針對設(shè)備固件升級的類協(xié)議,即可以通過DFU類協(xié)議進(jìn)行產(chǎn)品固件的加載或更新。關(guān)于STM32產(chǎn)品的DFU程序下載和升級,ST官方有相關(guān)的資料文檔。

2021-08-05 06:45:49

,以便為Microblaze實(shí)現(xiàn)不同的periferal。我已經(jīng)讀過Spartan3 FPGA支持部分重配置,但我不知道它是否支持動(dòng)態(tài)重配置,而Microblaze仍在使用中。有幫助嗎?提前致謝缺口

2019-05-14 06:28:56

你好。我在我的設(shè)計(jì)中使用了兩個(gè)FPGA(Spartan 3)。在這種情況下,我可以使用單個(gè)Config PROM將我的位文件加載到FPGA。如果是,我應(yīng)該如何連接FPGA和PROM,以便相應(yīng)的配置

2018-09-28 11:36:13

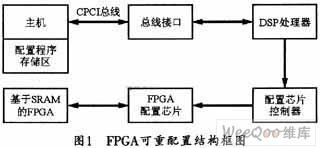

本文介紹的基于FPGA的可重配置系統(tǒng)可以在設(shè)計(jì)后期甚至量產(chǎn)階段通過重新編程以適應(yīng)標(biāo)準(zhǔn)和協(xié)議的改變。

2021-05-13 06:35:49

的靈活性和更高的性能,它正迅速成為軍事、公共安全和商業(yè)無線領(lǐng)域的事實(shí)標(biāo)準(zhǔn)。 SDR在商業(yè)領(lǐng)域日益流行的一個(gè)關(guān)鍵原因是它既能對多種波形執(zhí)行基帶處理,又能進(jìn)行數(shù)字中頻(IF)處理。中頻處理將DSP的應(yīng)用范圍

2019-07-29 07:21:01

大家好,我已經(jīng)閱讀了很多關(guān)于如何從PROM閃存和SPI閃存配置FPGA的PDF文件,但我需要知道如何使用mcs文件配置閃存本身(我知道它可以通過IMPACT完成,我知道所有步驟,但是我需要知道這些

2019-07-10 07:36:39

如何利用ST官方軟件工具DfuSe進(jìn)行相關(guān)編程操作?如何利用STM32芯片的USB模塊進(jìn)行程序代碼的下載或升級呢?

2021-11-02 06:25:28

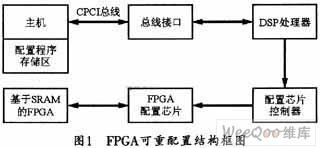

或系統(tǒng)重構(gòu)。結(jié)合對FPGA重配置方案的軟硬件設(shè)計(jì),本文通過PC機(jī)并通過總線(如PCI總線)將配置數(shù)據(jù)流下載到硬件功能模塊的有關(guān)配置芯片,從而完成配置FPGA的全過程。有誰知道,具體該怎么做嗎?

2019-08-07 06:17:30

后即可進(jìn)入bootloader。可是在某些應(yīng)用需求中,特別是成熟的產(chǎn)品中,往往不方便拆開外殼來修改Boot引腳。如何在不修改boot引腳的情況下進(jìn)入DFU模式來進(jìn)行程序升級?成為了產(chǎn)品的新需求。一、ST芯片的啟動(dòng)模式ST芯片的啟動(dòng)模式有三種。Main Flash Memory 稱為主Flas.

2021-08-10 07:02:27

你好:我正在使用三個(gè)XCF32P PROM來使用iMPACT配置XC5VLX330 FPGA。 FPGA和XCF32P PROM可以通過JTAG配置。* .mcs文件可以寫入XCF32P。但是再次上

2020-05-28 06:24:43

我試圖找出部分重配置的配置架構(gòu)。從我之前使用Virtex-5 FPGA的工作開始,幀將跨越時(shí)鐘區(qū)域的垂直切片。但是,我找不到任何類似的Virtex-7文檔。我找到的只是configuraiton指南

2020-05-29 08:54:01

隨著大規(guī)模集成電路的快速發(fā)展,系統(tǒng)設(shè)計(jì)已從傳統(tǒng)的追求大規(guī)模、高密度逐漸轉(zhuǎn)向提高資源利用率,使有限的資源可以實(shí)現(xiàn)更大規(guī)模的邏輯設(shè)計(jì)。利用現(xiàn)場可編程邏輯器件FPGA的多次可編程配置特點(diǎn),通過重新下載存儲(chǔ)

2019-08-06 07:05:37

你好我打算用xc5vlx20t。我應(yīng)該如何連接PROM,以便花費(fèi)最少的時(shí)間配置FPGA?我想更改PROM中的配置文件并重新配置電源開啟時(shí)fpga怎么樣SHOULDI呢?謝謝大衛(wèi)

2020-06-02 13:31:37

你好,我正在嘗試用.mcs文件編程我的PROM。它實(shí)際上對PROM進(jìn)行編程,但是當(dāng)我關(guān)閉電路板并按下prog引腳時(shí),沒有任何反應(yīng)。以下是詳細(xì)信息:1.董事會(huì)是定制董事會(huì),2.

2019-10-31 08:59:41

嗨,我們計(jì)劃在我們的新設(shè)計(jì)中使用兩個(gè)來自Spartan-6 famliy的FPGA(特別是XC6SLX100-3FGGI。)。我們設(shè)計(jì)的設(shè)備需要在現(xiàn)場進(jìn)行遠(yuǎn)程sw和fw升級,并采用故障安全操作

2019-05-30 10:05:15

單片機(jī)連接外部硬件看門狗后,程序下載不了,拆除硬件看門狗后,程序就可以下載了。應(yīng)該是程序下載過程中外狗一直復(fù)位單片機(jī),導(dǎo)致程序下載不了。有什么方法能使連接外部看門狗還能進(jìn)行程序的升級

2019-09-16 13:48:40

你好,我想使用兩個(gè)PROM(XCF32P)來配置我的XC4VLX200。我知道我可以使用M [2:0]引腳確定FPGA配置模式。但我不知道PROM如何從FPGA獲得當(dāng)前的配置模式。你能告訴我哪些引腳用于通知PROM當(dāng)前的配置模式嗎?謝謝。

2020-05-27 10:13:34

如何用ISP功能對Nuvoton8051單片機(jī)系列進(jìn)行ISP升級?

2020-12-21 06:36:14

TI工程師:你們好!現(xiàn)在由于工程項(xiàng)目上需要,計(jì)劃通過F28M36的以太網(wǎng)功能進(jìn)行程序升級,以前做過28335的CAN程序升級,是在28335的flashAPI上進(jìn)行修改編寫B(tài)ootloader

2018-09-20 11:50:12

本文提出了一種全新的總線可重配置的多處理器架構(gòu)。該架構(gòu)結(jié)合了多核與可重配置處理器的優(yōu)勢,具有并行性高、計(jì)算能力強(qiáng)、結(jié)構(gòu)復(fù)雜度低并且應(yīng)用領(lǐng)域廣泛靈活的特點(diǎn)。對

2009-06-13 14:11:04 11

11 介紹了基于ARM和FPGA的端到端重配置終端的硬件平臺(tái)設(shè)計(jì)方法。給出了系統(tǒng)設(shè)計(jì)的硬件結(jié)構(gòu)和重要接口, 提出了由ARM微處理器通過JTAG在系統(tǒng)配置FPGA的方法, 以滿足重配置系統(tǒng)中軟件

2010-09-14 16:40:09 21

21 本文檔主要是以Altera公司的Stratix II系列的FPGA器件為例,介紹了其內(nèi)嵌的增強(qiáng)型可重配置PLL在不同的輸入時(shí)鐘頻率之間的動(dòng)態(tài)適應(yīng),其目的是通過提供PLL的重配置功能,使得不需要對

2010-11-02 15:17:24 27

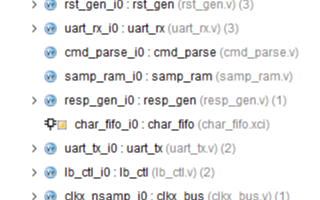

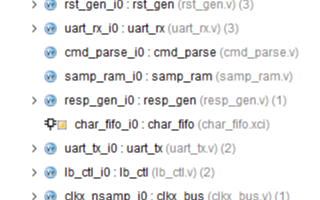

27 實(shí)現(xiàn)了一種用于上位機(jī)和FPGA處理板之間通信的可重配置接口,詳細(xì)介紹了該接口的包格式設(shè)計(jì)和FPGA邏輯設(shè)計(jì)。仿真結(jié)果表明,該可重配置接口能根據(jù)信令,實(shí)現(xiàn)準(zhǔn)實(shí)時(shí)在線參數(shù)配置

2010-11-22 15:15:28 12

12 FPGA的全局動(dòng)態(tài)可重配置技術(shù)主要是指對運(yùn)行中的FPGA器件的全部邏輯資源實(shí)現(xiàn)在系統(tǒng)的功能變換,從而實(shí)現(xiàn)硬件的時(shí)分復(fù)用。提出了一種基于System ACE的全局動(dòng)態(tài)可重配置設(shè)計(jì)方法,

2011-01-04 17:06:01 54

54 摘要: 一種基于嵌入式系統(tǒng)和Inlternet的FPGA動(dòng)態(tài)配置方案。詳細(xì)介紹了該方案的設(shè)計(jì)思想,并給出了設(shè)計(jì)實(shí)例。與傳統(tǒng)的FPGA配置方案相比,該方案具有靈活

2009-06-20 10:37:59 355

355

基于SRAM的可重配置PLD(可編程邏輯器件)的出現(xiàn),為系統(tǒng)設(shè)計(jì)者動(dòng)態(tài)改變運(yùn)行電路中PLD的邏輯功能創(chuàng)造了條件。PLD使用SRAM單元來保存字的配置數(shù)據(jù)決

2009-06-20 11:05:37 845

845

采用VC++程序的FPGA重配置設(shè)計(jì)方案利用現(xiàn)場可編程邏輯器件FPGA的多次可編程配置特點(diǎn),通過重新下載存儲(chǔ)于存儲(chǔ)器的不同系統(tǒng)數(shù)據(jù)

2010-04-14 15:14:57 580

580

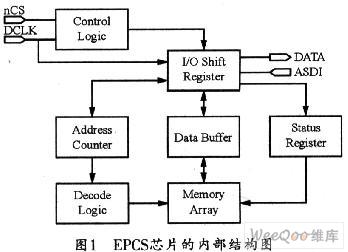

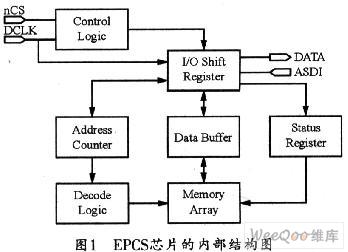

本文介紹了通過處理機(jī)用CPLD和Flash實(shí)現(xiàn)FPGA配置文件下載更新的方法。與傳統(tǒng)的JTAG或PROM串行下載配置方法相比,此方法具有更新配置文件靈活方便、易于操作、適用于大容量FPGA下載的特點(diǎn)

2018-10-25 05:51:00 8194

8194

基于查找表技術(shù)的FPGA在應(yīng)用時(shí)需要外置一個(gè)非易失性存儲(chǔ)器來存儲(chǔ)配置數(shù)據(jù)。如何方便靈活地對一個(gè)系統(tǒng)中多片FPGA的配置數(shù)據(jù)進(jìn)行升級是本文討論的問題

2011-06-22 09:39:38 2037

2037

為了滿足對分?jǐn)?shù)階 信號變換 進(jìn)行實(shí)時(shí)計(jì)算的要求,提出一種基于Altera St ratix II FPGA 平臺(tái)的可重配置分?jǐn)?shù)階信號變換處理器的硬件實(shí)現(xiàn)方案. 根據(jù)角度分解的算法,設(shè)計(jì)了一種通用的硬件框

2011-07-04 15:13:03 33

33 利用賽靈思 FPGA 的動(dòng)態(tài)重配置功能,同構(gòu)多線程執(zhí)行模型可同時(shí)兼得軟件靈活性和硬件性能。

2011-09-01 09:27:26 584

584

FPGA有多種配置模式:并行主模式為一片FPGA加一片EPROM的方式;主從模式可以支持一片PROM編程多片FPGA;串行模式可以采用串行PROM編程FPGA;外設(shè)模式可以將FPGA作為微處理器的外設(shè),由微處理

2011-09-08 17:50:27 1734

1734 基于 FPGA 的 RCS 有幾項(xiàng)值得注意的設(shè)計(jì)事項(xiàng)與優(yōu)勢。其核心部分是我們連接在一起以構(gòu)成單個(gè)計(jì)算系統(tǒng)的數(shù)個(gè)FPGA。在我們的可重配置系統(tǒng)中,我們使用了正交通信系統(tǒng),將 FPGA 布置在矩

2011-09-20 08:57:32 27

27 本文著重介紹了 Xilinx Platform Flash PROM 如何幫助系統(tǒng)和電路板設(shè)計(jì)人員簡化 FPGA 配置設(shè)計(jì)。用于配置 FPGA 的可選解決方案有很多,但它們通常都需要大量的前期設(shè)計(jì)工作和時(shí)間。Platform

2012-01-17 17:33:20 36

36 一些應(yīng)用利用 Xilinx FPGA 在每次啟動(dòng)時(shí)可改變配置的能力,根據(jù)所需來改變 FPGA 的功能。Xilinx Platform Flash XCFxxP PROM 的設(shè)計(jì)修訂 (Design Revisioning) 功能,允許用戶在單個(gè)PROM 中將多種配置存

2012-01-17 17:40:34 43

43 WP374 Xilinx FPGA的部分重配置

2012-03-07 14:34:39 34

34 在過去,靜態(tài)決策最壞情況分配曾為嚴(yán)格的實(shí)時(shí)約束提供了解決方案,而現(xiàn)在靈活性也成為一項(xiàng)要求。法國某研究項(xiàng)目建議使用的解決方案是一種分布在 FPGA 資源上,對軟硬件線程進(jìn)行

2012-05-09 10:40:11 1675

1675

本文介紹了XiLinx FPGA中DCM的結(jié)構(gòu)和相關(guān)特性,提出了一種基于XiLinx FPGA的DCM動(dòng)態(tài)重配置的原理方法,并給出了一個(gè)具體的實(shí)現(xiàn)系統(tǒng)。系統(tǒng)僅通過外部和......

2012-05-25 13:42:50 39

39 本文著重介紹了 Xilinx Platform Flash PROM 如何幫助系統(tǒng)和電路板設(shè)計(jì)人員簡化 FPGA 配置設(shè)計(jì)。用于配置 FPGA 的可選解決方案有很多,但它們通常都需要大量的前期設(shè)計(jì)工作和時(shí)間。Platform

2013-03-14 15:18:22 64

64 對MSP430系列單片機(jī)進(jìn)行編程的方式有以下3種:利用JTAG接口,利用BSL固件和利用用戶自定義的升級固件。由于利用自定義升級固件進(jìn)行程序升級的方式比較靈活,且用途廣泛,因此本文將對其作重點(diǎn)介紹。

2016-05-31 13:48:51 3618

3618

們快速開發(fā)和部署加速平臺(tái)。專門針對云級應(yīng)用而設(shè)計(jì)的基于FPGA的賽靈思可重配置加速堆棧,包括庫、框架集成、開發(fā)板并支持OpenStack。通過賽靈思FPGA,該可重配置加速堆棧方案提供了業(yè)界最高的計(jì)算效率:比x86服務(wù)器CPU高出40倍;比競爭型FPGA方案高出6倍。

2016-11-16 16:42:23 648

648 一種基于憶阻器的可重配置邏輯電路_張波

2017-01-08 10:18:57 4

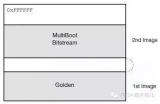

4 地址0處,FPGA默認(rèn)加載的配置程序。功能:用于引導(dǎo)FPGA跳到第二個(gè)配置程序所在的位置,進(jìn)行重配置,即multiboot功能 用于燒寫(更新)第二個(gè)配置程序(位于flash的xx偏移位置,偏移位置可由用戶設(shè)定) 第二個(gè)配置程序,叫用戶程序(位于flash的xx偏移位置,偏移位置可由用戶設(shè)定

2017-02-08 10:13:11 906

906

一旦你開始使用一個(gè)系統(tǒng),你可能更愿意它永遠(yuǎn)不需要升級。但是,通常情況下,這是不現(xiàn)實(shí)的。在現(xiàn)在的系統(tǒng)中,更新、升級、打補(bǔ)丁,這些都是司空見慣的。如果你對基于FPGA的系統(tǒng)非常熟悉,那么你可能對通過JTAG對PROM進(jìn)行編程、Xilinx iMPACT配置和編程工具也比較熟悉。

2018-07-14 05:24:00 3150

3150 這里提到的局部重配置技術(shù)(Partial Reconfiguration) 是現(xiàn)場可編程門陣列(呵呵,就是FPGA了) 器件中的一部分。指的是在FPGA其他部分還在正常運(yùn)行的情況下對其局部進(jìn)行的重新配置。

2017-02-11 16:32:11 2622

2622 工作效率。通過FPGA 的多重配置可以有效地精簡控制結(jié)構(gòu)的設(shè)計(jì),同時(shí)可以用邏輯資源較少的FPGA 器件實(shí)現(xiàn)需要很大資源才能實(shí)現(xiàn)的程序。以Virtex5系列開發(fā)板和配置存儲(chǔ)器SPIFLASH為基礎(chǔ),從硬件電路和軟件設(shè)計(jì)兩個(gè)方面對多重配置進(jìn)行分析,給出了多

2017-10-12 17:57:08 15

15 。 在現(xiàn)代的工業(yè)自控當(dāng)中對大型工業(yè)流程的分散處理、統(tǒng)一管理成本較高,而且設(shè)備的工業(yè)級實(shí)時(shí)監(jiān)測系統(tǒng)和視頻監(jiān)控系統(tǒng)都需要進(jìn)行大量的處理,使得成本高,但集中調(diào)控性不強(qiáng),而本系統(tǒng)通過對 FPGA 的區(qū)域配置,將上述功能集于一身;不僅成本低廉,體積較小,并且工業(yè)級效率也會(huì)

2017-10-18 16:38:59 4

4 視頻、影像和電信市場的標(biāo)準(zhǔn)推動(dòng)了異構(gòu)可重配置DSP硬件平臺(tái)的使用。在本文中這些平臺(tái)包括DSP處理器和FPGA,它們提供的現(xiàn)成硬件解決方案可以解決視頻、影像和電信設(shè)計(jì)中的重大難題,同時(shí)又不失差異化

2017-11-06 13:59:42 2

2 ,LabVIEW Real-Time模塊和LabVIEW FPGA模塊以及PXI-7931R可重配置I/O板卡完成實(shí)時(shí)仿真,并對I/O信號實(shí)現(xiàn)精確、靈活的定時(shí)與同步。

2017-11-18 18:24:14 1623

1623 對視頻等時(shí)序關(guān)鍵型應(yīng)用,采用純硬件解決方案可提升賽靈思 FPGA 的運(yùn)行能力。我們采一款基于小型狀態(tài)機(jī)的純硬件解決方案,并采用內(nèi)部配置訪問端口 (ICAP)接口加載比特流。這種方法具有多種優(yōu)勢

2017-11-22 17:08:56 1492

1492 的應(yīng)用。在主流的FPGA中,絕大多數(shù)都采用了SRAM來存放配置數(shù)據(jù),稱為SRAM FPGA。這種FPGA的突出優(yōu)點(diǎn)是可以進(jìn)行多次配置。通過給FPGA加載不同的配置數(shù)據(jù),即可令其實(shí)現(xiàn)不同的邏輯功能.FPGA這種可重配置的能力將給數(shù)字系統(tǒng)的設(shè)計(jì)帶來很大的方便。

2018-07-18 12:50:00 2407

2407

云級應(yīng)用而設(shè)計(jì)的基于FPGA的賽靈思可重配置加速堆棧,包括庫、框架集成、開發(fā)板并支持OpenStack。通過賽靈思FPGA,該可重配置加速堆棧方案提供了業(yè)界最高的計(jì)算效率:比x86服務(wù)器CPU高出40倍;比競爭型FPGA方案高出6倍。

2018-07-31 09:08:00 731

731 Xilinx 公司Virtex5 系列的FPGA 具有多重配置的特性,允許用戶在不掉電重啟的情況下,根據(jù)不同時(shí)刻的需求,可以從FLASH 中貯存的多個(gè)比特文件選擇加載其中的一個(gè),實(shí)現(xiàn)系統(tǒng)功能的變換。

2018-12-04 08:37:00 4654

4654

可重構(gòu)體系結(jié)構(gòu)已經(jīng)成為FPGA系統(tǒng)開發(fā)的研究熱點(diǎn),并已有許多令人矚目的研究成果及產(chǎn)品應(yīng)用。FPGA可重構(gòu)的應(yīng)用為用戶提供了方便的系統(tǒng)升級模式,同時(shí)也實(shí)現(xiàn)了基于相同硬件系統(tǒng)的不同工作模式功能。在當(dāng)

2018-12-30 11:09:00 5670

5670

結(jié)合對FPGA重配置方案的軟硬件設(shè)計(jì),本文通過PC機(jī)并通過總線(如PCI總線)將配置數(shù)據(jù)流下載到硬件功能模塊的有關(guān)配置芯片,從而完成配置FPGA的全過程。該方法的軟件部分基于Visual C++的開發(fā)環(huán)境,并用C++語言開發(fā)動(dòng)態(tài)連接庫,以用于軟件設(shè)計(jì)應(yīng)用程序部分的調(diào)用。

2018-12-30 09:26:00 2425

2425

FPGA可重配置帶來了很高的靈活性,所以基于FPGA的設(shè)計(jì)/產(chǎn)品往往也會(huì)有后期更新/升級的需求。同時(shí),需要更新/升級的FPGA板卡由于物理?xiàng)l件的限制,可能無法現(xiàn)場升級。

2018-09-15 09:30:47 3556

3556 主設(shè)備可以為控制器,CPLD等等。當(dāng)然FPGA也支持通過JTAG的方式進(jìn)行程序下載,同時(shí)也可以通過JTAG進(jìn)行FPGA時(shí)序抓取。 FPGA的配置過程包括以下幾方面:復(fù)位,程序加載,初始化,最后進(jìn)入用戶

2018-11-18 18:05:01 481

481 本視頻介紹了UltraScale +芯片的部分重配置功能,展示了Vivado Design Suite中部分重配置的新功能,并介紹了對部分重配置的更廣泛的訪問權(quán)限

2018-11-20 06:25:00 3831

3831 關(guān)鍵詞:PLD , SRAM , 可重配置電路 由于SRAM的可重配置PLD(可編程邏輯器件)的出現(xiàn),為系統(tǒng)設(shè)計(jì)者動(dòng)態(tài)改變運(yùn)行電路中PLD的邏輯功能創(chuàng)造了條件。PLD使用SRAM單元來保存字的配置

2019-02-23 14:30:01 675

675

本文檔的主要內(nèi)容詳細(xì)介紹的是程序的擴(kuò)展性如何進(jìn)行程序的擴(kuò)展。

2019-04-26 18:26:00 0

0 Partial Reconfiguration(部分重配置)在現(xiàn)在的FPGA應(yīng)用中越來越常見,我們這次的教程以Project模式為例來說明部分重配置的操作過程。

2021-07-05 15:28:24 3140

3140

使用CH340串口模塊對STM32進(jìn)行程序下載一、接線二、利用FlyMcu進(jìn)行STM32程序下載1、STM32配置2、FlyMcu配置一、接線

2021-12-20 19:37:32 21

21 西門子S7-1200系列PLC可以通過存儲(chǔ)卡進(jìn)行程序的更新,固件版本的升級以及程序數(shù)據(jù)的存儲(chǔ)多項(xiàng)功能。本例進(jìn)行程序更新的操作。

2023-03-07 10:34:16 2603

2603 一般情況下,要重新配置一個(gè)FPGA需要使其處于復(fù)位狀態(tài),并通過外部控制器重新加載一個(gè)新設(shè)計(jì)到器件中。而局部重配置技術(shù)允許在FPGA內(nèi)部或外部的控制器在加載一個(gè)局部設(shè)計(jì)到一個(gè)可重配置模塊中時(shí)

2023-03-17 14:03:39 1508

1508 除通過外部多功能IO來選擇之外,易靈思通過內(nèi)部重配置實(shí)現(xiàn)遠(yuǎn)程更新操作也非常簡單。

2023-05-30 09:24:32 712

712

電子發(fā)燒友App

電子發(fā)燒友App

評論