的項(xiàng)目數(shù)量也很龐大,資金很分散,需要集中精力辦大事。以產(chǎn)業(yè)并購為例,國內(nèi)規(guī)模最大也就20多億美元,高通一起并購就是470億美元,國內(nèi)的資金就做不到。

2017-03-30 09:19:11 1095

1095 想要機(jī)器人實(shí)現(xiàn)智能化,需要具有敏銳且優(yōu)秀的感知,同時還能有精準(zhǔn)的運(yùn)控。就感知計(jì)算而言,尤其是視覺以及深度學(xué)習(xí),計(jì)算量往往很大,對器件性能要求高。而且感知算法也在不斷發(fā)展,這需要對機(jī)器人處理系統(tǒng)

2022-08-01 07:26:00 1687

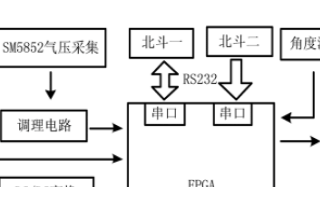

1687 ,從而獲得最佳互連。此外,還可以最大程度地減少初始分配中產(chǎn)生的網(wǎng)絡(luò)交互,提高布線完成率。FPGA Synthesis高級優(yōu)化算法一套獨(dú)特的優(yōu)化算法可自動將特定優(yōu)化集中在最有可能妨礙整體性能的設(shè)計(jì)領(lǐng)域,例如

2018-09-20 11:11:16

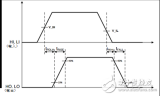

工程師和物理布局設(shè)計(jì)師面臨著更大的挑戰(zhàn)。很多視頻系統(tǒng)都采用多功能FPGA和多傳輸率SDI集成電路,以支持高性能專業(yè)視頻在長距離的傳輸。FPGA需要高密度、細(xì)跡線寬度的傳輸,而高速模擬SDI傳輸需要阻抗匹配和信號保真。那么FPGA/SDI子系統(tǒng)中的高速板布局挑需要面對哪些挑戰(zhàn)?具體該怎么做呢?

2019-08-06 07:23:31

提高競爭力,嵌入式系統(tǒng)開發(fā)人員需要一種能夠幫助他們開發(fā)獨(dú)具優(yōu)勢產(chǎn)品的解決方案,非常靈活,效率也非常高。基于FPGA的單芯片實(shí)現(xiàn)方法具有低成本和快速面市等優(yōu)點(diǎn),是多芯片和ASICSoC非常有吸引力的替代

2021-07-14 08:00:00

的Enpirion的ED8101P0xQI單相數(shù)字控制器,可實(shí)現(xiàn)對FPGA的多種遠(yuǎn)程監(jiān)視和低功耗特性。 5.提前規(guī)劃電源樹,整體布局優(yōu)化系統(tǒng)功耗 系統(tǒng)硬件設(shè)計(jì)會影響設(shè)計(jì)的復(fù)雜程度、周期和成本,因此,盡早規(guī)劃

2018-10-23 16:33:09

FPGA器件售價(jià)不到10美元(在與門陣列產(chǎn)品相當(dāng)?shù)呐繒r)。 性能和功耗 與傳統(tǒng)數(shù)據(jù)處理方法不同,DSP采用了高度流水線化的并行操作。而FPGA結(jié)構(gòu)則可以做得更好,達(dá)到更高的性能。FPGA具有

2011-02-17 11:21:37

設(shè)計(jì)方法也在發(fā)生變化,對FPGA和PCB的設(shè)計(jì)可以并行進(jìn)行以降低系統(tǒng)成本、優(yōu)化系統(tǒng)性能并縮短設(shè)計(jì)周期。 PCB和FPGA一般是在不同的設(shè)計(jì)環(huán)境下創(chuàng)建,過去這些設(shè)計(jì)方案很少相互溝通。然而,隨著高性能

2018-09-21 11:55:09

EDA技術(shù)具有什么特征?FPGA是什么原理?FPGA設(shè)計(jì)應(yīng)用及優(yōu)化策略基于VHDL的FPGA系統(tǒng)行為級設(shè)計(jì)

2021-04-15 06:33:58

效率;造成過多的電磁干擾而影響系統(tǒng)的兼容性。 ZXLD1370是一款多拓 對于開關(guān)模式轉(zhuǎn)換器而言,出色的印制電路板(PCB)布局對獲得最佳系統(tǒng)性能至關(guān)重要。若PCB設(shè)計(jì)不當(dāng),則可能造成以下后果

2016-12-28 09:44:05

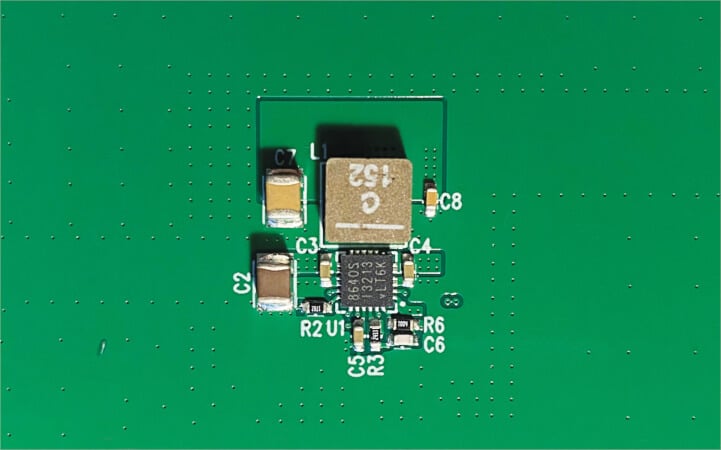

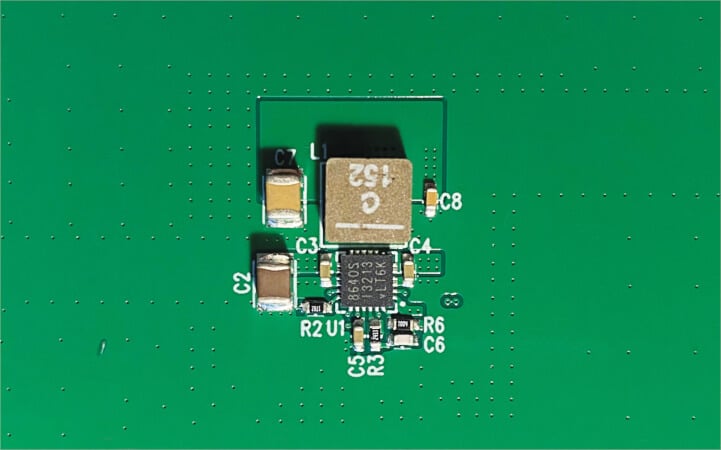

對于開關(guān)模式轉(zhuǎn)換器而言,出色的印制電路板(PCB)布局對獲得最佳系統(tǒng)性能至關(guān)重要。若PCB設(shè)計(jì)不當(dāng),則可能造成以下后果:對控制電路產(chǎn)生太多噪聲而影響系統(tǒng)的穩(wěn)定性;在PCB跡線上產(chǎn)生過多損耗而

2018-11-22 15:22:33

全球出現(xiàn)的能源短缺問題使各國***都開始大力推行節(jié)能新政。電子產(chǎn)品的能耗標(biāo)準(zhǔn)越來越嚴(yán)格,對于電源設(shè)計(jì)工程師,如何設(shè)計(jì)更高效率、更高性能的電源是一個永恒的挑戰(zhàn)。本文從電源PCB的布局出發(fā),介紹了優(yōu)化

2018-09-14 16:22:45

基于FPGA的CNN的多種網(wǎng)絡(luò)實(shí)現(xiàn)。OpenCL的編程模型我們機(jī)器人系統(tǒng)實(shí)驗(yàn)室今年的工作重點(diǎn)便是為機(jī)器人搭建基于CPU+FPGA的異構(gòu)計(jì)算平臺。根據(jù)我們的經(jīng)驗(yàn),FPGA能夠在一些關(guān)鍵的機(jī)器人應(yīng)用中發(fā)揮極大

2017-03-20 17:54:31

,可以讓企業(yè)集中精力改善企業(yè)在社會和環(huán)境方面的問題,提高供應(yīng)鏈的生產(chǎn)力,同樣可以通過該程序向利益相關(guān)方征求意見。

2015-08-05 17:39:37

HBase是Hadoop生態(tài)系統(tǒng)中的一個組件,是一個分布式、面向列的開源數(shù)據(jù)庫,可以支持?jǐn)?shù)百萬列、超過10億行的數(shù)據(jù)存儲,因此,對HBase性能提出了一定的要求,那么如何進(jìn)行HBase性能優(yōu)化呢

2018-04-20 17:16:47

,該軟件還包含能夠輕松在實(shí)時嵌入式硬件上實(shí)現(xiàn)的機(jī)器人IP,用于避障、動力學(xué)和搜尋算法,幫助自主系統(tǒng)或機(jī)器人選擇最佳路徑。 “在過去23年里,LabVIEW開發(fā)環(huán)境的發(fā)展非常顯著。LabVIEW從最初

2019-05-21 07:40:08

作為一名Linux 或 Android 平臺的系統(tǒng)工程師,在開發(fā)系統(tǒng)新功能外,主要工作就是優(yōu)化系統(tǒng)性能,使系統(tǒng)上以最優(yōu)的狀態(tài)運(yùn)行,但是由于硬件問題、軟件問題、網(wǎng)絡(luò)環(huán)境等的復(fù)雜性和多變性,導(dǎo)致對系統(tǒng)

2019-07-22 06:48:03

通知。此設(shè)計(jì)利用了 FRAM 的快速寫入速度和高壽命 – 但復(fù)雜程度更高。 為了真正優(yōu)化系統(tǒng),需要在 MSP430FR5969 MCU 上運(yùn)行振動數(shù)據(jù)頻譜分析,最大限度減少必須無線傳輸?shù)臄?shù)據(jù)。 通過利用

2018-09-10 11:57:29

"NI PXI 射頻平臺是一個理想的選擇,因?yàn)樗哂谐商椎姆独M件易于獲取,并且運(yùn)行快速。工程師們用于理解射頻原理的時間變少,這樣他們就可以集中精力開發(fā)更加優(yōu)化且易于使用的測試序列應(yīng)用。"

2019-08-27 08:34:51

路徑的優(yōu)化算法,并基于一種方法編程實(shí)現(xiàn)了基本方案。最后在HSP貼片系統(tǒng)上使用本解決方案,大幅度提高了生產(chǎn)效率,證明了本解決方案的優(yōu)越性和高效性,同時也為用其它算法解決SMT系統(tǒng)優(yōu)化問題提供了一種可

2010-04-24 10:09:25

Nexus4DDR開發(fā)板搭載 Xilinx@ artix-7FPGA芯片,是一個打開即用型的數(shù)字電路開發(fā)平臺,幫助使用者能夠在課堂環(huán)境下實(shí)現(xiàn)諸多工業(yè)領(lǐng)域的應(yīng)用。相比早期版本,經(jīng)優(yōu)化后

2021-07-22 08:34:54

各位大神: 大家有用SDx開發(fā)環(huán)境對zturn開發(fā)板進(jìn)行連接調(diào)試的么?連接方式為PC機(jī)與開發(fā)板用網(wǎng)線連接,pc機(jī)的ip網(wǎng)段與開發(fā)板的ip網(wǎng)段設(shè)置為同一ip網(wǎng)段,在SDx開發(fā)環(huán)境中點(diǎn)擊linux

2017-08-21 09:26:12

促單。而且傳統(tǒng)電銷人員也不會因?yàn)闄C(jī)器人的加入而失業(yè),只會把精力更多的集中到回訪意向客戶上面,效果是顯而易見的。行業(yè)迅猛發(fā)展,市面上的電銷機(jī)器人品牌也是五花八門,有優(yōu)有劣,因此選擇到適合自己的電銷機(jī)器人

2018-06-15 10:34:35

,往往是這些細(xì)節(jié)和準(zhǔn)備工作沒做好,導(dǎo)致大家在后續(xù)編程中出現(xiàn)一些費(fèi)解的Bug,所以我基于我的經(jīng)驗(yàn),前面幾課花了大量的篇幅介紹一些概念性的東西,并把這些細(xì)節(jié)整理出來分享給大家,以免浪費(fèi)一些不必要的時間,集中精力在項(xiàng)目開發(fā)上。更多原創(chuàng)內(nèi)容,掃描二維碼聯(lián)系作者本人獲取,原創(chuàng)內(nèi)容,請勿轉(zhuǎn)載`

2019-11-27 14:30:17

檢測算法經(jīng)驗(yàn)。特申請此開發(fā)板,優(yōu)化系統(tǒng)性能,提高檢測速度。項(xiàng)目描述:第一代坯布疵點(diǎn)檢測算法已經(jīng)在工控機(jī)實(shí)現(xiàn)并設(shè)計(jì)成品在產(chǎn)線上進(jìn)行實(shí)驗(yàn)。為了進(jìn)一步優(yōu)化疵點(diǎn)檢測系統(tǒng)的檢測速度。目前想通過相機(jī)+FPGA

2015-10-09 15:09:57

嗨,我下載了安裝了可執(zhí)行文件Xilinx_SDSoC_2017.1_sdx_0623_1_Win64的SDSoC,但是當(dāng)我打開安裝的程序時,它是SDx而不是SDSoC。我很擔(dān)心,因?yàn)槲乙矅L試

2018-12-27 10:52:18

無論從微觀到宏觀、從延長電池壽命到減少全球變暖的溫室效應(yīng)等等,各種不同因素都在迅速推動系統(tǒng)設(shè)計(jì)人員關(guān)注節(jié)能問題。一項(xiàng)有關(guān)設(shè)計(jì)優(yōu)先考慮事項(xiàng)的最新調(diào)查指出,大部分工程師已把功耗排在首位,或者是將其緊跟在性能、密度和成本之后。在功耗方面,FPGA帶來了獨(dú)特的挑戰(zhàn)。為什么要設(shè)計(jì)優(yōu)化FPGA功耗?

2019-08-08 07:39:45

本文闡述了Spartan-3 FPGA針對DSP而優(yōu)化的特性,并通過實(shí)現(xiàn)示例分析了它們在性能和成本上的優(yōu)勢。

2019-10-18 07:11:35

今年年初,賽靈思率先在FPGA領(lǐng)域提出目標(biāo)設(shè)計(jì)平臺概念,旨在通過選用開放的標(biāo)準(zhǔn)、通用的開發(fā)流程以及類似的設(shè)計(jì)環(huán)境,減少通用工作對設(shè)計(jì)人員時間的占用,確保他們能集中精力從事創(chuàng)新性的開發(fā)工作。

2019-08-13 07:27:15

全球出現(xiàn)的能源短缺問題使各國***都開始大力推行節(jié)能新政。電子產(chǎn)品的能耗標(biāo)準(zhǔn)越來越嚴(yán)格,對于電源設(shè)計(jì)工程師,如何設(shè)計(jì)更高效率、更高性能的電源是一個永恒的挑戰(zhàn)。本文從電源PCB的布局出發(fā),介紹了優(yōu)化

2021-12-28 07:07:59

,分辨率為1080p的高清(HD)視頻的水印應(yīng)用。

SDAccel開發(fā)環(huán)境能讓設(shè)計(jì)人員先用OpenCL編寫應(yīng)用,然后在無需了解底層FPGA實(shí)現(xiàn)工具的情況下把應(yīng)用編譯到FPGA中。可以以這種視頻水印應(yīng)用為例

2019-06-19 07:27:40

與自動化工具,可以將開發(fā)資源集中在不同的產(chǎn)品線上 ?迅速應(yīng)用最新的協(xié)議與規(guī)格 ?更有效率的工程師培訓(xùn)(由高端到低成本的FPGA器件都通過同一種開發(fā)工具實(shí)現(xiàn)完成,并提供實(shí)例教學(xué)講座及演示等) ?可以重新

2012-02-24 17:26:23

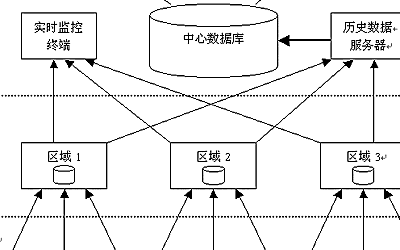

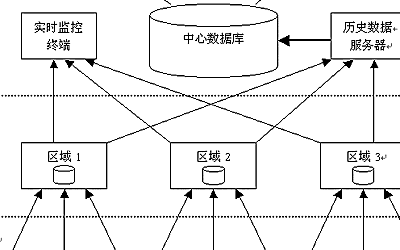

隨著中國經(jīng)濟(jì)的快速發(fā)展,人們生活品質(zhì)的改善,對環(huán)境保護(hù)要求越來越高,污水是環(huán)境污染一個非常重要來源,國家現(xiàn)在大力建設(shè)污水處理系統(tǒng)。污水處理系統(tǒng)的集中監(jiān)控,能極大提高監(jiān)管力度,并能通過數(shù)據(jù)的集中

2018-06-07 15:13:28

提高競爭力,嵌入式系統(tǒng)開發(fā)人員需要一種能夠幫助他們開發(fā)獨(dú)具優(yōu)勢產(chǎn)品的解決方案,非常靈活,效率也非常高。基于FPGA的單芯片實(shí)現(xiàn)方法具有低成本和快速面市等優(yōu)點(diǎn),是多芯片和ASICSoC非常有吸引力的替代

2021-07-12 08:00:00

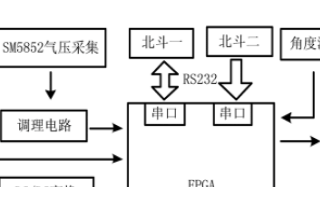

研究了一種用FPGA技術(shù)實(shí)現(xiàn)三輪全方位移動機(jī)器人運(yùn)動控制系統(tǒng)的方法,與雙DSP結(jié)構(gòu),DSP+CPLD結(jié)構(gòu),以及DSP+專用集成電路結(jié)構(gòu)等相比,該方法具有簡單可靠,擴(kuò)展性強(qiáng)等特點(diǎn)。且FPGA設(shè)計(jì)簡單,使用方便,開發(fā)周期短,能夠實(shí)現(xiàn)真正的SOPC系統(tǒng)。

2019-10-22 07:35:19

。串口通信以其簡單的硬件連接,成熟的通信協(xié)議,成為上下位機(jī)之間通信的首選。移植了Linux 操作系統(tǒng)的s3c2440 可以在Linux 環(huán)境下操作串口,降低了串口操作的難度,可以使開發(fā)者集中精力開發(fā)大規(guī)模的應(yīng)用程序,而不必在操作底層設(shè)計(jì)上耗費(fèi)時間。

2020-04-14 07:31:33

所有低成本的FPGA都以頗具吸引力的價(jià)格提供基本的邏輯性能,并能滿足廣泛的多用途設(shè)計(jì)需求。然而,當(dāng)考慮在FPGA構(gòu)造中嵌入DSP功能時,必須選擇高端FPGA以獲得諸如嵌入式乘法器和分布式存儲器等平臺

2019-06-27 06:12:26

FPGA加速卡是如何產(chǎn)生的?主要的FPGA加速卡產(chǎn)品有哪些?基于加速卡的FPGA生態(tài)系統(tǒng)布局是怎樣的?

2021-06-17 06:07:15

管理移動機(jī)器人的導(dǎo)航算法的實(shí)現(xiàn)和多任務(wù)的執(zhí)行。實(shí)驗(yàn)結(jié)果表明:該系統(tǒng)能夠實(shí)現(xiàn)避障和導(dǎo)航功能并能順利達(dá)到目的地。

2020-11-23 15:08:52

怎樣寫c代碼才能讓程序的執(zhí)行效率更高?同樣結(jié)構(gòu)和功能的代碼,只是其中的變量的定義方式不同,但程序的執(zhí)行效率卻又天壤之別!能相差10倍!!!所以,想問問怎樣寫代碼,可以讓代碼的執(zhí)行效率更高?

2020-07-14 08:00:20

面對日益嚴(yán)格的規(guī)范要求以及降低工廠運(yùn)營成本的迫切需求,機(jī)械制造商正在尋找提高產(chǎn)品用電效率的解決方案。最大化控制機(jī)械設(shè)備電機(jī)效率的方法眾多,其中之一就是采用效率更高、更先進(jìn)的磁場定向控制技術(shù)來優(yōu)化用電效率。

2019-10-18 06:40:22

系統(tǒng)補(bǔ)償,確保最優(yōu)的基站性能。Maxim InTune產(chǎn)品,例如MAX15301,解決了電源管理的設(shè)計(jì)難題。這些產(chǎn)品很容易實(shí)現(xiàn)高性能、DC-DC電源設(shè)計(jì),濾波電容尺寸更小,具備更高的工作效率。該數(shù)字

2018-09-26 17:27:09

本文基于Viitex-5 LX110驗(yàn)證平臺的設(shè)計(jì),探索了高性能FPGA硬件系統(tǒng)設(shè)計(jì)的一般性方法及流程,以提高FPGA的系統(tǒng)性能。

2021-04-26 06:43:55

由于系統(tǒng)帶寬不斷的增加,因此針對更高的速度和性能,設(shè)計(jì)人員對存儲技術(shù)進(jìn)行了優(yōu)化。下一代雙數(shù)據(jù)速率(DDR)SDRAM芯片是DDR3 SDRAM。 DDR3 SDRAM具有比DDR2更多的優(yōu)勢。這些

2019-08-09 07:42:01

多核處理器環(huán)境下的編程挑戰(zhàn)是什么如何通過LabVIEW圖形化開發(fā)平臺有效優(yōu)化多核處理器環(huán)境下的信號處理性能

2021-04-26 06:40:29

怎么實(shí)現(xiàn)基于FPGA視頻采集中的I2C總線設(shè)計(jì)?

2021-06-03 06:51:15

本文介紹在智能手機(jī)中實(shí)現(xiàn)環(huán)境光感測遇到的主要挑戰(zhàn),以及如何克服這些挑戰(zhàn),以實(shí)現(xiàn)背光燈更高的反應(yīng)靈敏度,并能精確地根據(jù)環(huán)境光來調(diào)整背光亮度。

2021-03-08 07:25:33

本文提出一種優(yōu)化的高性能高可靠性的嵌入式大屏幕LED顯示系統(tǒng),只需要用1片FPGA和2片SRAM就可以實(shí)現(xiàn)大屏幕LED顯示的驅(qū)動和內(nèi)容更換,可以說其性能已經(jīng)大有改善。本設(shè)計(jì)可以應(yīng)對多種大屏幕顯示的場合。

2021-06-04 06:02:01

本文從電源PCB的布局出發(fā),介紹了優(yōu)化SIMPLE SWITCHER電源模塊性能的最佳PCB布局方法、實(shí)例及技術(shù)。

2021-04-25 06:38:31

的 FPU 框,即可實(shí)現(xiàn)APU-FPU 連接(見圖 3 頂部)。該向?qū)Э?b class="flag-6" style="color: red">實(shí)現(xiàn)一個經(jīng)過優(yōu)化能以處理器時鐘三分之一速率運(yùn)行的雙精度 FPU。您也可定制更高時鐘速率的 FPU 和單精度 FPU。如果不想

2018-08-03 11:15:23

系統(tǒng)設(shè)計(jì)人員被要求生產(chǎn)更小、效率更高的電源解決方案,以滿足所有行業(yè)SoC和FPGA的高耗電需求。在先進(jìn)的電子系統(tǒng)中,因?yàn)殡娫幢仨毞旁赟oC或其外圍設(shè)備(如DRAM或I/O設(shè)備)附近,因此電源封裝的可占用空間至關(guān)重要。在便攜式儀器中,如手持條碼掃描儀或醫(yī)療數(shù)據(jù)記錄儀系統(tǒng),空間更為緊湊。

2019-07-31 07:15:59

描述此參考設(shè)計(jì)展示了設(shè)計(jì)雙面 DC/DC 布局以實(shí)現(xiàn)更高電源密度的正確方法。該設(shè)計(jì)指南重點(diǎn)介紹了常見錯誤以及如何避免這些錯誤,以及測試結(jié)果表明在兩側(cè)布局中正確實(shí)施 TPS54824 器件不會影響性能

2022-09-15 06:50:38

如何通過LabVIEW優(yōu)化多核環(huán)境下的信號處理性能?

2021-04-09 06:49:51

。面向 Arria 10 等高端 FPGA 的電源管理解決方案應(yīng)該謹(jǐn)慎選擇。 一個經(jīng)過精心計(jì)劃的電源管理設(shè)計(jì)可以減小 PCB 尺寸、減輕重量并降低復(fù)雜性,同時降低功耗和冷卻成本。這對優(yōu)化系統(tǒng)性能而言

2018-10-15 10:30:31

。在許多情況下,機(jī)器人必須能夠自主工作,利用導(dǎo)航系統(tǒng)來監(jiān)視并控制它從一個位置移到另一個位置。管理位置和運(yùn)動時的精度是實(shí)現(xiàn)有用、可靠的自主工作的關(guān)鍵。MEMS(微機(jī)電系統(tǒng))陀螺儀可提供反饋檢測機(jī)制,對優(yōu)化

2014-09-02 17:15:20

參考。如何運(yùn)行在FPGA弓I起的嘈雜環(huán)境中,已成為FPGA參考時鐘設(shè)計(jì)面I臨的主要挑戰(zhàn)。 圖la和圖lb所示為兩種類型的XO結(jié)構(gòu)圖。晶體已經(jīng)被使用f數(shù)十年來作為大多數(shù)電子系統(tǒng)的脈搏。他們?yōu)槎喾N高性能

2018-09-26 14:33:58

當(dāng)今世界,設(shè)計(jì)師們似乎永遠(yuǎn)不停地追求更高效率。我們希望以更低的功率輸入得到更高的功率輸出!更高的系統(tǒng)效率需要團(tuán)隊(duì)的努力,這包括(但不限于)性能更高的柵極驅(qū)動器、控制器和新的寬禁帶技術(shù)。特別是高電流

2019-08-07 04:45:12

。 這本書把多年推廣到諸多公司和工程師團(tuán)隊(duì)的經(jīng)驗(yàn)以及由專門的白皮書和應(yīng)用要點(diǎn)匯集的許多知識進(jìn)行濃縮,可以用來完善工程師的知識,幫助他們成為高級的fpga設(shè)計(jì)者。...高級FPGA設(shè)計(jì) 結(jié)構(gòu)、實(shí)現(xiàn)和優(yōu)化

2012-03-01 14:59:23

新年伊始,設(shè)計(jì)師們似乎在永遠(yuǎn)不停地追求更高效率。在此系列的第一部分中,我討論了高電流柵極驅(qū)動器如何幫助系統(tǒng)實(shí)現(xiàn)更高的效率。高速柵極驅(qū)動器可以實(shí)現(xiàn)相同的效果。高速柵極驅(qū)動器可以通過降低FET的體二極管

2019-03-08 06:45:10

電源、機(jī)房環(huán)境集中監(jiān)控系統(tǒng)的出現(xiàn),將原來相對分散的各個機(jī)房電源、空調(diào)設(shè)備的運(yùn)行和環(huán)境數(shù)據(jù)進(jìn)行了集中,方便了監(jiān)控。

2010-06-27 18:16:43 38

38 闡述基于調(diào)度自動化系統(tǒng)的四遙功能, 實(shí)現(xiàn)地區(qū)電網(wǎng)無功電壓優(yōu)化運(yùn)行集中控制的原理、方法和控制策略等。介紹無功電壓優(yōu)化集中控制系統(tǒng)在青島電網(wǎng)的應(yīng)用狀況, 探討系統(tǒng)應(yīng)用中應(yīng)注

2011-08-26 17:14:59 20

20 介紹了基于硬件描述語言Verilog HDL設(shè)計(jì)的SDX總線與Wishbone總線接口轉(zhuǎn)化的設(shè)計(jì)與實(shí)現(xiàn),并通過Modelsim進(jìn)行功能仿真,在QuartusⅡ軟件平臺上綜合,最終在Altera公司的CycloneⅢ系列FPGA上調(diào)試。實(shí)驗(yàn)

2012-01-11 10:21:21 25

25 基于FPGA的SM3算法優(yōu)化設(shè)計(jì)與實(shí)現(xiàn)的論文

2015-10-29 17:16:51 4

4 高級FPGA設(shè)計(jì) 結(jié)構(gòu)、實(shí)現(xiàn)和優(yōu)化,適合于FPGA的進(jìn)階學(xué)習(xí)。

2016-05-11 16:40:55 15

15 高級FPGA設(shè)計(jì) 結(jié)構(gòu)、實(shí)現(xiàn)和優(yōu)化,適合于學(xué)習(xí)FPGA的進(jìn)階學(xué)習(xí)。

2016-05-11 16:40:55 14

14 當(dāng)今世界,設(shè)計(jì)師們似乎永遠(yuǎn)不停地在追求更高效率。我們希望以更低的功率輸入得到更高的功率輸出!更高的系統(tǒng)效率需要團(tuán)隊(duì)的努力,這包括(但不限于)性能更高的柵極驅(qū)動器、控制器和新的寬禁帶技術(shù)。特別是高電流柵極驅(qū)動器,其能夠通過降低開關(guān)損耗幫助提升整體系統(tǒng)效率。當(dāng)FET開關(guān)打開或關(guān)閉時,就會出現(xiàn)開關(guān)損耗。

2017-01-12 15:40:39 1010

1010

解釋SDx:SDx? 是一種面向系統(tǒng)和軟件工程師的開發(fā)環(huán)境。?SDx 讓沒有 FPGA 專業(yè)知識的系統(tǒng)和軟件工程師也能通過使用高層次編程語言,來獲益于帶有業(yè)界標(biāo)準(zhǔn)處理器的可編程硬件的強(qiáng)大威力。

2019-10-06 17:47:00 681

681

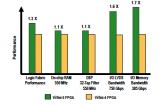

在FPGA系統(tǒng)設(shè)計(jì)中,要達(dá)到性能最大化需要平衡具有混合性能效率的元器件,包括邏輯構(gòu)造(fabric)、片上存儲器、DSP 和I/O帶寬。在本文中,我將向你解釋怎樣能在追求更高系統(tǒng)級性能的過程中受益于Xilinx? 的Virtex?-5 FPGA構(gòu)建模塊,特別是新的ExpressFabric?技術(shù)。

2018-07-22 09:30:00 1628

1628

3月8日消息 據(jù)國外媒體報(bào)道,美國通信設(shè)備巨頭思科公司宣布,將停止WiMax基站的研發(fā)及制造等工作,以集中精力開展IP網(wǎng)絡(luò)業(yè)務(wù)。 思科公司新聞發(fā)言人布拉迪(Jim Brady)本周五宣布:思科公司

2017-12-12 06:05:33 538

538 賽靈思7系列FPGA平臺整合了業(yè)內(nèi)功耗最低、性能最高的28nm FPGA、ISE設(shè)計(jì)工具、符合AXI4規(guī)范的IP和在開發(fā)板上運(yùn)行的目標(biāo)參考設(shè)計(jì),能夠讓工程師盡快著手設(shè)計(jì)和將現(xiàn)有設(shè)計(jì)移植到新型7系列類FPGA上的器件和工具,給工程師充分的設(shè)計(jì)自由,可以集中精力實(shí)現(xiàn)產(chǎn)品差異化。

2018-06-05 13:45:00 3045

3045 賽靈思公司(Xilinx)推出針對 OpenCL、C 和 C++的S DAccel 開發(fā)環(huán)境,將單位功耗性能提高達(dá)25倍,從而利用 FPGA 實(shí)現(xiàn)數(shù)據(jù)中心應(yīng)用加速。SDAccel 是賽靈思 SDx

2018-08-30 17:00:00 1023

1023 電源、機(jī)房環(huán)境集中監(jiān)控系統(tǒng)的出現(xiàn),將原來相對分散的各個機(jī)房的電源、空調(diào)設(shè)備的運(yùn)行狀態(tài)和環(huán)境數(shù)據(jù)進(jìn)行了集中,方便了監(jiān)控。然而隨著我國通信事業(yè)的發(fā)展,通信布局從原來的大型母局式轉(zhuǎn)變到接入設(shè)備更靠近用戶

2018-09-19 09:42:00 5226

5226

面向OpenCL,C和C ++的SDAccel開發(fā)環(huán)境利用FPGA將數(shù)據(jù)中心單位功耗性能提升高達(dá)25倍。作為SDx系列的成員,SDAccel是首個面向OpenCL,C和C ++進(jìn)行架構(gòu)優(yōu)化的編譯器,并結(jié)合了

庫,開發(fā)板,可在FPGA上實(shí)現(xiàn)類似CPU / GPU的開發(fā)運(yùn)行體驗(yàn)。

2018-11-27 06:49:00 2842

2842 據(jù)采集系統(tǒng)中得到廣泛應(yīng)用。有些FPGA是反熔絲的,可靠性能和穩(wěn)定性能非常高,這類FPGA在特定宇航應(yīng)用中是必選項(xiàng)。

2020-01-27 16:02:00 768

768

AMD今天獲得了一份新的超算訂單,聯(lián)合HPE旗下的Cray為美國能源部建造El Capitan超算,預(yù)算6億美元,將使用AMD下一代CPU及Radeon加速卡,2023年問世,浮點(diǎn)性能200億億次。

2020-03-06 08:42:37 512

512 應(yīng)用能夠有更高的性能,您需要熟悉如下介紹的硬件。另外,將會介紹編譯優(yōu)化選項(xiàng),有助于將您的 OpenCL 應(yīng)用更好的實(shí)現(xiàn) RTL 的轉(zhuǎn)換和映射,并部署到 FPGA 上執(zhí)行。

2020-07-16 17:58:28 6015

6015

行業(yè)媒體對大數(shù)據(jù)在數(shù)字營銷中的優(yōu)勢進(jìn)行了廣泛討論,現(xiàn)在集中精力將數(shù)據(jù)分析用于搜索引擎優(yōu)化(SEO)。

2020-09-03 11:29:14 2022

2022 通信運(yùn)營商必須重新集中精力覆蓋“非現(xiàn)場”并提高可靠性,以更好地滿足客戶的需求。

2020-10-08 14:34:00 524

524 全球出現(xiàn)的能源短缺問題使各國政府都開始大力推行節(jié)能新政。電子產(chǎn)品的能耗標(biāo)準(zhǔn)越來越嚴(yán)格,對于電源設(shè)計(jì)工程師,如何設(shè)計(jì)更高效率、更高性能的電源是一個永恒的挑戰(zhàn)。本文從電源PCB的布局出發(fā),介紹了優(yōu)化

2022-01-06 12:36:35 10

10 蘋果WWDC2022大會亮點(diǎn):Focus專注模式幫助減少用戶干擾并集中精力 ? ? ? ? ? ? ? 審核編輯:彭靜

2022-06-07 10:07:38 699

699

如何實(shí)現(xiàn)更高的系統(tǒng)效率——第二部分:高速柵極驅(qū)動器

2022-11-02 08:15:59 2

2 如何利用高電流柵極驅(qū)動器實(shí)現(xiàn)更高的系統(tǒng)效率

2022-11-02 08:16:03 0

0 本文介紹了實(shí)現(xiàn)優(yōu)化電路板布局的基礎(chǔ),這是開關(guān)模式電源設(shè)計(jì)的一個關(guān)鍵方面。

2023-03-08 15:01:00 403

403

為了實(shí)現(xiàn)卓越應(yīng)用體驗(yàn),伴隨著創(chuàng)新技術(shù)的發(fā)展,目前業(yè)內(nèi)動環(huán)監(jiān)控方案提供商也在積極嘗試將一些新興技術(shù)融合到動力環(huán)境集中監(jiān)控系統(tǒng)中來,比如人工智能、5G、物聯(lián)網(wǎng)等創(chuàng)新技術(shù)。依托技術(shù)的應(yīng)用優(yōu)勢,動力環(huán)境集中

2023-05-17 15:44:16 261

261 電子發(fā)燒友網(wǎng)站提供《使用FPGA I/O優(yōu)化來設(shè)計(jì)更高性價(jià)比的PCB.pdf》資料免費(fèi)下載

2023-09-13 09:24:49 0

0 電子發(fā)燒友網(wǎng)站提供《如何使PLC的設(shè)計(jì)和實(shí)現(xiàn)達(dá)到更高的效率和生產(chǎn)力.pdf》資料免費(fèi)下載

2023-11-02 11:18:49 0

0 提高系統(tǒng)的性能和可靠性。 一、晶振布局優(yōu)化 1. 位置選擇:晶振應(yīng)盡量靠近主要使用它的電路,縮短傳輸距離,減少信號的干擾和損耗。同時應(yīng)盡量遠(yuǎn)離干擾源,如高頻電路、開關(guān)電源等。 2. 地址線和控制線的分離:保持晶振的引腳

2023-12-18 14:09:22 257

257 任務(wù)是將邏輯元件與連接線路進(jìn)行合理的布局和布線,以實(shí)現(xiàn)性能優(yōu)化和電路連接的可靠性。然而,FPGA布局布線的過程通常是一項(xiàng)繁瑣且耗時的任務(wù),因此加速布局布線算法的研究具有重要意義。本文將詳盡探討FPGA布局布線算法加速的方法與技術(shù),分析其理論基礎(chǔ)和實(shí)踐應(yīng)用。 FPGA布局布

2023-12-20 09:55:13 200

200

電子發(fā)燒友App

電子發(fā)燒友App

評論