PicoBlaze 是一款結構緊湊的8 位軟核微控制器,FPGA工程師可在其所選的賽靈思FPGA 中對其進行實例化。一旦實現,該處理器完全包含到僅使用邏輯Slice 和Block RAM 的FPGA 架構中;無需外部易失性和非易失性存儲器。

由于其實現方案封裝面積小,FPGA 才可能容納多個PicoBlaze 實例化。每個實例化用于實現通常由狀態機創建的控制結構。這樣不僅能縮短開發時間,而且還可用標準化方法來控制結構生成。由于賽靈思FPGA結構潛在的高性能,PicoBlaze 實例化往往能夠超越許多分離式8 位微控制器。

下面讓我們看看如何在我們的設計中充分利用這款便捷的器件。

PICOBLAZE 架構

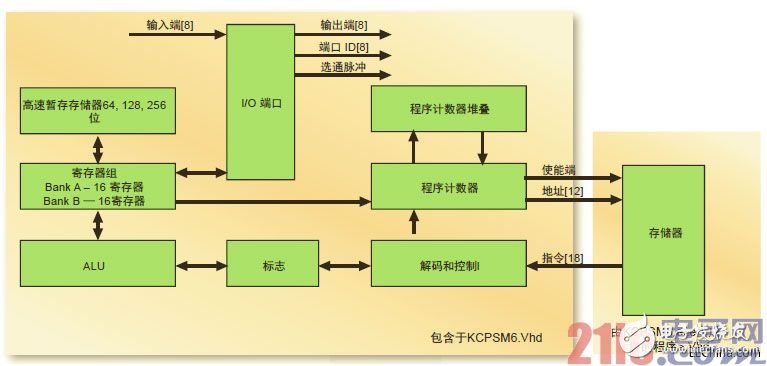

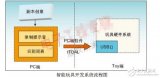

在使用這個處理器之前,首先讓我們了解一下它的架構。PicoBlaze 是一款基于RISC 架構的非常簡單的8 位微控制器(如圖1 所示)。該控制器有一個12 位的地址端口,這意味著它可以處理多達4096 個存儲器位置。

圖1 – PicoBlaze架構,處理器(左)和存儲器(右)

每個地址位置包括一個18 位指令,用以定義該處理器必須執行的操作。該處理器的輸入輸出可能通過兩個8位端口(一個輸入端口,一個輸出端口)。該控制器還提供了一個8 位識別端口,可讓多達256 個外設通過該端口進行讀寫。此外,該控制器還提

供一個64、128 或256 字節大小可選的高速暫存存儲器。跟所有微處理器一樣,PicoBlaze 包含一個算術邏輯單元并支持一個中斷。有了這些功能,意味著該控制器能夠為FPGA 設計工程師帶來眾多優勢。

PicoBlaze 最重要的一個方面是它具有高度的確定性,這意味著所有指令都需要兩個時鐘周期才能執行完畢,中斷服務最多需要四個時鐘周期。( 您可以通過下載賽靈思用戶指南,了解有關PicoBlaze 架構的更多詳情。)

如何使用PICOBLAZE?

FPGA 應用通常需要結合并行和時序操作,其中數據流主要采用并行操作,而控制結構主要以時序結構實現,如狀態機。(參見《賽靈思中國通信》第46 期,“ 如何在您的FPGA 中實現狀態機”)。然而,復雜的控制結構如果以狀態機實現,可能會變得

難以處理,不僅會延長驗證時間,而且還會讓開發周期的后期修改變得困難重重。復雜的狀態機還需要花更多時間來開發,如果需要開發數個,那么花費時間就會相當長。

此外,您還可以使用PicoBlaze控制通過RS232、I2C 和SPI 接口的串行通信。事實上,您采用典型8位微處理器實現的任何方案均可在PicoBlaze 中實現, 而且具有更高的性能。工程師們已經用PicoBlaze 在控制系統中實現PID 控制器。他們結合使用PicoBlaze 與I2C、SPI 或并行DAC 來創建方形、鋸齒和三角形以及更復雜的正弦/ 余弦等各種參考波形(使用移位加CORDIC 算法)。在您的FPGA 中實例化PicoBlaze 微控制器來實現這些時序功能,不僅可縮短開發時間,而且還允許在開發周期的

后期階段進行簡單的修改。當然,作為軟核,PicoBlaze 還有助于解決過時問題,而且在您開發ASM 模塊時還支持設計重用。

首個PICOBLAZE 實例化

遵循以下幾個簡單步驟,您就可以在您的設計中快速實現PicoBlaze。首先,確保您將用于目標器件中的微控制器是最新版本。您可從賽靈思PicoBlaze 下載區下載這些微控制器產品,這里既提供支持最新7 系列器件的版本,又提供能與舊版Spartan?-3

和Virtex?-4 器件協同使用的微控制器版本。

當下載了正確的處理器版本后,將這些文件解壓到您的工作目錄下并確保您能讀取“read-me”文件,同時根據需要密切關注路徑的設置以及賽靈思的環境變量。在您的工作目錄中, 您將注意到以下文件或應用,以及有用的read-me 文件、許可證文件和用戶指南。

? KCPSM6.Vhd: 這是一個真正的PicoBlaze 源代碼。

? KCPSM6.exe :這是一個匯編程序,您可運用其生成所需的機器碼和存儲器文件。

? ROM_Form.vhd :這是一個可執行匯編程序,使用該文件可以生成VHDL 文件,您創建的程序將存儲在這里。

? KCPSM6_design_template vhd :這是一個PicoBlaze 處理器模板實例。

? All_kcpsm6_syntax.psm :這個文件是關于所有匯編程序命令和語法的定義。

對于我們的實例設計,如果你不想將PicoBlaze 及其程序存儲器添加到現有項目中,那么最后一步您應在我們能實例化PicoBlaze 及其程序存儲器的ISE? 設計套件中創建一個新的項目。

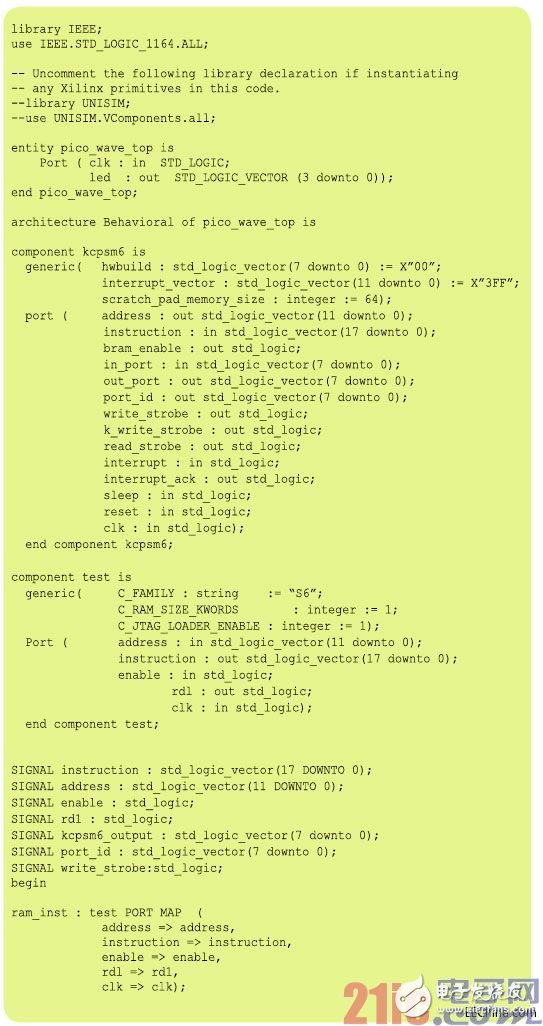

一旦完成上述步驟,我們就準備開始在我們的應用中創建PicoBlaze處理器。在此最簡單的層面上,您只需在您的設計中聲明兩個組件:一個是處理器本身,另一個是程序存儲器,如圖1 所示 ( 處理器位于左側方框中,存儲器位于右側方框中,用以提供上下文環境)。當然,如果您需要實現一個以上的實例化,那么您應該提供若干個存儲器組件,用于存儲不同的程序。然而,首先需要我們做的是了解典型項目的開發流程。

開發流程

創建首個PicoBlaze 實例其實很簡單。第一步,使用Notepad++ 之類的編輯器創建一個空白的文本文件。該文件應該具備一個 .PSM 的文件擴展名,比如像“test.psm”這樣的。您可以用PicoBlaze 匯編程序對微控制器進行編程。

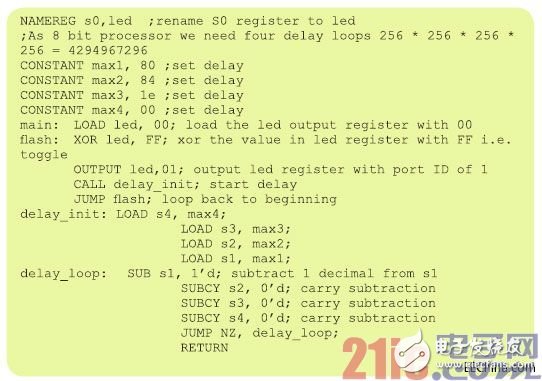

賽靈思在All_kcpsm6_ syntax.psm 文件中對該語法進行了詳細介紹,您可以自行下載。無論怎樣,這個語法很容易理解和掌握。圖2 是匯編程序代碼片段的示例,這是一個簡單程序,用以閃存運行頻率為2Hz、時鐘頻率為 40MHz 的LED。

圖2 – 用于項目閃存LED的匯編程序代碼片段

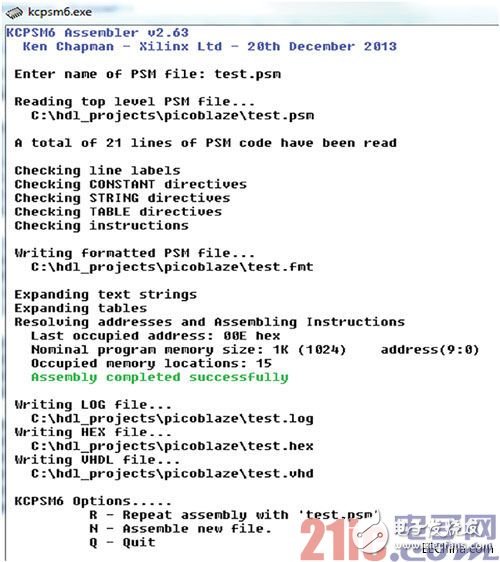

一旦您對自己的匯編程序感到滿意后,就可以進行下一步:通過您下載的匯編程序可執行文件運行該程序。這樣將會生成一個存儲器文件 (您的FPGA 中會用到的VHDL)、一個日志文件和一個十六進制文件,我們將在后文介紹它們的用途。圖3 顯示了針對上述代碼片段所運行的匯編程序流程。一旦運行匯編程序,您現在就能夠在您的FPGA 內實例化PicoBlaze。

圖3 –使用KCPSM6匯編程序生成存儲器文件

您現在擁有兩個所需的VHDL文件:KCPSM6.vhd 和由匯編程序創建的包含您的應用的VHDL 文件( 在本例中為test.vhd)。第二步:

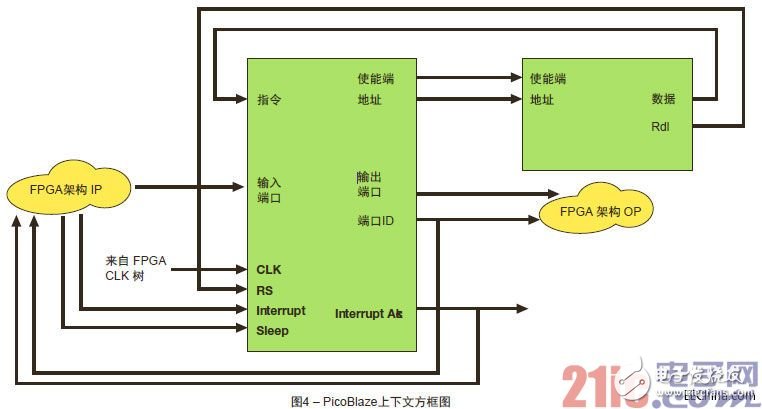

在您的VHDL 設計中聲明兩個組件(KCPSM6 和Memory) 并對他們進行實例化(如圖4 所示)。在圖5 所示的代碼片段中可以看到這個簡單的VHDL 示例。這個VHDL 示例實現的PicoBlaz 可以將LED 閃存到LX9Spartan? 開發板上。

圖4 – PicoBlaze上下文方框圖

圖5 –將LED閃存到LX9 Spartan開發板上的PicoBlaze的代碼片段

仿真與驗證

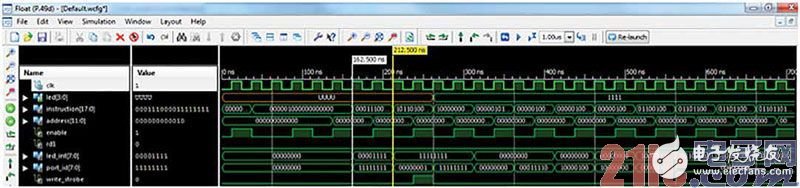

一旦您在應用中完成了設計文件的實例化,您肯定希望能在綜合和實現之前在仿真環境中驗證一下該系統或模塊的性能。由于PicoBlaze 使用的是邏輯Slice 和 Block RAM,所以您在Mentor Graphics 的Mod-elSim 或賽靈思ISE 中的ISim ( 如果您是在

Vivado? 設計套件中的Xsim 中實現您的PicoBlaze,也可使用Xsim) 等程序中進行仿真就極其簡單。

由于Block RAM 包含有針對您程序的指令,所以仿真工作自然就簡單。基本上,您只需要提供一個時鐘以及實例化要求的其他輸入輸出。圖6 顯示了在ISim 中進行的PicoBlaze仿真結果,以及指令加載之間的兩個時鐘周期。

圖6 – ISim仿真結果

圖6 – ISim仿真結果

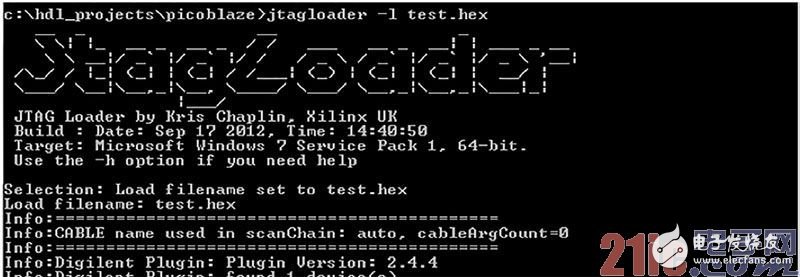

升級您的程序

在FPGA( 以及比特文件) 中內置PicoBlaze 的最大優勢之一就是在FPGA 配置完成后PicoBlaze 開始直接在其RAM 中運行程序。然而,在某些情況下,您可能需要修改該處理器核正在執行的程序。雖然根據設計余下部分的復雜程度,您可能會重新運行Implementation 階段(包括更新了的存儲器文件),但這會非常耗時,尤其是您只在實驗室里嘗試各種可能的情況下。因此,在重新運行Implementation 階段之前可以用JTAGloader 更新處理器 核的程序存儲器,來調試你的軟件程序。其中JTAG loader 也能通過下載獲得。

在使用JTAG loader 之前,首先需要在您的設計設置中啟用該加載程序。在一個程序存儲器的實例化中使用通用C_JTAG_LOAD-ER_ENABLE: integer := 1 。注意您一次只能為您設計中的一個內存實例設置該參數。

在您的設計中啟用該程序后,您必須從JTAG_loader 目錄中選擇和你的操作系統匹配的版本并將其復制到您的工作目錄下 ( 即十六進制文件所在位置)。現在您可以打開一個命令窗口并導航到您的工作目錄下,然后使用以下命令。

jtagloader –l .hex

注意:我已經我的操作系統重新命名為可執行文件版本,即jtagloader.exe。

當您在您的最新PSM 文件上運行匯編程序時,此項操作將下載所創建的十六進制文件,結果如圖7 所示。下載該文件后,您將注意到JTAGloader 會停止處理器執行并在釋放處理器復位之前下載新的程序到存儲器中,此時處理器開始運行新的程序。

一旦您對PSM 文件的更新行為感到滿意,您就可以重新運行實現方案和比特文件生成,從而確保下次該器件經過配置,能夠執行更新的程序。

電子發燒友App

電子發燒友App

評論