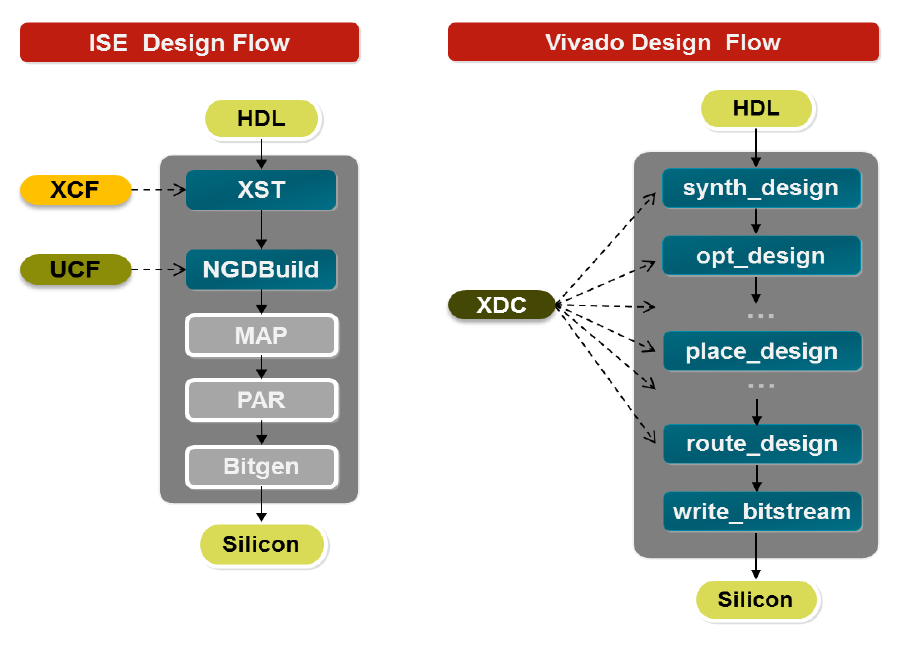

Xilinx的新一代設(shè)計(jì)套件Vivado相比上一代產(chǎn)品ISE,在運(yùn)行速度、算法優(yōu)化和功能整合等很多方面都有了顯著地改進(jìn)。但是對(duì)初學(xué)者來(lái)說(shuō),新的約束語(yǔ)言XDC以及腳本語(yǔ)言Tcl的引入則成為了快速掌握Vivado使用技巧的最大障礙,以至于兩年多后的今天,仍有很多用戶缺乏升級(jí)到Vivado的信心。

本文介紹了Tcl在Vivado中的基礎(chǔ)應(yīng)用,希望起到拋磚引玉的作用,指引使用者在短時(shí)間內(nèi)快速掌握相關(guān)技巧,更好地發(fā)揮Vivado在FPGA設(shè)計(jì)中的優(yōu)勢(shì)。

Tcl的背景介紹和基礎(chǔ)語(yǔ)法

Tcl(讀作tickle)誕生于80年代的加州大學(xué)伯克利分校,作為一種簡(jiǎn)單高效可移植性好的腳本語(yǔ)言,目前已經(jīng)廣泛應(yīng)用在幾乎所有的EDA工具中。Tcl 的最大特點(diǎn)就是其語(yǔ)法格式極其簡(jiǎn)單甚至可以說(shuō)僵化,采用純粹的 [命令 選項(xiàng) 參數(shù)] 形式,是名副其實(shí)的“工具命令語(yǔ)言”( 即Tcl的全稱Tool Command Language)。

實(shí)際上Tcl的功能可以很強(qiáng)大,用其編寫的程序也可以很復(fù)雜,但要在Vivado或大部分其它EDA工具中使用,則只需掌握其中最基本的幾個(gè)部分。

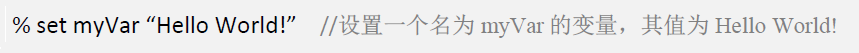

注: 在以下示例中,% 表示Tcl的命令提示符,執(zhí)行回車后,Tcl會(huì)在下一行輸出命令執(zhí)行結(jié)果。 // 后是作者所加注釋,并不是例子的一部分。

設(shè)置變量

打印主要通過(guò)puts語(yǔ)句來(lái)執(zhí)行,配合特殊符號(hào),直接決定最終輸出內(nèi)容。

文件I/O

可以看到Tcl對(duì)文件的操作也是通過(guò)設(shè)置變量,改變屬性以及打印命令來(lái)進(jìn)行的。上述寫文件的例子中通過(guò)puts命令在my_file.txt文件中寫入兩行文字,分別為“Hello World!” 和myVar變量的值,然后在讀文件操作中逐行讀取同一文件的內(nèi)容。

控制流和循環(huán)命令

Tcl語(yǔ)言中用于控制流程和循環(huán)的命令與C語(yǔ)言及其它高級(jí)語(yǔ)言中相似,包括if、while、for和foreach等等。

具體使用可以參考如下示例:

子程序/過(guò)程

Tcl中的子程序也叫做過(guò)程(Procedures),Tcl正是通過(guò)創(chuàng)建新的過(guò)程來(lái)增強(qiáng)其內(nèi)建命令的能力,提供更強(qiáng)的擴(kuò)展性。具體到Vivado的使用中,用戶經(jīng)常可以通過(guò)對(duì)一個(gè)個(gè)子程序/過(guò)程的創(chuàng)建來(lái)擴(kuò)展或個(gè)性化Vivado的使用流程。

一些特殊符號(hào)

Tcl語(yǔ)言的基本語(yǔ)法相對(duì)簡(jiǎn)單,但要熟練掌握仍需日常不斷練習(xí)。Xilinx網(wǎng)站上有很多相關(guān)資料,這里推薦兩個(gè)跟Tcl相關(guān)的文檔 UG835 和 UG894 ,希望對(duì)大家學(xué)習(xí)Vivado和Tcl有所幫助。

在Vivado中使用Tcl定位目標(biāo)

在Vivado中使用Tcl最基本的場(chǎng)景就是對(duì)網(wǎng)表上的目標(biāo)進(jìn)行遍歷、查找和定位,這也是對(duì)網(wǎng)表上的目標(biāo)進(jìn)行約束的基礎(chǔ)。要掌握這些則首先需要理解Vivado對(duì)目標(biāo)的分類。

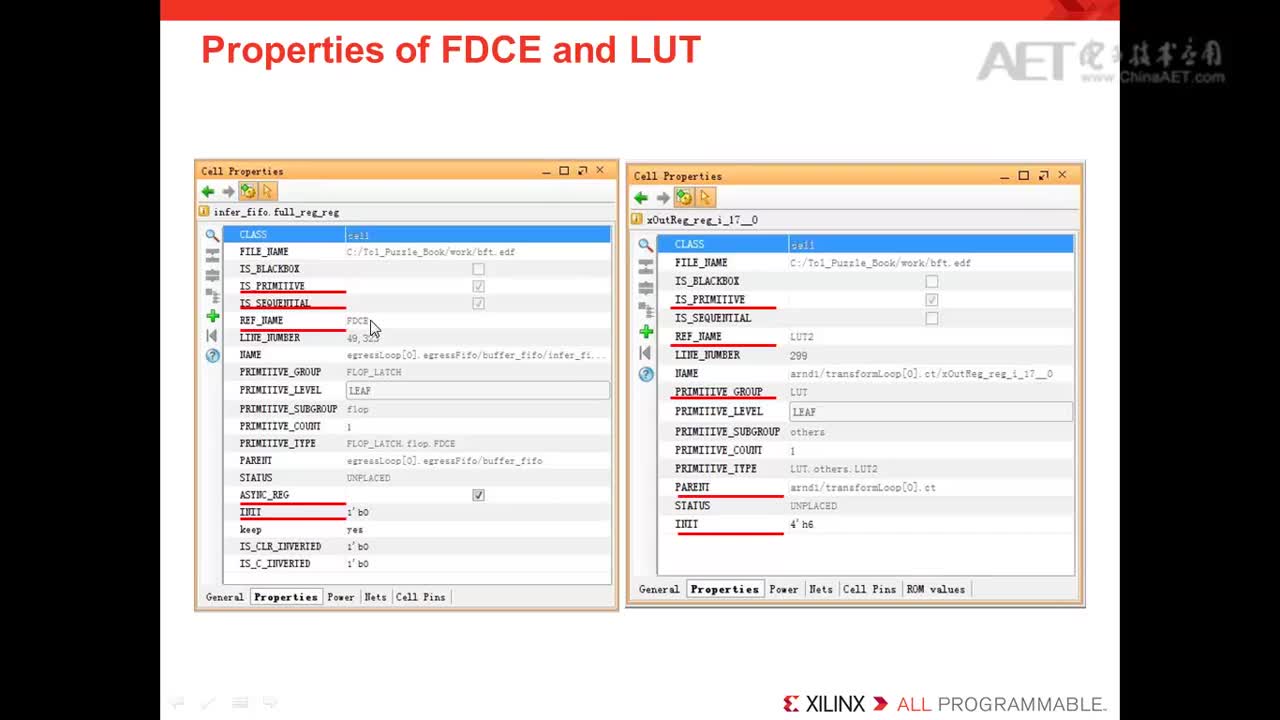

目標(biāo)的定義和定位

如上圖所示,設(shè)計(jì)頂層的I/O稱作ports,其余底層模塊或是門級(jí)網(wǎng)表上的元件端口都稱作pins。而包括頂層在內(nèi)的各級(jí)模塊,blackbox以及門級(jí)元件,都稱作cells。連線稱作nets,加上XDC中定義的clocks,在Vivado中一共將網(wǎng)表文件中的目標(biāo)定義為五類。要選取這五類目標(biāo),則需用相應(yīng)的get_*命令,例如get_pins等等。

get_ports

ports僅指頂層端口,所以get_ports的使用相對(duì)簡(jiǎn)單,可以配合通配符“* ”以及Tcl語(yǔ)言中處理list的命令一起使用。如下所示,

get_cells/get_nets

?

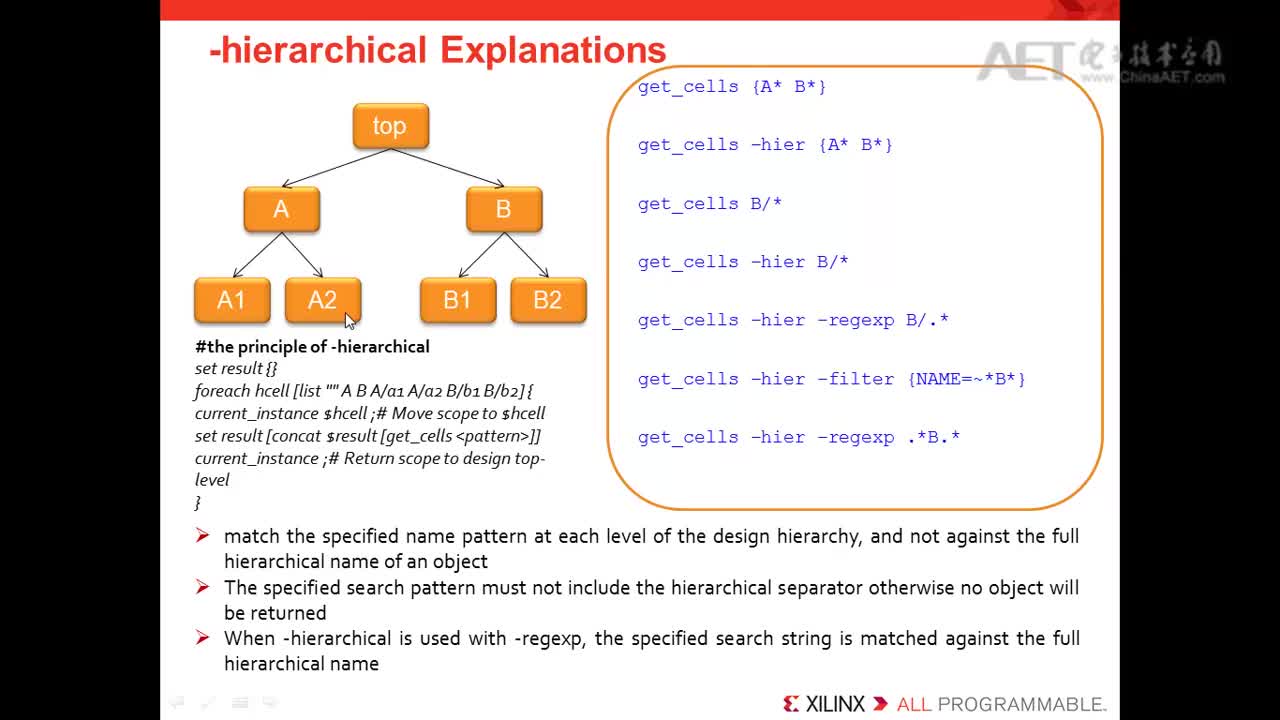

不同于ports僅指頂層端口,要定位cells和nets則相對(duì)復(fù)雜,首先需要面對(duì)層次的問(wèn)題。這里有個(gè)大背景需要明確:Vivado中Tcl/XDC對(duì)網(wǎng)表中目標(biāo)的搜索是層次化的,也就是一次僅搜索一個(gè)指定的層次current_instance,缺省值為頂層。

以下圖所示設(shè)計(jì)來(lái)舉例,若要搜索A(不含a1,a2)層次內(nèi)的所有cells和名字中含有nt的nets, 有兩種方法:

若要將搜索層次改為A+B+b1,則可以寫一個(gè)循環(huán),逐一用current_instance將搜索層次指向A,B和b1,再將搜索到的cells或nets合成一個(gè)list輸出即可。

若要將搜索層次改為當(dāng)前層次以及其下所有子層次,可以使用 -hierarchical (在Tcl中可以簡(jiǎn)寫為-hier )。

在使用-hierarchical時(shí)有一點(diǎn)需要特別留意,即后面所跟的搜索條件僅指目標(biāo)對(duì)象的名字,不能含有代表層次的“/” 。 下面列出的寫法便是一種常見(jiàn)的使用誤區(qū),并不能以此搜索到A及其下子層次內(nèi)所有的cells。

get_pins

pins在Vivado數(shù)據(jù)庫(kù)中有個(gè)獨(dú)特的存在形式,即 /

。這里的“/”不表示層次,而是其名字的一部分,表示這個(gè)pin所屬的實(shí)體。也就是說(shuō),在使用get_pins 配合-hier來(lái)查找pins時(shí),“/”可以作為名字的一部分,出現(xiàn)在搜索條件內(nèi)(注意與上述get_cells和get_nets的使用區(qū)別)。

目標(biāo)之間的關(guān)系

Tcl在搜索網(wǎng)表中的目標(biāo)時(shí),除了上述根據(jù)名字條件直接搜索的方式,還可以利用目標(biāo)間的關(guān)系,使用-of_objects(在Tcl中可以簡(jiǎn)寫為-of)來(lái)間接搜索特定目標(biāo)。Vivado中定義的五類目標(biāo)間的關(guān)系如下頁(yè)左圖所示。

以上示右圖的設(shè)計(jì)來(lái)舉例,

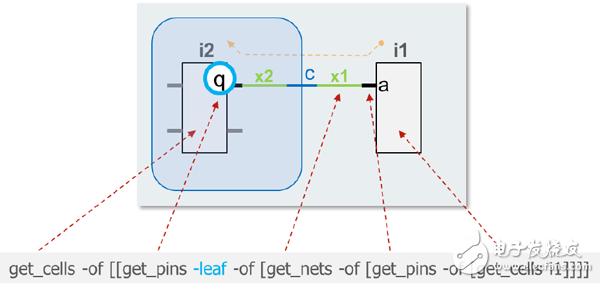

下圖是一個(gè)更復(fù)雜的示例,涉及跨層次搜索。可以看到在get_pins時(shí),要加上-leaf才能準(zhǔn)確定位到門級(jí)元件(或blackbox)的端口q。另外,在實(shí)際操作中,使用get_nets和get_pins時(shí),需要視情況而加上其它條件(-filter)才能準(zhǔn)確找到下述例子中的cells (i2)。

高級(jí)查找功能

在使用get_*命令查找網(wǎng)表中的目標(biāo)時(shí),除了名字這一直接條件,往往還需要輔以其它更復(fù)雜的條件判斷,這就需要用到高級(jí)查找功能:-filter 結(jié)合Tcl支持的各種關(guān)系和邏輯運(yùn)算符(==, !=, =~, !~, <=, >=, >, <, &&, ||)甚至是正則表達(dá)式來(lái)操作。

在創(chuàng)建子程序時(shí)也常常用到-filter,例如下述get_p的子程序/過(guò)程就可以用來(lái)返回指定管腳的方向?qū)傩裕嬖V用戶這是一個(gè)輸入管腳還是一個(gè)輸出管腳。

Tcl在Vivado中的延伸應(yīng)用

Tcl在Vivado中的應(yīng)用還遠(yuǎn)不止上述所列,其它常用的功能包括使用預(yù)先寫好的Tcl腳本來(lái)跑設(shè)計(jì)實(shí)現(xiàn)流程,創(chuàng)建高級(jí)約束(XDC不支持循環(huán)等高級(jí)Tcl語(yǔ)法)以及實(shí)現(xiàn)復(fù)雜的個(gè)性化設(shè)計(jì)流程等等。Tcl所帶來(lái)的強(qiáng)大的可擴(kuò)展性決定了其在版本控制、設(shè)計(jì)自動(dòng)化流程等方面具有圖形化界面不能比擬的優(yōu)勢(shì)。

Vivado在不斷發(fā)展更新的過(guò)程中,還有很多新的功能,包括ECO、PR、HD Flow等等都是從Tcl腳本方式開(kāi)始支持,然后再逐步放入圖形化界面中實(shí)現(xiàn)。這也解釋了為何高端FPGA用戶和熟練的Vivado用戶都更偏愛(ài)Tcl腳本。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論