親愛的先生,我們有一個(gè)項(xiàng)目,我們需要6個(gè)UART。所以我們計(jì)劃使用100引腳控制器。市場(chǎng)上可用的100引腳控制器是PIC24FJXXXGB610這個(gè)控制器包含6個(gè)UART,當(dāng)我看到數(shù)據(jù)表時(shí),它顯示

2020-05-14 08:36:53

10G以太網(wǎng)系統(tǒng)中的并行CRC編解碼器的設(shè)計(jì)

2012-08-10 17:59:00

的應(yīng)用可略見一斑。差錯(cuò)控制理論是在代數(shù)理論基礎(chǔ)上建立起來的。這里我們著眼于介紹CRC的算法與實(shí)現(xiàn),對(duì)原理只能捎帶說明一下。若需要進(jìn)一步了解線性碼、分組碼、循環(huán)碼、糾錯(cuò)編碼等方面的原理,可以閱讀有關(guān)資料

2010-09-20 12:13:14

FPGA實(shí)現(xiàn)的SATA控制器FPGA實(shí)現(xiàn)的SATA控制器

2012-08-11 18:08:52

問答選編問:Cortex-M1微控制器有哪些接口資源?答:Cortex-M1處理器掛在AHB總線上,AHB總線通過橋接邏輯可以掛APB總線,APB總線上可以掛的接口有IIC、UART、PWM、中斷

2019-07-26 07:46:51

;25.4.3 CRC 控制寄存器(CRC_CR)位 4:3 POLYSIZE[1:0]:多項(xiàng)式大小這些位控制多項(xiàng)式的大小。00:32 位多項(xiàng)式01:16位多項(xiàng)式10:8位多項(xiàng)式11:7位多項(xiàng)式"

2022-12-09 06:14:34

FPGA中的數(shù)字控制器是什么?System Generator中的PID控制器是如何設(shè)計(jì)的?

2021-04-08 06:51:46

Verilog并行CRC校驗(yàn)

2012-08-20 21:52:15

大家好,STM32L0 系列微控制器通過 UART 閃存,但 STM32G0 系列微控制器不是能夠通過 UART 閃爍。所以問題是“使用 UART 閃存 STM32G0 系列微控制器的方法是什么”

2022-12-21 06:02:40

分享如何利用FPGA設(shè)計(jì)幀存控制器的方法?從而去實(shí)現(xiàn)幀存的交替 、上電清屏等。

2021-04-08 06:19:05

。實(shí)際上,這種經(jīng)驗(yàn)很難以實(shí)際應(yīng)用。硬件的選擇受限于微控制器內(nèi)核的基本算法函數(shù),以及DSP內(nèi)核的乘法/累加和線性函數(shù)處理,雖然FPGA所具有更高靈活度,但其缺點(diǎn)是外形尺寸、功耗以及批量時(shí)的單位成本。可選

2008-09-27 11:42:55

DSP芯片組成并行處理系統(tǒng)。另外,為充分發(fā)揮 DSP芯片在復(fù)雜算法處理上的優(yōu)勢(shì)及FPGA在大數(shù)據(jù)量的底層算法上的優(yōu)勢(shì),設(shè)計(jì)了一種基于FPGA控制的多DSP并行處理系統(tǒng)。1 系統(tǒng)設(shè)計(jì)基于FPGA控制的多

2019-05-21 05:00:19

目前伺服控制器的設(shè)計(jì)多以DSP或MCU為控制核心,但DSP的靈活性不如FPGA,且在某些環(huán)境比較惡劣的條件如高溫高壓下DSP的應(yīng)用效果會(huì)大打折扣,因此以FPGA為控制核心,對(duì)應(yīng)用于機(jī)載三軸伺服控制平臺(tái)的控制器進(jìn)行了設(shè)計(jì)與優(yōu)化。

2019-07-16 07:41:04

基于FPGA的圖形式AMLCD控制器該如何去設(shè)計(jì)?怎樣去設(shè)計(jì)一種VGA視頻接口電路?

2021-06-08 06:57:57

現(xiàn)在市場(chǎng)上有基于FPGA的多電機(jī)運(yùn)動(dòng)控制器的成品嗎,注意是成品喲,成品!成品!成品!

2016-01-19 11:22:17

剛剛開始入門FPGA,現(xiàn)在想做基于FPGA的智能溫度采集控制器設(shè)計(jì),各位大神誰做過這個(gè)設(shè)計(jì),能不能把包給我!!謝謝了,我qq985984834

2014-02-18 15:50:32

轉(zhuǎn)帖摘要: 針對(duì)嵌入式軟件無法滿足數(shù)字圖像實(shí)時(shí)處理速度問題,提出用硬件加速器的思想,通過FPGA實(shí)現(xiàn)Sobel邊緣檢測(cè)算法。通過乒乓操作、并行處理數(shù)據(jù)和流水線設(shè)計(jì),大大提高算法的處理速度。采用模塊

2017-11-29 08:57:04

傳統(tǒng)數(shù)字濾波器硬件的實(shí)現(xiàn)主要采用專用集成電路(ASIC)和數(shù)字信號(hào)處理器(DSP)來實(shí)現(xiàn)。FPGA內(nèi)部的功能塊中采用了SRAM的查找表(lo-ok up table,LUT)結(jié)構(gòu),這種結(jié)構(gòu)特別適用于并行處理結(jié)構(gòu),相對(duì)于傳統(tǒng)方法來說,其并行度和擴(kuò)展性都很好,它逐漸成為構(gòu)造可編程高性能算法結(jié)構(gòu)的新選擇。

2019-10-22 07:14:04

哪位大俠可以提供基于ADC0832與FPGA的采樣控制器的設(shè)計(jì)思路,萬分感謝!!!最好可以提供采樣精度算法、中斷控制流程

2013-12-28 20:11:06

在很多嵌入式控制系統(tǒng)中,系統(tǒng)既要完成大量的信息采集和復(fù)雜的算法,又要實(shí)現(xiàn)精確的控制功能。采用運(yùn)行有嵌入式Linux操作系統(tǒng)的ARM9微控制器完成信號(hào)采集及實(shí)現(xiàn)上層控制算法,并向DSP芯片發(fā)送上層算法得到控制參數(shù),DSP芯片根據(jù)獲得的參數(shù)和下層控制算法實(shí)現(xiàn)精確、可靠的閉環(huán)控制。

2019-08-19 06:29:34

(FPGA)作為核心處理器的協(xié)處理架構(gòu)的開放式運(yùn)動(dòng)控制器。該控制器將PC機(jī)和DSP的信息處理能力與FPGA的外圍擴(kuò)展功能很好的結(jié)合在一起,具有信息處理能力強(qiáng)、模塊化、開放程度高、運(yùn)動(dòng)軌跡控制精確等優(yōu)點(diǎn)。

2019-09-04 07:10:42

(FPGA)作為核心處理器的協(xié)處理架構(gòu)的開放式運(yùn)動(dòng)控制器。該控制器將PC機(jī)和DSP的信息處理能力與FPGA的外圍擴(kuò)展功能很好的結(jié)合在一起,具有信息處理能力強(qiáng)、模塊化、開放程度高、運(yùn)動(dòng)軌跡控制精確等優(yōu)點(diǎn)。

2019-08-30 08:27:17

控制器越來越多地運(yùn)用在運(yùn)動(dòng)控制系統(tǒng)中,具有較高的集成度和靈活性,可實(shí)時(shí)完成運(yùn)動(dòng)控制過程中復(fù)雜的邏輯處理和控制算法,能實(shí)現(xiàn)多軸高速高精度的伺服控制。本文選用DSP與FPGA作為運(yùn)動(dòng)控制器的核心部件,設(shè)計(jì)了

2009-09-19 09:43:00

請(qǐng)教一下,基于DSP和FPGA的嵌入式控制器該如何去設(shè)計(jì)?

2021-05-06 09:16:19

基于查表法的快速CRC算法設(shè)計(jì)

2012-08-20 20:01:16

本文提出了一種基于FPGA的SDRAM控制器的設(shè)計(jì)方法,并用Verilog給于實(shí)現(xiàn),仿真結(jié)果表明通過該方法設(shè)計(jì)實(shí)現(xiàn)的控制器可以在FPGA芯片內(nèi)組成如圖1所示的SDRAM接口,從而使得系統(tǒng)用戶對(duì)SDRAM的操作非常方便。

2021-04-15 06:46:56

你好,我正在使用連接到TMS320F28335 DSP的XC7A35T FPGA。有沒有辦法將位流CRC存儲(chǔ)在FPGA中,然后使用DSP進(jìn)行讀取?我想為每個(gè)版本生成一個(gè)新的固件版本號(hào),將版本號(hào)存儲(chǔ)在FPGA中,然后使用微控制器讀取它。我該怎么做謝謝。斯蒂芬

2020-06-10 14:58:29

的邏輯處理和控制算法,能實(shí)現(xiàn)多軸高速高精度的伺服控制。利用DSP與FPGA設(shè)計(jì)運(yùn)動(dòng)控制器,其中DSP用于運(yùn)動(dòng)軌跡規(guī)劃、速度控制及位置控制等功能;FPGA完成運(yùn)動(dòng)控制器的精插補(bǔ)功能,用于精確計(jì)算步進(jìn)電機(jī)或伺服驅(qū)動(dòng)元件的控制脈沖,同時(shí)接收并處理脈沖型位置反饋信號(hào)。那么,我們具體該怎么做呢?

2019-08-06 06:27:00

基于FPGA的SDRAM控制器包括哪些部分呢?如何去實(shí)現(xiàn)一種基于FPGA的SDRAM控制器設(shè)計(jì)呢?

2021-11-04 06:47:44

請(qǐng)問如何將8051微控制器引到FPGA中去?

2021-04-28 06:41:17

為 STSPIN 提供的 6 步算法。我們應(yīng)該將該代碼移植到任何其他 ST 控制器嗎?如何將BLDC進(jìn)電機(jī)控制算法移植到STM微控制器上呢?

2023-01-17 08:54:28

晚上好,如何將微控制器與FPGA連接?如何使用微控制器配置FPGA?如何使用微控制器或軟件程序?yàn)?b class="flag-6" style="color: red">FPGA創(chuàng)建.bit文件以使用微控制器配置FPGA?任何人都可以告訴發(fā)送與這些排隊(duì)相關(guān)的文件....提前致謝問候Vimala

2020-03-25 09:22:18

本文介紹通過FPGA實(shí)現(xiàn)的步進(jìn)電機(jī)控制器。該控制器可以作為單片機(jī)或DSP的一個(gè)直接數(shù)字控制的外設(shè),只需向控制器的控制寄存器和分頻寄存器寫入數(shù)據(jù),即可實(shí)現(xiàn)對(duì)步進(jìn)電機(jī)的控制。

2021-04-29 06:05:44

問候語!我想使用PIC18F控制器的外部并行SRAM。但是我有2個(gè)UART接口激活,我想把數(shù)據(jù)安全地送到外部SRAM。并且數(shù)據(jù)應(yīng)該由控制器來計(jì)算。因此,我有3個(gè)進(jìn)程必須訪問SRAM。我可以整理這個(gè)

2019-04-02 09:55:26

本文介紹一種使用硬件描述語言VHDL來實(shí)現(xiàn)基于Petri網(wǎng)的并行控制器的方法。首先使用Petri網(wǎng)對(duì)問題進(jìn)行建模,并對(duì)模型進(jìn)行分析和控制,獲得控制器的Petri網(wǎng)模型;然后用VHDL對(duì)Petri網(wǎng)

2019-08-16 07:52:03

國內(nèi)普遍采用TM320系列的DSP器件作為永磁同步電機(jī)控制系統(tǒng)的主控制器,因CPU負(fù)載過重導(dǎo)致系統(tǒng)實(shí)時(shí)性降低的問題日益顯著。采用具有并行工作特性的FPGA器件作為主控制器能夠提高系統(tǒng)實(shí)時(shí)性。因此,我們具體該怎么設(shè)計(jì)呢?

2019-08-14 08:02:56

本文采用Verilog FPGA設(shè)計(jì)懸掛運(yùn)動(dòng)控制系統(tǒng)的控制器,通過輸入模塊傳送控制參數(shù),采用HDL語言編程實(shí)現(xiàn)的控制算法,驅(qū)動(dòng)步進(jìn)電機(jī),對(duì)懸掛運(yùn)動(dòng)物體進(jìn)行精確的控制。

2021-05-06 07:11:03

課程設(shè)計(jì)。俺菜鳥,時(shí)間來不及了。在這里求大神們幫忙下。求基于FPGA的uart控制器的設(shè)計(jì)和仿真用Verilog將完整的程序編寫,QuartusII軟件上進(jìn)行仿真。這個(gè)應(yīng)該不算難不過時(shí)間來不及了。q 136201727如果有的話可以發(fā)一下么第一次發(fā)帖 不知道合不合規(guī)矩請(qǐng)諒解

2013-04-04 14:34:48

目前我們?cè)谝粋€(gè)項(xiàng)目中使用 STM32G473CC 控制器,我們?cè)谄渲惺褂?CAN 模塊(CAN 2.0 模式)以及 UART1/LPUART1 等外圍設(shè)備。我們?cè)?CAN 驅(qū)動(dòng)程序之上集成了 CAN

2022-12-12 08:29:48

如何去設(shè)計(jì)模糊PID自整定控制器?關(guān)于模糊控制器算法的研究是什么?模糊PID控制器具有哪些特點(diǎn)?

2021-04-21 06:08:28

基于FPGA的MCU設(shè)計(jì)有兩種基本實(shí)現(xiàn)方式如何實(shí)現(xiàn)微控制器與FPGA的接口設(shè)計(jì)

2021-05-06 10:05:17

,本文的目標(biāo)是介紹CRC算法的基本原理和實(shí)現(xiàn)方式,用到的數(shù)學(xué)盡量控制在高中生可以理解的深度。另外,鑒于大多數(shù)嵌入式程序員都是半路出家轉(zhuǎn)行過來的,不少人只會(huì)C語言。因此,文中的示例代碼全部采用C語言來

2016-08-01 18:32:16

和靈活性,可實(shí)時(shí)完成運(yùn)動(dòng)控制過程中復(fù)雜的邏輯處理和控制算法,能實(shí)現(xiàn)多軸高速高精度的伺服控制。本文選用DSP與FPGA作為運(yùn)動(dòng)控制器的核心部件,設(shè)計(jì)了通用型運(yùn)動(dòng)控制器。其中DSP用于運(yùn)動(dòng)軌跡規(guī)劃、速度控制

2019-07-31 08:15:26

雖說懂原理,但是這算法還不理解/*******************************************************************//**//*DS18B20

2014-04-25 15:17:17

介紹了CRC(循環(huán)冗余碼校驗(yàn))原理及集成混合信號(hào)片上系統(tǒng)單片機(jī)C8051F的新特性,推導(dǎo)獲得以字節(jié)為單位的數(shù)據(jù)序列CRC碼遞推算法,利用C8051F單片機(jī)的自帶CAN2.0B總線接口控制器可以很

2009-03-14 08:39:50 46

46 本文從理論上推導(dǎo)出CRC 算法實(shí)現(xiàn)原理,給出三種分別適應(yīng)不同計(jì)算機(jī)或微控制器硬件環(huán)境的C 語言程序。讀者更能根據(jù)本算法原理,用不同的語言編寫出獨(dú)特風(fēng)格更加實(shí)用的CRC 計(jì)算

2009-07-20 15:27:14 32

32 文章介紹了一種在現(xiàn)場(chǎng)可編程門陣列(FPGA)上實(shí)現(xiàn)UART 的方法。UART 的波特率可設(shè)置調(diào)整,工作狀態(tài)可讀取。系統(tǒng)結(jié)構(gòu)進(jìn)行了模塊化分解,使之適應(yīng)自頂向下(Top-Down)的設(shè)計(jì)

2009-08-21 11:35:03 52

52 CRC算法原理及C語言實(shí)現(xiàn):本文從理論上推導(dǎo)出CRC 算法實(shí)現(xiàn)原理,給出三種分別適應(yīng)不同計(jì)算機(jī)或微控制器硬件環(huán)境的C 語言程序。讀者更能根據(jù)本算法原理,用不同的語言編寫出獨(dú)特

2009-09-23 23:38:50 31

31 UART 是廣泛使用的串行數(shù)據(jù)通訊電路。本設(shè)計(jì)包含UART 發(fā)送器、接收器和波特率發(fā)生器。設(shè)計(jì)應(yīng)用EDA 技術(shù),基于FPGA/CPLD 器件設(shè)計(jì)與實(shí)現(xiàn)UART。關(guān)鍵詞 :FPGA/CPLD;UART;VHDLUART(即U

2009-09-29 08:01:20 23

23 針對(duì)工業(yè)控制系統(tǒng)中的特殊應(yīng)用,提出利用CRC校驗(yàn)方法提高通信可靠性,并著重介紹了CRC校驗(yàn)原理及在工業(yè)控制網(wǎng)絡(luò)中的實(shí)現(xiàn)方法,重點(diǎn)闡述了查表法的CRC實(shí)現(xiàn),同時(shí)給出余式項(xiàng)的生成

2011-04-03 19:30:07 46

46 為了實(shí)現(xiàn)軍航管制系統(tǒng)中雷達(dá)數(shù)據(jù)的可靠傳輸,根據(jù) HDLC 協(xié)議的幀結(jié)構(gòu)和循環(huán)冗余校驗(yàn)(CRC)原理,提出了一種新型的基于并行機(jī)制的HDLC協(xié)議控制器,討論采用FPGA新技術(shù)實(shí)現(xiàn)HDLC協(xié)議幀的構(gòu)成

2011-07-20 16:17:50 93

93 循環(huán)冗余碼校驗(yàn) CRC (Cyclic Redundancy Check) 廣泛用于通訊領(lǐng)域和數(shù)據(jù)存儲(chǔ)的數(shù)據(jù)檢錯(cuò)。基于FPGA在通訊領(lǐng)域和數(shù)據(jù)存儲(chǔ)的應(yīng)用越來越廣泛,CRC的編碼解碼模塊已經(jīng)是FPGA上的常用模塊了。采

2011-08-15 11:19:57 40

40 針對(duì)大數(shù)據(jù)量的串口間通信,在常規(guī)的UART串行數(shù)據(jù)通信的基礎(chǔ)上,結(jié)合Cortex-M3微控制器中DMA控制器的作用,實(shí)現(xiàn)DMA控制的UART串口數(shù)據(jù)包收發(fā)。設(shè)計(jì)鏈表項(xiàng)緩存,最終實(shí)現(xiàn)DMA的分散/聚集

2012-04-20 10:54:07 46

46 基于解決Xmodem協(xié)議中CRC校驗(yàn)的目的,以經(jīng)典的LFSR硬件電路為基礎(chǔ),采用了按字節(jié)并行運(yùn)算CRC校驗(yàn)碼,以及多字節(jié)CRC算法的方法。在Quartus II環(huán)境下,通過以VHDL語言仿真試驗(yàn),得出Xmodem協(xié)

2012-05-07 15:29:01 47

47 設(shè)計(jì)了一種基于DSP與FPGA的運(yùn)動(dòng)控制器。該控制器以DSP為控制核心,用FPGA構(gòu)建運(yùn)動(dòng)控制器與傳感器以及電機(jī)驅(qū)動(dòng)器的接口電路。充分發(fā)揮了DSP強(qiáng)大的運(yùn)算能力和FPGA的并行處理能力。具有

2012-10-26 15:21:51 93

93 在介紹CRC校驗(yàn)原理和傳統(tǒng)CRC32串行比特算法的基礎(chǔ)上,由串行比特型算法推導(dǎo)出一種CRC32并行算法。并結(jié)合SATAⅡ協(xié)議的要求,完成了SATAⅡ主控制器設(shè)計(jì)中CRC生成與校驗(yàn)?zāi)K的設(shè)計(jì)。最后

2012-11-07 16:19:37 54

54 運(yùn)用低功耗C0rtex-M3微控制器STM32F103VBT6和FPGA芯片設(shè)計(jì)一種基于CAN總線的運(yùn)動(dòng)控制器。介紹系統(tǒng)的體系結(jié)構(gòu)、主要硬件設(shè)計(jì)和軟件結(jié)構(gòu)。利用FPGA高速處理能力實(shí)現(xiàn)控制算法,與外界通信采

2013-01-31 14:33:39 45

45 介紹了一種基于FPGA的多軸控制器,控制器主要由ARM7(LPC2214)和FPGA(EP2C5T144C8)及其外圍電路組成,用于同時(shí)控制多路電機(jī)的運(yùn)動(dòng)。利用Verilog HDL 硬件描述語言在FPGA中實(shí)現(xiàn)了電機(jī)控制邏

2013-04-27 16:23:11 82

82 基于 FPGA的LCD控制器設(shè)計(jì)的論文。

2015-10-29 14:05:37 17

17 利用查表法實(shí)現(xiàn)CRC算法,CRC算法廣泛應(yīng)用與各行業(yè),查表法實(shí)現(xiàn)CRC簡(jiǎn)單快速方便

2016-01-06 11:29:49 15

15 Xilinx FPGA工程例子源碼:在FPGA上實(shí)現(xiàn)CRC算法的程序

2016-06-07 15:07:45 28

28 基于FPGA的LED屏控制器設(shè)計(jì)基于FPGA的LED屏控制器設(shè)計(jì)

2016-06-21 17:56:39 50

50 基于FPGA的嵌入式多核處理器及SUSAN算法并行化

2016-08-30 18:11:47 24

24 16位CRC校驗(yàn)原理與算法分析,感興趣的小伙伴們可以看看。

2016-10-10 14:55:44 10

10 針對(duì)高速網(wǎng)絡(luò)通信中高位寬并行數(shù)據(jù)的實(shí)時(shí)校驗(yàn)需求,提出了一種可單周期實(shí)現(xiàn)的、面向128位并行數(shù)據(jù)的循環(huán)冗余校驗(yàn)算法(Cyclic Redundancy Check,CRC )。該算法首先根據(jù)CRC

2017-10-30 16:39:25 3

3 。CRC的實(shí)現(xiàn)方式分為串行方式和并行方式,由于并行方式一個(gè)時(shí)鐘周期內(nèi)可以處理8個(gè)bit,與千兆以太網(wǎng)的C;MIl接口協(xié)議相符合,故千兆以太網(wǎng)的CRC校驗(yàn)碼的生成和校驗(yàn)中常使用并行算法實(shí)現(xiàn)。本文研究了CRC校驗(yàn)碼的串行實(shí)現(xiàn)算法和并行實(shí)現(xiàn)算法,并且

2017-11-13 14:20:47 12

12 傳統(tǒng)的基于模擬退火的現(xiàn)場(chǎng)可編程門陣列( FPGA)時(shí)序驅(qū)動(dòng)布局算法在時(shí)延代價(jià)的計(jì)算上存在一定誤差,已有的時(shí)序優(yōu)化算法能夠改善布局質(zhì)量,但增加了時(shí)耗。針對(duì)上述問題,提出一種基于事務(wù)內(nèi)存( TM)的并行

2018-02-26 10:09:04 0

0 實(shí)現(xiàn)RS-232電平和TTL/CMOS電平轉(zhuǎn)換可以用接口芯片來實(shí)現(xiàn),實(shí)現(xiàn)數(shù)據(jù)的串行到并行轉(zhuǎn)換用的是UART,它們是實(shí)現(xiàn)串行通信必不可少的兩個(gè)部分。雖然目前大部分處理器芯片中都集成了UART,但是一般

2019-10-18 07:54:00 2317

2317

介紹了CRC(循環(huán)冗余碼校驗(yàn))原理及集成混合信號(hào)片上系統(tǒng)單片機(jī)C8051F的新特性,推導(dǎo)獲得以字節(jié)為單位的數(shù)據(jù)序列CRC碼遞推算法,利用C8051F單片機(jī)的自帶CAN2.0B總線接口控制器可以很方便

2019-12-17 16:09:41 17

17 UART作為RS232協(xié)議的控制接口得到了廣泛的應(yīng)用,將UART的功能集成到FPGA芯片中,可使整個(gè)系統(tǒng)更為靈活、緊湊,減小整個(gè)電路的體積,提高系統(tǒng)的可靠性和穩(wěn)定性。提出了一種基于FPGA

2020-07-07 15:51:05 7

7 UART作為RS232協(xié)議的控制接口得到了廣泛的應(yīng)用,將UART的功能集成到FPGA芯片中,可使整個(gè)系統(tǒng)更為靈活、緊湊,減小整個(gè)電路的體積,提高系統(tǒng)的可靠性和穩(wěn)定性。提出了一種基于FPGA的UART

2020-07-07 17:28:03 10

10 為了實(shí)現(xiàn)軍航管制系統(tǒng)中雷達(dá)數(shù)據(jù)的可靠傳輸,根據(jù)HDLC協(xié)議的幀結(jié)構(gòu)和循環(huán)冗余校驗(yàn)(CRC)原理,提出了一種新型的基于并行機(jī)制的HDLC協(xié)議控制器,討論采用FPGA新技術(shù)實(shí)現(xiàn)HDLC協(xié)議幀的構(gòu)成

2020-11-04 18:04:10 15

15 出了四核心嵌入式并行處理器FPEP的結(jié)構(gòu)設(shè)計(jì)并建立了FPGA驗(yàn)證平臺(tái).為了對(duì)多核處理器平臺(tái)性能進(jìn)行評(píng)測(cè),提出了基于OpenMP的3種可行的圖像處理領(lǐng)域的經(jīng)典算法SUSAN算法的并行化方法:直接并行

2021-02-03 16:26:00 8

8 在數(shù)據(jù)通信中, 提高數(shù)據(jù)在通信中的可靠性,以及快速的數(shù)據(jù)處理能力一直是人們所追求的,循環(huán)冗余校驗(yàn)CRC就是一種廣泛采用的差錯(cuò)控制方法,也是一種最常用的信道編碼方法。在介紹CRC碼原理之后,以經(jīng)典

2021-03-10 15:50:00 14

14 的高速CRC并行吏現(xiàn)遞推公式,可適用于并行處理位寬小于等于生成多項(xiàng)式階數(shù)和大于生成多項(xiàng)式階數(shù)條件下的并行幀校驗(yàn)應(yīng)用。最后分別設(shè)計(jì)了這2種條件下的硬件實(shí)現(xiàn)電路,電路的綜臺(tái)結(jié)果表明,該方法具有更步的資源占用量和更高的工作

2021-03-23 15:44:59 13

13 CRC校驗(yàn)的實(shí)現(xiàn)基于串行位移寄存器,如果要處理并行數(shù)據(jù),需要對(duì)電路進(jìn)行改進(jìn)。本文介紹了一種并行CRC電路HDL代碼的快速生成鐘算法,只需要帶入不同的參數(shù),可自動(dòng)生成不同長(zhǎng)度以及并行度的并行CRC電路的HDL代碼。

2021-03-28 09:29:50 15

15 文章介紹了用于 USB 總線數(shù)據(jù)傳輸?shù)?b class="flag-6" style="color: red">CRC 校驗(yàn)的原理和算法,并且采用并行電路實(shí)現(xiàn) USB2.0 中的 CRC產(chǎn)生和CRC校驗(yàn),與傳統(tǒng)的串行電路實(shí)現(xiàn)相比,并行電路實(shí)現(xiàn)方法雖然在芯片面積上大于串行電路實(shí)現(xiàn), 但由于降低了時(shí)鐘頻率,電路更容易綜合實(shí)現(xiàn),并且大大降低了功耗,有利于低功耗電路設(shè)計(jì)。

2021-03-28 09:32:27 11

11 用軟件實(shí)現(xiàn) CRC 校驗(yàn)碼計(jì)算很難滿足高速數(shù)據(jù)通信的要求 ,基于硬件的實(shí)現(xiàn)方法中 ,有串行經(jīng)典算法 LFSR 電路 以及由軟件算法推導(dǎo)出來的其它各種并行計(jì)算方法。以經(jīng)典的LFSR 電路為基礎(chǔ) ,研究

2021-03-28 09:34:24 30

30 EE-296:在SHARC?處理器上使用UART端口控制器

2021-04-26 10:19:17 2

2 CRC校驗(yàn)算法原理及c語言實(shí)現(xiàn)

2021-11-30 10:04:07 8

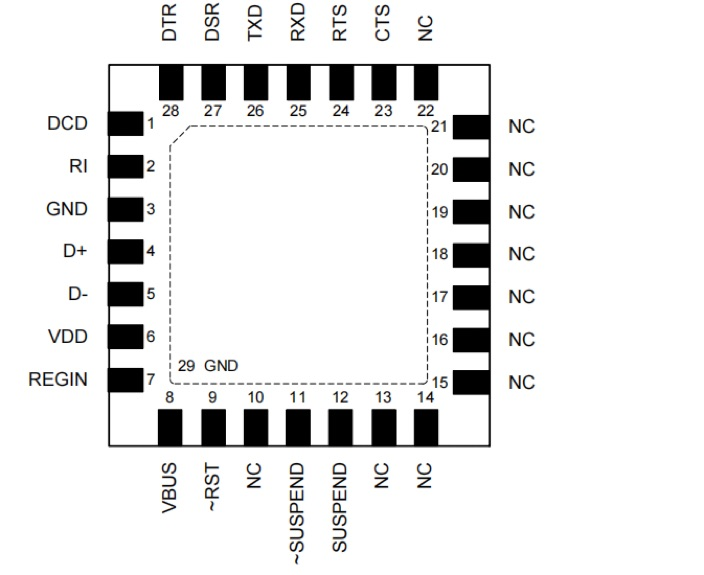

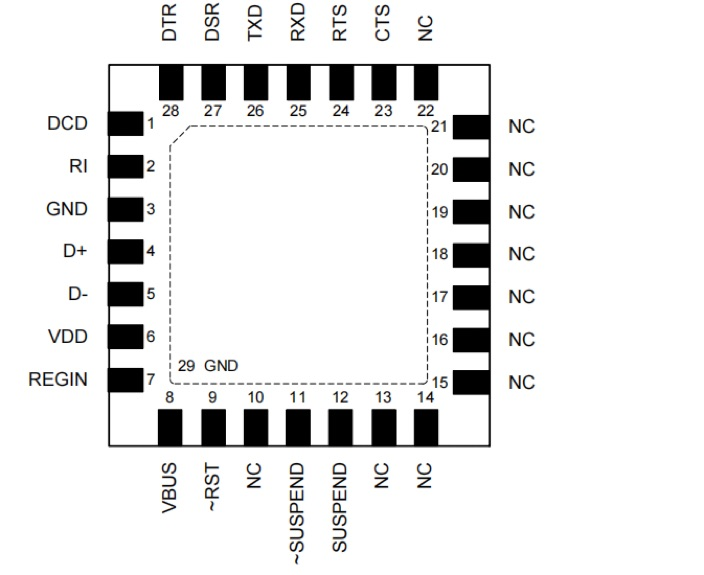

8 DPU02是一個(gè)高度集成的USB轉(zhuǎn)UART的橋接控制器,可將RS-232設(shè)計(jì)更新為USB設(shè)計(jì),并簡(jiǎn)化PCB組件空間。

2022-12-16 11:53:14 716

716

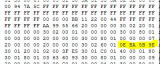

摘要:本文從一已提出的通用數(shù)學(xué)表達(dá)式出發(fā),研究了一種并行循環(huán)冗余校驗(yàn)(CRC)計(jì)算的新算法,該算法是一種迭代算法,可以逐步更新校驗(yàn)序列,適用于CRC計(jì)算的各種參數(shù)選擇。這一算法適合硬件實(shí)現(xiàn)。其仿真

2023-02-21 09:45:49 0

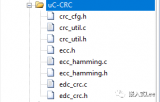

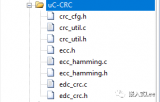

0 我們這一篇來講講Micrium全家桶的uC-CRC。該代碼庫提供了CRC算法進(jìn)行錯(cuò)誤檢測(cè)EDC,使用HAMMING算法實(shí)現(xiàn)ECC錯(cuò)誤糾正。

2023-05-04 10:47:44 509

509

CRC循環(huán)冗余逆向算法顧名思義就是將左邊的數(shù)據(jù)看作低位,右邊的數(shù)據(jù)看作高位。這樣的話需要在g的左邊加m個(gè)0,h也要逆向,例如正向CRC-16算法h=0x4c11db8,逆向CRC-16算法

2023-05-06 14:33:39 397

397 常用的校驗(yàn)方法,用于檢測(cè)和校正數(shù)據(jù)傳輸中的錯(cuò)誤。在FPGA設(shè)計(jì)中,CRC故障指的是與CRC相關(guān)的錯(cuò)誤或問題。 首先,讓我們了解CRC是什么以及它在數(shù)據(jù)傳輸中的作用。CRC是一種基于二進(jìn)制算法的校驗(yàn)

2024-01-04 11:06:15 308

308 FPGA 在比特流被加載時(shí)計(jì)算 CRC 值,然后該值與在比特流加載結(jié)束時(shí)預(yù)期的 CRC 值進(jìn)行比較。如果兩個(gè)值匹配,則FPGA 成功加載。

2024-02-28 14:58:34 99

99

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論