電子發(fā)燒友網(wǎng): 繼 Virtex-7 2000T 之后,賽靈思日前又推出一款 7 系列的高端器件 Virtex-7 H580T,這是全球首款異構(gòu) 3D FPGA,該技術(shù)是在堆疊硅片互聯(lián)(SSI)技術(shù)的基礎(chǔ)上,對(duì) FPGA 和 28Gbps收發(fā)器

2012-07-06 10:42:43 1056

1056

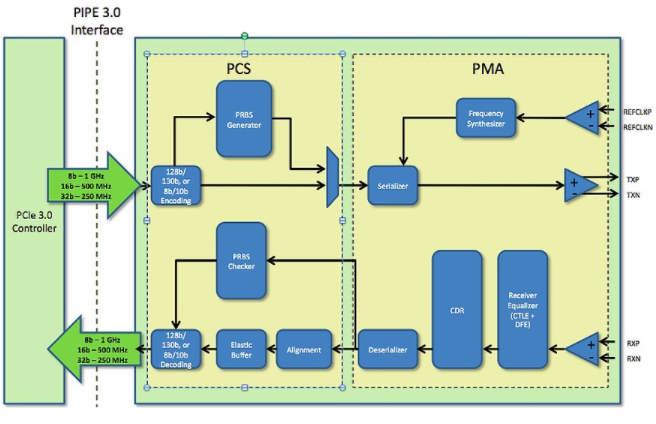

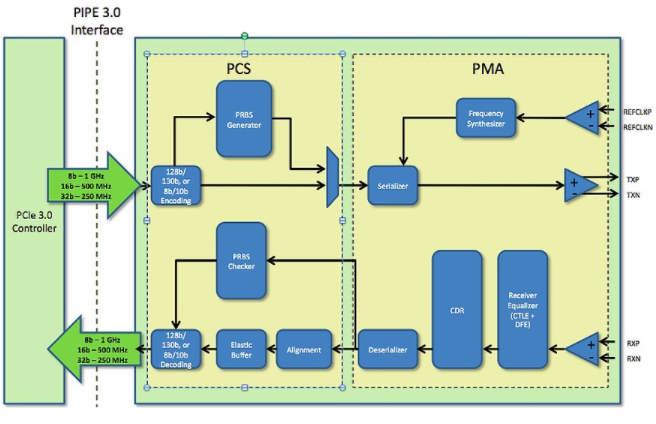

Altera公司 (NASDAQ: ALTR)今天宣布,其28 nm Stratix? V GX FPGA已經(jīng)收錄在最新的PCI-SIG? Integrators名錄中,符合PCI Express? (PCIe?) 3.0規(guī)范(Gen3)要求。

2013-05-23 10:34:54 1803

1803 ,2GB的DDR3。 6、標(biāo)準(zhǔn)JTAG接口。 7、支持BPI模式快速加載。 基于賽靈思的V7 的FPGA開(kāi)發(fā)的PCIe DMA IP支持8.0Gbps(Gen3)at x8,x4,x2和x1的硬核,包括

2016-03-11 10:57:58

賽靈思的最新7系列FPGA芯片包括3個(gè)子系列,Artix-7、 Kintex-7和Virtex-7。在介紹芯片之前,先看看三個(gè)子系列芯片的介紹表,如下表1所示: 表1 全新Xilinx FPGA 7

2012-09-21 13:46:16

VIRTEX-5FPGA - DC and Switching Characteristics - Xilinx, Inc

2022-11-04 17:22:44

我目前正在使用示例設(shè)計(jì)文件模擬virtex-7 690tffg1927-3 GTH。在以_exdes.v結(jié)尾的示例設(shè)計(jì)頂級(jí)文件中,我更改了參數(shù)EXAMPLE_SIM_GTRESET_SPEEDUP

2020-03-06 10:02:12

Layerscape MPU 中是否有支持 PCIe GEN3 16 通道的 EVB?

2023-05-30 08:01:56

(Spartan-6, Virtex-5 FPGA)和Gen 2、5.0Gbps/Lane(Virtex-6/7 Series FPGA)和Gen 3、8.0Gbps/Lane(Virtex-7

2015-06-21 13:38:12

, Virtex-5 FPGA)和Gen 2、5.0Gbps/Lane(Virtex-6/7 Series FPGA)和Gen 3、8.0Gbps/Lane(Virtex-7/UltraScale

2017-06-06 14:46:24

查看我使用我公司擁有的邏輯和協(xié)議分析儀捕獲的PCIe GEN3跟蹤時(shí),沒(méi)有跡象表明TLP摘要中的ECRC值存在問(wèn)題。但是,當(dāng)我在Windows 7筆記本電腦上查看保存的跟蹤/配置.ala文件時(shí),似乎

2018-11-05 10:31:03

描述 這款經(jīng)驗(yàn)證的參考設(shè)計(jì)是一款 PCIe Gen-3 高速前端卡設(shè)計(jì),旨在擴(kuò)展 PCIe 子系統(tǒng)的 PCB 線跡距離。該電路板適合安裝在主板與 PCIe Gen3 插卡之間的 x16 通道寬度

2022-09-21 07:43:27

你好。我使用GTH收發(fā)器(gen3,8x,refclk 100 Mhz)生成了用于PCI Express的Virtex-7集成模塊,然后我嘗試模擬

2020-08-07 10:03:37

,從而達(dá)到多路數(shù)據(jù)通道訪問(wèn)的并行需求和QoS要求。

1.1特性?支持Ultrascale+,Ultrascale,7 Series FPGA?支持PCIe Gen4,PCIe Gen3,PCIe

2024-02-21 10:16:30

達(dá)到多路數(shù)據(jù)通道訪問(wèn)的并行需求和QoS要求。1.1特性?支持Ultrascale+,Ultrascale,7 Series FPGA?支持PCIe Gen4,PCIe Gen3,PCIe Gen

2024-03-09 13:56:04

你好,我是與

FPGA有關(guān)的初學(xué)者,但我對(duì)以下內(nèi)容感興趣:Xilinx

Virtex-7 FPGA VC707評(píng)估套件我注意到PCIe插座是x8,但我的PC主板只有x16??jī)蓚€(gè)插座兼容嗎?問(wèn)候,魯?shù)婪?/div>

2020-03-17 10:00:32

你好,我想獲得Eval板“Xilinx Virtex-7 FPGA VC707評(píng)估套件”,但我有一些問(wèn)題: - 我們是否必須通過(guò)LCD附近的接口將該板連接到PC,以便它能否工作?如果我們不這樣做

2019-09-05 13:09:14

Achieving High Performance DDR3 Data Rates in Virtex-7 and Kintex-7 FPGAs。Xilinx官方DDR3資料。

2016-05-27 16:39:58

嗨,我想在我的PCIe Gen3插槽上使用VC709,但它不起作用。首先,我的電腦規(guī)格:英特爾i7-4770(Haswell)華碩Z87 Pro-V三星DDR3 4GB x 4VC709連接套件

2019-09-09 10:40:29

提供 Virtex-4、Virtex-5、Virtex-6 、Virtex-7、 Kintex-7ZYNQ-7000系列等.. ALTERA優(yōu)勢(shì)產(chǎn)品系列:Stratix、 Arria、 Cyclone、 MAX、 Agilex系列等二手FPGA 貨真價(jià)實(shí)

2019-07-28 17:47:39

(Virtex-6/7 Series FPGA)和Gen 3、8.0Gbps/Lane(Virtex-7/Kintex UltraScale FPGA)2. 自適應(yīng)鏈路寬度,支持PCI Express x8

2015-11-11 15:06:39

描述這款經(jīng)驗(yàn)證的參考設(shè)計(jì)是一款 PCIe Gen-3 高速前端卡設(shè)計(jì),旨在擴(kuò)展 PCIe 子系統(tǒng)的 PCB 線跡距離。該電路板適合安裝在主板與 PCIe Gen3 插卡之間的 x16 通道寬度

2018-08-14 07:00:49

CFP2光纖以太網(wǎng)收發(fā)器模塊相連接,板級(jí)的Virtex-7 H580T 3D FPGA用于接收以太網(wǎng)數(shù)據(jù)流,該FPGA通過(guò)4個(gè)工作在25Gbps的GTZ 28.05Gbps SerDes來(lái)跟兩個(gè)

2017-02-10 17:19:24

我們?nèi)绾问褂?b class="flag-6" style="color: red">Virtex-4 FPGA的Block-RAM來(lái)存儲(chǔ)矩陣/ Vector的內(nèi)容。例如,如何在BRAM中存儲(chǔ)矢量A = [1 2 4 5 6 7 9 3]?OR矩陣B = 1 2 3 45 6 7 8 9 1 4 5

2020-05-27 06:43:47

我們?nèi)绾问褂?b class="flag-6" style="color: red">Virtex-4 FPGA的Block-RAM來(lái)存儲(chǔ)矩陣/ Vector的內(nèi)容。例如,如何在BRAM中存儲(chǔ)矢量A = [1 2 4 5 6 7 9 3]?OR矩陣B = 1 2 3 45 6 7 8 9 1 4 5

2020-05-29 09:16:36

我們?nèi)绾问褂?b class="flag-6" style="color: red">Virtex-4 FPGA的Block-RAM來(lái)存儲(chǔ)矩陣/ Vector的內(nèi)容。例如,如何在BRAM中存儲(chǔ)矢量A = [1 2 4 5 6 7 9 3]?OR矩陣B = [1 2 3 45 6 7 8 9 1 4 5 232 1]

2020-05-29 14:41:56

嗨,如何在Virtex-7 FPGA中實(shí)現(xiàn)動(dòng)態(tài)部分配置?問(wèn)候,Suresh Palani

2020-05-29 11:30:45

需要更多引腳,所以如果我們選擇Virtex-7那么我將會(huì)放松永遠(yuǎn)。當(dāng)我想在fpga本身生成數(shù)據(jù)而不是從PC將其傳輸?shù)?b class="flag-6" style="color: red">fpga時(shí),我陷入了困境,因?yàn)槟壳拔艺谑褂肗DIS驅(qū)動(dòng)程序執(zhí)行此操作,沒(méi)有人知道Windows何時(shí)會(huì)停止支持這一點(diǎn)。如果您能幫助我們對(duì)這兩種設(shè)備進(jìn)行比較,我將不勝感激。溫暖的問(wèn)候

2020-07-20 07:07:12

我試圖在virtex 7而不是kintex 7上使用PRC的實(shí)驗(yàn)3(UG947),在更改.xdc文件以與VC709兼容后,我成功生成了比特流文件和prom.mcs(PIN I /使用(UG947

2020-08-07 08:15:27

Virtex-7 PCI Express Gen3集成塊遷移到我的Kintex板并使其工作?我是否必須進(jìn)行任何具體更改?先謝謝你!

2020-07-16 10:12:19

在我們的應(yīng)用程序中,我們讓多個(gè)Virtex-7設(shè)備通過(guò)SRIO相互通信。在UG476中,建議使用100nF交流耦合電容。在頁(yè)307上,它指出:“發(fā)射器應(yīng)交流耦合到接收器。交流耦合電容的推薦值為100

2020-07-28 10:43:01

對(duì)于VC707評(píng)估套件或VC709連接套件的Virtex-7“參考設(shè)計(jì)”中包含的內(nèi)容,我感到很遺憾。具體來(lái)說(shuō),我想設(shè)計(jì)一個(gè)新的Virtex-7板。我習(xí)慣于其他大芯片的“參考設(shè)計(jì)”,其中參考設(shè)計(jì)包括我

2020-08-13 09:08:44

我需要一些幫助來(lái)評(píng)估Virtex-7演示板的性能。我有ML501板。我記得10%被用于系統(tǒng)架構(gòu)和設(shè)備,如Microbleze,ports,.......我使用其他90%來(lái)執(zhí)行特定的處理單元 - 30

2020-07-16 12:44:21

嗨,我正在通過(guò)JTAG為Virtex-7開(kāi)發(fā)系統(tǒng)內(nèi)配置。我已經(jīng)閱讀了7系列FPGAs配置用戶指南,但沒(méi)有關(guān)于JTAG指令以及單/多設(shè)備配置順序的詳細(xì)信息。在哪里可以找到Virtex-7的單/多設(shè)備配置順序信息?

2020-05-29 12:35:45

你好我有一個(gè)在MIcroBlaze上運(yùn)行l(wèi)inux的設(shè)計(jì)要求。我能夠在我的Virtex-7 FPGA上下載比特流(在Vivado 2014.4中生成)。我使用Impact來(lái)編程我的FPGA。我因此

2020-04-02 10:05:40

嗨,我有一個(gè)virtex-7系列板,我還沒(méi)有在互聯(lián)網(wǎng)上找到引腳說(shuō)明文檔。我怎樣才能為virtex 7分配引腳描述?

2020-07-26 19:37:58

你好,我正在開(kāi)發(fā)一個(gè)在VC709開(kāi)發(fā)板上使用Virtex7 FPGA的系統(tǒng)。該應(yīng)用程序使用32Mb的板載Block RAM作為設(shè)計(jì)中的存儲(chǔ)元件。 FPGA配置序列完成后,有沒(méi)有一種方法可以使用PC上的JTAG / USB接口直接寫(xiě)入和讀取Block RAM的內(nèi)容?謝謝,

2019-09-29 14:00:01

`描述這款經(jīng)驗(yàn)證的參考設(shè)計(jì)是一款 PCIe Gen-3 高速前端卡設(shè)計(jì),旨在擴(kuò)展 PCIe 子系統(tǒng)的 PCB 線跡距離。該電路板適合安裝在主板與 PCIe Gen3 插卡之間的 x16 通道寬度

2015-05-08 11:31:58

SI52147-EVB,用于PoE無(wú)線接入點(diǎn)的時(shí)鐘發(fā)生器評(píng)估板。 Si52147是一款符合PCIe Gen1,Gen2和Gen3標(biāo)準(zhǔn)的9端口PCIe時(shí)鐘發(fā)生器

2020-08-27 14:27:11

嗨,我想檢查7系列設(shè)備XC7K325T-2FFG900是否支持PCIE PHY GEN3?謝謝,

2020-07-25 08:11:39

我正在使用zynq芯片和VIRTEX-7設(shè)計(jì)電路板。我想知道在Zynq PL引腳和Virtex-7 IO引腳之間選擇配置數(shù)據(jù)線(例如Slave SelectMAP X8,X16,X32)的方法。在

2020-06-05 10:31:19

適用于Xilinx Virtex-7 FPGA開(kāi)發(fā)板的32位DDR4 SDRAM

2020-12-30 07:39:14

概述EasyGo FPGA Coder Block是嵌入Matlab/Simulink里面的FPGA 仿真工具包軟件。提供了一些基礎(chǔ)的函數(shù)庫(kù)以及常用的控制函數(shù)模塊,配合

2022-05-19 09:16:05

賽靈思多平臺(tái)Virtex-4 FPGA的性能及應(yīng)用

賽靈思(Xilinx)的Virtex-4現(xiàn)場(chǎng)可編程門陣列(FPGA)是首款基于ASMBL(Advanced Silicon Modular Block)架構(gòu)的多平臺(tái)FPGA系列。通過(guò)采用不同的平臺(tái)(LX、FX

2009-06-26 08:11:39 41

41 引言

本文探討在Virtex-5 FPGA中實(shí)現(xiàn)設(shè)計(jì)的一些難題,然后用一個(gè)項(xiàng)目作為示范來(lái)詳解充分利用其功能集的

2010-11-12 09:44:40 827

827

賽靈思已向客戶推出世界最大容量FPGA:Virtex-7 2000T。這款包含68億個(gè)晶體管的FPGA具有1954560個(gè)邏輯單元,容量相當(dāng)于市場(chǎng)同類最大28nm FPGA的兩倍

2011-10-26 14:31:29 1491

1491 Virtex-7 2000T FPGA的容量是市場(chǎng)同類最大28nm器件的2倍,而且比賽靈思最大型Virtex-6 FPGA大2.5倍。雖然2000T由4個(gè)切片組成,但它仍然保持著傳統(tǒng)FPGA的使用模式,設(shè)計(jì)人員可通過(guò)賽靈思工具流程

2011-10-26 09:11:30 2795

2795 Altera公司(Nasdaq: ALTR)宣布,成功實(shí)現(xiàn)28-nm Stratix? V GX FPGA與PLX?技術(shù)公司(Nasdaq: PLXT) ExpressLane? PCI Express? (PCIe?) Gen3的互操作

2011-12-14 09:28:09 677

677 賽靈思宣布Virtex-7 H580T開(kāi)始發(fā)貨常見(jiàn)問(wèn)題解答,Virtex-7 HT采用賽靈思的堆疊硅片互聯(lián) (SSI)技術(shù),是提供業(yè)界帶寬最高的 FPGA

2012-05-31 17:59:14 1871

1871

UltraScale系列芯片包含PCIe的Gen3 Integrated Block IP核在內(nèi)的多種不同功能的IP核都會(huì)有一頁(yè)設(shè)置為PCIe:BARs,設(shè)置IP核的Base address register 的相關(guān)參數(shù)。

2018-07-04 02:02:00 20828

20828

自己的單獨(dú)的 TAG。在XILINX的Virtex-7 FPGA Gen3 Integrated Block中,TAG管理相對(duì)于原來(lái)的Integrated Block for PCI Express v2.0 有一些新的特點(diǎn),在使用時(shí)必須加以注意。

2017-11-18 13:16:19 1487

1487

賽靈思近日推出內(nèi)置28Gbps收發(fā)器的Virtex-7 HT系列支持下一代100-400Gbps通信系統(tǒng)應(yīng)用適用于行業(yè)最高帶寬線路卡的全新FPGA, 可以提供多達(dá)16個(gè)28Gbps串行收發(fā)器,可支持主要的高速串行、光學(xué)和背板協(xié)議,這里以QA形式對(duì)這一新品進(jìn)行了深度解讀。

2017-11-24 20:42:02 2426

2426 Virtex-7 485T I/O處理能力

2018-06-05 13:45:00 2618

2618 Virtex-7 485T DSP處理能力

2018-06-05 02:45:00 3246

3246 Virtex-7 485T功耗演示

2018-06-05 02:45:00 3159

3159 賽靈思Virtex-7 2000T 演示

2018-06-05 01:45:00 2632

2632 Virtex-7 GTH 收發(fā)器與Altera Stratix V GX 收發(fā)器的功能對(duì)比情況

2018-06-06 01:45:00 3572

3572

Xilinx公司全球最大容量芯片Virtex-7 2000T 性能演示。

2018-06-04 13:47:00 5120

5120 Virtex-7 FPGA系列旨在滿足寬帶通信、高階無(wú)線基礎(chǔ)設(shè)施、高端數(shù)字廣播、雷達(dá)圖像處理及其它航空航天和軍用產(chǎn)品等關(guān)鍵細(xì)分市場(chǎng)應(yīng)用需求。Virtex-7為這些應(yīng)用提供了高容量、高吞吐量、低時(shí)延、低功耗、可擴(kuò)展等優(yōu)異特性。

2018-06-04 01:47:00 5349

5349

Xilinx公司介紹Virtex-7 X690T GTH Demo。

2018-05-22 13:47:47 8473

8473 賽靈思Virtex-7 GTX收發(fā)器演示

2018-05-24 13:49:00 4199

4199 在Virtex-7 x690T FPGA中首次公開(kāi)演示集成PCI Express x8 Gen3端點(diǎn)功能

2018-11-21 06:06:00 3213

3213 ICHEC討論了FPGA對(duì)HPC應(yīng)用的適用性,并重點(diǎn)介紹了能夠利用特定FPGA上所有DSP的器件的最佳數(shù)據(jù)模式。

利用Xilinx Virtex-7 FPGA和Kintex KU115,ICHEC充分利用了re

2018-11-20 06:42:00 2425

2425 Virtex-7 H580T FPGA與CFP2光模塊連接

2018-11-20 06:05:00 3379

3379 演示運(yùn)行x8 Gen3 PCI Express Link的Xilinx Kintex-7 FPGA KC705板。

2019-01-04 11:30:00 3877

3877 查看UltraScale FPGA中集成的PCIe Gen3模塊的性能演示。

第一個(gè)演示顯示了PCIe鏈路上的最大數(shù)據(jù)吞吐量;

demo#2利用現(xiàn)成的DMA引擎和軟件驅(qū)動(dòng)程序來(lái)代表典型的用例。

2018-11-28 06:22:00 3464

3464 Virtex-7 GTH收發(fā)器與Altera Stratix-V GX器件Battle Kits Demo

2018-11-30 06:31:00 2787

2787 觀看Xilinx 28nm FPGA系列中第二款器件的演示 - 高性能Virtex-7 XV485T。

2018-11-30 06:26:00 3271

3271 Virtex?-6 FPGA內(nèi)置支持PCIExpress?Gen2兼容接口。

本視頻介紹了在ML605評(píng)估套件上運(yùn)行的用于PCI Express技術(shù)的Virtex-6 FPGA集成模塊的三個(gè)演示。

2018-11-22 06:30:00 2820

2820 通過(guò)Virtex-7 2000T FPGA中的GTX收發(fā)器實(shí)現(xiàn)高速串行性能。

2018-11-22 06:27:00 3461

3461 Virtex-7 H580T是全球首款全可編程異構(gòu)3D FPGA,具有最高速度的低抖動(dòng)28Gbps收發(fā)器。

2018-11-22 05:55:00 3475

3475 用于virtex?-7 FPGA GTX收發(fā)器的Chipscope?Pro ibert核心是可定制的,設(shè)計(jì)用于評(píng)估和監(jiān)控virtex-7 FPGA GTX收發(fā)器。該核心包括在FPGA邏輯中實(shí)現(xiàn)的模式

2019-02-25 16:43:08 15

15 大程度地實(shí)現(xiàn)差異化。 Virtex-7 FPGA擁有多達(dá)96個(gè)高級(jí)串行收發(fā)器,使設(shè)計(jì)人員能夠?qū)⑼黄菩缘膸挊?gòu)建到下一代通信解決方案中。Virtex-7 FPGA可提供多達(dá)200萬(wàn)個(gè)邏輯單元和超過(guò)5TMACS DSP的吞吐量。這些資源支持大規(guī)模并行數(shù)據(jù)處理體系結(jié)構(gòu),這些體系結(jié)構(gòu)在每個(gè)時(shí)鐘周

2020-06-05 13:55:40 1522

1522 借助128b/130b 編碼方案和加擾多項(xiàng)式,PCIe Gen3 提出了許多傳輸和接收問(wèn)題,所有這些問(wèn)題都在最新規(guī)范中得到解決。

2022-06-14 15:27:59 1592

1592

ON Semiconductor Gen3 掃描 LiDAR 演示器的性能測(cè)量和模型驗(yàn)證

2022-11-15 20:12:52 0

0 completion 直接翻譯過(guò)來(lái)是完成,所以我更愿意稱 rt_completion 為 完成量。

2023-06-07 11:48:21 1110

1110 電子發(fā)燒友網(wǎng)站提供《UltraScale+ FPGA Gen3集成模塊.pdf》資料免費(fèi)下載

2023-09-15 14:26:00 0

0 高通驍龍8 Gen3基于臺(tái)積電N4P工藝制程打造,CPU部分包含1顆Cortex X4超大核、5顆Cortex A720大核和2顆Cortex A520小核,CPU主頻最高為3.19GHz,集成了Adreno 750 GPU。

2023-10-15 11:03:15 1164

1164 高通驍龍8 Gen3旗艦芯片已經(jīng)確定將搭載在多款手機(jī)上,其中包括小米14系列、一加12系列、真我GT5 Pro、魅族21系列、紅魔9系列、榮耀Magic6系列、OPPO Find X7系列等。

2023-10-24 16:53:10 952

952 隨著驍龍8 Gen3在小米14系列的首秀開(kāi)始,11月注定會(huì)是驍龍8 Gen3終端刷屏的月份,各廠商紛紛交出自己對(duì)驍龍8 Gen3的閱讀理解,仿佛誰(shuí)不是首批搭載,誰(shuí)就要成為那個(gè)被“美式霸凌”的顯眼包。

2023-12-06 09:41:52 307

307

據(jù)悉,本次發(fā)布會(huì)的亮點(diǎn)之一是全新的旗艦級(jí)芯片——驍龍8s Gen3。此芯片將作為驍龍8 Gen3之后的次高端產(chǎn)品面世,而搭載它的首款設(shè)備可能就是小米Civi 4手機(jī)。

2024-03-13 09:59:09 113

113

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論