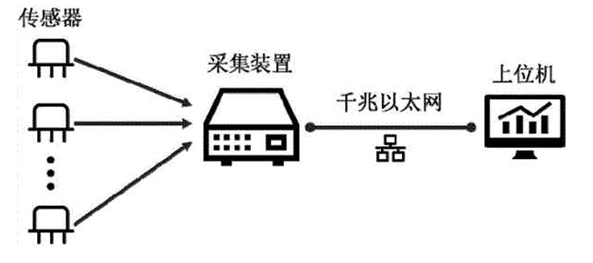

隨著通信技術的發展,千兆以太網因在傳輸中具備高帶寬和高速率的特點,成為高速傳輸設備的首選。基于Xilinx FPGA的嵌入式系統設計整合了一系列的知識產權(IP)核使其功能強大,從而使得利用FPGA進行嵌入式串行千兆以太網開發成為可能。

本設計使用Xilinx公司65 nm工藝級別的Virtex5 FXT系列芯片,滿足嵌入式系統設計所應具備的高性能、高密度、低功耗和低成本的要求。V5 Hard TEMAC模塊提供了專用的以太網功能,并通過FPGA內部高速串行收發器GTX和Marvell公司的88E1111物理層接口芯片相連,完成串行千兆以太網的接口功能。物理層接口芯片支持MII、GMII、RGMII 和SGMII四種以太網接口模式。相對GMII接口而言,SGMII接口的I/O端口數目少,便于PCB布線,并且數據信號以差分對的形式出現,有利于保證信號完整性[1]。

本文將FPGA內嵌PowerPC硬核處理器、Xilinx精簡嵌入式操作系統Xilkernel,以及相應的外設IP Core相結合,完成嵌入式串行千兆以太網的設計。

1 總體設計

系統硬件平臺中選用Xilinx公司的Virtex5 FX70t作為主控芯片,它集成了PowerPC440處理器模塊和高速RocketIO GTX收發器。

外部存儲器采用Micron公司的128M×16位DDR SDRAM芯片MT47H128M16HG 31T,為程序運行提供空間。

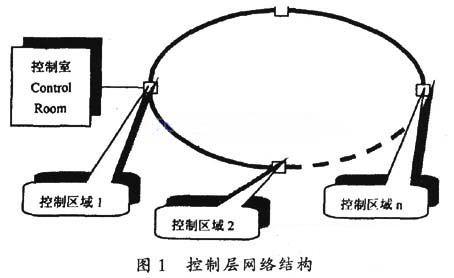

在網絡芯片方面有兩種方案可供選擇,即單物理層芯片方案和物理層加MAC層集成于同一芯片方案[2]。基于易于控制方面的考慮,采用Marvell公司的88E1111單物理層接口芯片作為解決方案,該芯片支持10BASET、100BASETX和1000BASET以太網協議。本系統硬件由Virtex5 FX70t芯片、88E1111 PHY芯片、DDRII芯片、8個撥碼開關(8DIPS)、8個LED燈和RJ45接口構成,其連接框圖如圖1所示。

?

圖1 系統硬件連接框圖

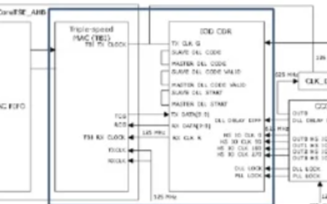

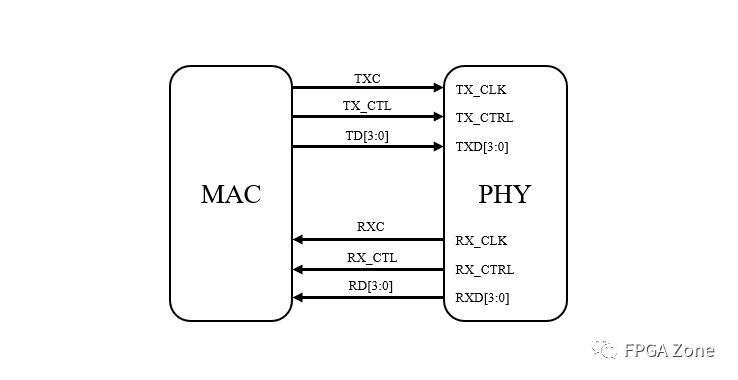

串行千兆以太網設計中,需使用FPGA內部RocketIO GTX收發器完成SGMII鏈路的建立。RocketIO GTX是集成在Virtex5 FX70t芯片中靈活的、功能可配置的千兆位級串行收發器,支持750 Mbps~6.5 Gbps的數據傳輸速率,滿足千兆以太網系統設計中數據傳輸速率的要求。本設計通過在FPGA中例化EMAC硬核,并將相應的FPGA端口和外部PHY芯片88E1111相連完成SGMII鏈路的建立。SGMII接口使用全雙工模式,有收發兩個獨立的通道,每個通道使用一對差分信號線,采用無時鐘信號模式,RocketIO GTX收發器從串行數據中恢復時鐘用于差分數據的發送與接收。

SGMII接口實現框圖如圖2所示。

圖2 SGMII接口實現框圖

本系統基于Xilinx公司嵌入式系統開發工具EDK12.3完成軟硬件協同設計。EDK12.3由XPS (Xilinx Platform Studio)、SDK(Software Development Kit)等組成。設計時需在XPS環境下添加所需的IP核,生成硬件系統框架,并添加相應的引腳約束和時序約束,然后調用Platgen生成嵌入式系統硬件部分的網表(.NGC)文件和比特(.bit)文件,并通過軟件描述文件(.MSS文件)來設置系統軟件配置;接著將硬件設計導入到SDK中,并在SDK中生成各個外設的驅動層和庫,設置相應軟件的操作系統、庫、外設驅動的屬性,添加應用軟件項目并編寫應用軟件;最后,調用處理器對應的編譯器編譯軟件并和硬件可執行文件合成后,生成最終的二進制比特文件,下載到目標板進行系統調試[3]。

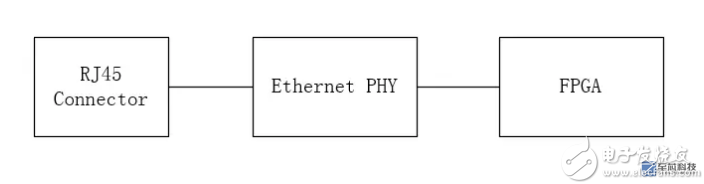

2 PowerPC的硬件設計

設計中采用的FPGA內嵌硬核處理器PowerPC440屬于32位精簡指令集嵌入式處理器,它采用擴展型BookE結構,其內部包括一個高性能、可雙指令處理并有七級流水線的微內核。同時,具有靈活的存儲器管理單元(MMU)、3個相互獨立的128位PLB總線接口、4個直接存儲器存儲(DMA)控制單元,以及設備控制寄存器(DCR) 等[4]。它集成了32 KB指令和32 KB數據緩存,在550 MHz時鐘頻率下可提供高達1 100 DMIPS的性能。在本設計中,PowerPC440通過PLB總線與外設端口相連,其硬件架構如圖3所示。

?

圖3 嵌入式系統硬件架構

系統硬件平臺的搭建(包括PowerPC處理器功能配置、系統總線結構以及相應的地址映射)均在EDK集成開發環境XPS中完成。

設計中采用片內高速數據總線PLB連接各種控制IP核,PowerPC440通過PLB總線完成對內部IP核以及外設的訪問和控制功能。其中,外部PHY芯片通過與在FPGA內部例化EMAC核(Ethernet MAC)相連,掛載在PLB總線上,完成SGMII鏈路的建立;DDR II芯片通過IP核多端口存儲控制器(Multiport Memory Controller,MPMC)掛載在PLB總線上,實現外部存儲功能;串口通過串口控制器IP核(Xps_uartlite)與PLB總線相連,用于打印輸出調試狀態信息;8個撥碼開關DIP和LED燈分別通過GPIO口與PLB總線相連,實現簡單的控制與狀態顯示功能。

硬件結構如圖4所示。

圖4 PowerPC硬件結構圖

本系統使用時鐘生成器IP核生成系統各模塊工作時所需時鐘。該IP核模塊的輸入時鐘為FPGA全局時鐘引腳輸入的100 MHz時鐘,經過相應的倍頻,生成400 MHz的PowerPC440工作時鐘,生成200 MHz的DDR II工作時鐘以及125 MHz的Ethernet MAC工作時鐘。

在各模塊添加及連接結束后,需添加UCF約束文件,包括FPGA引腳約束和相應的時序約束等,并對XPS自動生成的微處理器硬件規范MHS文件進行相應的修改,對系統進行適當的優化。生成的系統在綜合、布局、布線無誤后生成最終的.bit文件,準備下載到電路板上。

3 嵌入式系統軟件設計

本系統軟件部分需實現TCP/IP網絡協議,TCP/IP協議模型包括應用層、傳輸層、網絡層和網絡接口層[5]。網絡接口層分為PHY層和MAC層兩部分。其中,PHY層由外部PHY芯片88E1111實現,MAC層由Xilinx公司的Hard Ethernet MAC IP核實現,并作為整個PowerPC系統硬件的一部分在FPGA的內部實現。

網絡層和傳輸層主要采用LwIP協議模塊編寫相應的軟件代碼。LwIP同時支持服務器模式和客戶端模式,提供RAW和Socket兩種API。它的特點是在保持TCP/IP協議主要功能的情況下,減少對RAW的使用,使得LwIP在各類高檔嵌入式系統開發中得到廣泛的應用。本設計選擇Xilinx公司的精簡嵌入式操作系統Xilkernel,用于更好地管理系統資源。

Xilkernel能與EDK形成的硬件系統緊密結合,是一種可定制的簡單高效系統。Xilkernel系統的配置可以在開發環境SDK中進行手動設置。本設計中運用LwIP協議模塊編寫運行在Xilkernel操作系統上的應用軟件,實現了Web Server(網頁服務)、FTP(File Transfer Protocl)、Telnet遠程登錄服務、iperf應用等功能。下面以網頁服務程序、iperf服務器和客戶端程序為例對軟件設計流程進行說明。

具體流程描述如下:

① 在Xilkernel系統的靜態啟動線程main_thread()中,初始化網絡協議和文件系統。

② 調用線程生成函數sys_thread_new()生成并啟動線程1。

③ 在線程1中設置電路板硬件的MAC地址、網關、IP地址和子網掩碼等參數,并初始化網絡接口。具體設置方式如下:MAC地址為00:0a:35:00:01:02;IP4地址為192.168.1.10;IP4地址掩碼為255.255.255.0;IP4地址網關為192.168.1.1。

④ 初始化一個Socket,將它與IP地址和端口號綁定,然后開始監聽網絡,一旦監聽到網絡請求,再由函數sys_thread_new()生成一個線程2去響應,用于緩存接收到的數據包。然后,通過函數launch_app_threads()判斷監聽到的網絡請求屬于哪種類型,并由函數sys_thread_new()生成相應的線程3去處理。

如果是網絡服務請求,則將網頁文件輸出到PC機上,并接收PC機傳輸的控制數據信息,其程序流程如圖5所示。如果是iperf應用請求,則發送或接收相應的數據完成對請求的響應。

?

圖5 網頁服務程序流程

網頁服務程序運行前需在FPGA外部的DDR中建立文件系統,將用于控制的相關網頁文件保存在該文件系統中。系統在運行時,訪問預設的IP地址,會將相關網頁文件傳輸到遠端控制電腦上,并通過網頁中的超鏈接命令腳本將預設的控制信息傳送給PowerPC處理器,用以控制電路板上的LED燈亮滅,或者讀取電路板上撥碼開關的狀態值并在服務器首頁上顯示。

本設計中采用iperf網絡測試軟件對其性能進行測試。采用9 000字節巨幀可以實現高達490 Mbps的傳輸速率。

結語

本文成功使用Virtex5 FX70t芯片實現串行千兆以太網系統,并通過網頁服務程序對其功能加以驗證。本系統在硬件電路設計階段具有I/O端口數目少、便于PCB布線,以及信號完整性容易保證等優點。通過iperf網絡測試軟件對其傳輸速率進行測試,其結果達到高速數據傳輸的要求。

參考文獻

[1] Xilinx.Virtex5 FPGA Embedded TriMode Ethernet MAC User Guide. [EB/OL].[20120711]. ~cs150/sp10/Project/Checkpoint2/ ug194.pdf.

[2] 高一沅,黃春暉.基于MicroBlaze的以太網通信系統平臺設計的研究[J].現代電子技術,2007(17):2931.

[3] 王長清,陳棟.基于FPGA的千兆以太網通信板的設計與實現[J].河南師范大學學報:自然科學版,2011,39(1):8689.

[4] 宋曉翠,張晉寧.基于PowerPC440的嵌入式系統設計與研究[J].新特器件應用,2009,11(7):1921.

[5] 徐欣,于紅旗,易凡,等. 基于FPGA的嵌入式系統設計[M].北京:機械工業出版社,2005.

電子發燒友App

電子發燒友App

評論