頻譜分析儀主要用于信號成分分析,其應用領域相當廣泛,在電磁干擾偵測分析、無線電通信、衛星接收系統等方面均有涉及。就具體信號分析手段而言,傳統時域波形分析的確能夠直觀觀察信號的幅度、頻率、波形等響應變化,但局限于低頻信號,高速信號下時域分析有著必然的缺憾。頻譜分析是指將信號的頻率、幅值等信息在頻域中表示的一種分析方法,它對于任意信號進行傅里葉變換,進而將其分解為若干單一的諧波分量來研究,以獲得信號的頻率結構以及各諧波幅值和相位信息,這對于高頻信號以及復雜信號分析意義十分重大。可以看出,頻譜分析儀的重點是幅頻特性與相頻特性,尤其是幅頻特性的計算。

1、核心原理論證

對于頻譜分析儀,就具體的實現原理而言,主要存在三種思路:多通道并行濾波式、掃頻外差分析式以及直接FFT式。

1.1、多通道并行濾波式

多通道并行濾波式方案的核心在于多個濾波器的制作,其思路主要是將全頻段等分為若干個通帶不重疊(或部分重疊)的帶通濾波器,這些濾波器的過渡帶帶寬、甚至通帶最大允許衰減等參數都幾乎一致,僅僅是通帶頻率范圍不一致。當信號并行送入每個濾波器之后,對于各個濾波輸出進行能量檢測,從而進一步確定各個頻段的信號幅度,繪制出頻譜圖。顯然,只有諧波分量對應頻段的濾波器,輸出信號可以采集到能量值,且能量值隨諧波分量增大而增大。這種傳統模擬頻譜儀的缺點在于過于依賴模擬電路的搭建,硬件要求很高,容易產造成頻率分辨率精度不足,甚至是測量誤差。

1.2、掃頻外差分析式

掃頻外差分析式的核心在于混頻模塊的設計,其思路主要是利用一個連續掃頻的本地振蕩器,產生的本振信號與被測信號混頻,這樣被測信號諧波分量總會有機會落入后續中頻濾波器的通帶中。如果令本振信號的幅度保持不變,那么混頻器的輸出、中頻濾波的輸出、檢波模塊的輸出都會與被測信號的對應諧波分量幅度成正比。將掃頻器的控制電壓(一般為線性)與檢波模塊的輸出電壓分別作為X和Y信號,即可得到被測信號的幅頻特性圖。這種方案實際上以掃頻外差功能代替了并行濾波功能,降低了硬件要求,提高了系統性能。

1.3、直接FFT式

直接FFT式方案的核心在于高速FFT(FastFourierTransform)的計算,常規的單片機系統如ARM都無法完成,必須要依靠現場可編程門陣列(FPGA)等適合高速信號處理的開發系統,其思路主要是將信號進行波形調理后送入高速AD采樣芯片,將采集得到的信號截取短時窗進行FFT計算,直接將計算結果輸出為幅頻特性圖與相頻特性圖。顯然,這種方案也有難點存在,那就是對于AD芯片的采樣頻率要求較高,但是如果有合適的AD芯片,那么這種數字型頻譜儀與模擬型頻譜儀相比,容錯率將會更高,頻率檢測范圍、頻率分辨率等技術指標也會大大優化。

2、系統整體方案設計

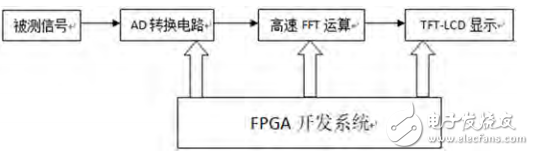

簡易數字式頻譜儀主要由信號采集模塊、高速FFT模塊以及LCD顯示模塊組成。信號采集模塊以AD9226芯片為核心,配合前置抗混疊濾波電路實現信號采集;高速FFT模塊在FPGA開發系統通過編程實現;LCD顯示模塊選擇4.3寸TFT液晶屏,實現可視化界面。簡易數字式頻譜儀的系統框圖如圖1。

圖1

2.1、信號采集模塊

AD9226芯片是ADI公司的12bit量化、65MSPS模數轉換器,采用單電源供電,內置一個片內高性能采樣保持放大器和基準電壓源,采用多級差分流水線架構,AD采樣頻率理論上可以達到65MHz。根據ADI公司提供的芯片數據手冊以及FPGA配套模塊的相關資料,設計信號采集模塊如圖2。

圖2

2.2、高速FFT模塊

高速FFT模塊依托FPGA開發系統進行搭建,以按鍵為工作開始的標志,對信號采集模塊輸出的數據截取長度為512的短時窗,接著利用XILINX公司提供的IP核構建FFT計算單元,對512個采樣數據進行FFT計算,并將FFT計算結果按序依次保存到事先分配的LCD顯示內存中,更新頻譜圖的顯示數據。

(1)FPGA需要實現按鍵檢測,以按鍵作為允許FFT計算單元輸入新采樣數據的標志。

(2)FPGA需要調用快速傅立葉變換(FFT)IP核,將參數定義為短時窗長度512、非流水線式基2蝶形運算、12bit整型輸入、8bit整型輸出、50MHz工作頻率等狀態,設置好何時讀取新數據、何時輸出計算結果的標志位等等。

(3)FPGA需要調用坐標旋轉數字計算機(CORDIC)IP核,對FFT計算所得的實部數據和虛部數據進行模值計算或者相角計算。

(4)FPGA分配出數據存儲區域作為LCD的顯示內存,將前256個模值計算結果或相角計算結果(FFT的運算過程決定了幅頻特性圖前256個數據與后256個數據軸對稱,相頻特性圖前256個數據與后256個數據中心對稱),由顯存送入LCD數據接口。整個設計流程最為重要的是時序,每個模塊的工作時序以及標志位必須互相關聯,且由于各種計算單元是單接口串行輸出,因此尤其要注意高速信號傳輸時由于時序設計不當而產生的“競爭冒險”現象,因此一個鎖相環IP核也必不可少。

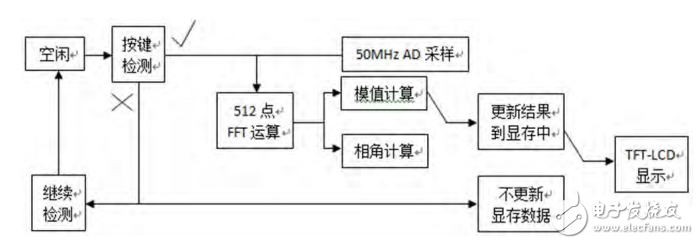

整個FPGA高速FFT模塊的工作框圖如圖3。

圖3

2.3、LCD可視化界面模塊

對于4.3寸TFT液晶顯示屏,像素為480*272,顏色規格為24bitRGB。由于FPGA開發系統不像ARM開發系統有許多現成的庫函數可以調用,因此在編程驅動LCD時需要自行設定掃描刷新頻率、橫向與縱向掃描控制信號等,配合LCD的顯示內存,實現掃描到LCD每個位置時輸出對應的顏色數據即可。由于LCD顯存中的數據變化速率(由按鍵決定)并不快,遠遠慢于正常液晶屏的掃描頻率(60幀/秒),因此LCD顯示出的頻譜圖應當為靜態圖像。此外,在顯示圖像時還要增加坐標軸,將各個諧波的對應頻率與幅度顯示在坐標軸旁,或者增加標度,使得諧波分量的相關信息可讀出。

諧波分量在256個計算結果中的對應下標k(0~255)與實際諧波頻率f的換算公式為:

式(1)中,fs為實際AD采樣頻率50MHz,N為截取短時窗的長度,即FFT計算長度512。

由于AD芯片的采樣電壓范圍為-5~5V,在模數轉換時量化為12bit,因此經過推衍可知諧波分量在256個計算結果中的對應幅度A(0~63)與實際諧波幅度Vpp的換算公式為:

式(2)中,Vpp的單位為V。

整個LCD顯示模塊的工作框圖如圖4。

圖4

3、測量結果

3.1、開發系統編譯環境

FPGA開發系統,編譯環境:XILINXISE14.7,開發板型號:XILINXSPARTAN-6

3.2、測試結果

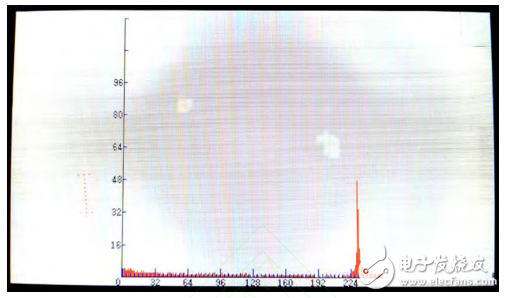

利用信號發生器產生峰峰值10V,頻率11MHz的雙極性正弦信號作為被測信號,送入數字頻譜儀,在TFT-LCD得到幅頻特性圖像如圖5。

圖5

由圖5中可見,正弦信號在頻譜儀上的分析結果中,僅有一個諧波分量。

根據諧波分量在256個計算結果中的對應下標k=113與公式(1)可以得知,頻譜圖中諧波分量對應的頻率為11.03MHz,基本等于實際正弦信號頻率;

根據諧波分量幅度值為A=51與公式(2)可以得知,頻譜圖中諧波分量對應的幅值為9.94V,基本等于實際正弦信號幅度。

利用信號發生器產生峰峰值9V,頻率22.5MHz的雙極性正弦信號作為被測信號,送入數字頻譜儀,在TFT-LCD得到幅頻特性圖像如圖6。

由圖6中可見,正弦信號在頻譜儀上的分析結果中,僅有一個諧波分量。

根據諧波分量在256個計算結果中的對應下標k=230與公式(1)可以得知,頻譜圖中諧波分量對應的頻率為22.47MHz,基本等于實際正弦信號頻率;

根據諧波分量幅度值為A=47與公式(2)可以得知,頻譜圖中諧波分量對應的幅值為9.16V,基本等于實際正弦信號幅度。

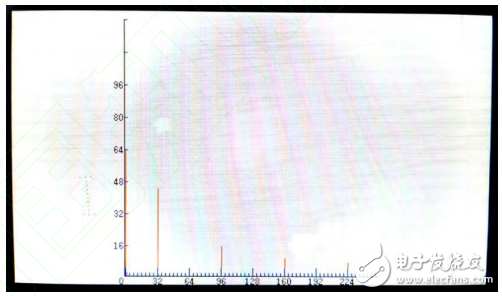

利用信號發生器產生峰峰值5V,頻率3.125MHz單極性方波信號作為被測信號,送入數字頻譜儀,在TFT-LCD得到幅頻特性圖像如圖7。

由圖7中可見,單極性方波信號在頻譜儀上的分析結果中,存在著直流分量(k=0)與多個奇次諧波分量,且分量幅值逐漸降低。

根據各個諧波分量在256個計算結果圖6圖7中的對應下標k=32,96,160,224與公式(1)可以得知,頻譜圖中諧波分量對應的頻率為3.125MHz、9.375MHz、15.625MHz、21.875MHz,完全等于實際方波信號中一、三、五、七次諧波頻率。

4、結語

本文提出了一種基于FPGA開發系統的數字式簡易頻譜分析儀的設計,實現了高頻信號的采集、運算、成分分析與顯示,整個系統分析時間僅為10~15μs,在50MHz采樣頻率情況下頻譜圖的頻率分辨率可達到100kHz以下,可以控制諧波頻率檢測的相對誤差在1%以下。此設計方案還可以進一步研究,尤其是在提高FFT計算精度,以及可視化界面優化方面依然存在著研究空間。

電子發燒友App

電子發燒友App

評論