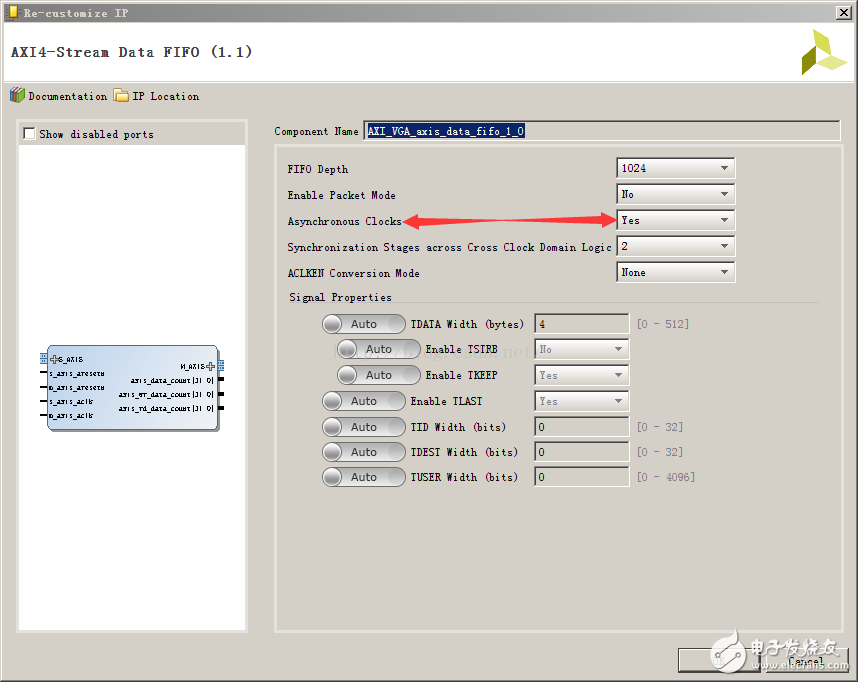

AXI STREAM FIFO如何設置雙時鐘

- 異步時鐘(9361)

相關推薦

Zynq中AXI4-Lite和AXI-Stream功能介紹

等于b0000(非緩沖和非緩存)。 5) 不支持互斥性操作。 Zynq中AXI-Stream功能 AXI-Stream協議作為一個標準接口,用于連接數據交換元

2020-09-27 11:33:02 8051

8051

8051

8051

Xilinx zynq AXI總線全面解讀

,是面向地址映射的接口,允許最大256輪的數據突發傳輸; (B)AXI4-Lite:(For simple, low-throughput memory-mapped communication )是一個輕量級的地址映射單次傳輸接口,占用很少的邏輯單元。 (C)AXI4-Stream:(F

2020-12-04 12:22:44 6179

6179

6179

6179

ZYNQ SOC案例開發:AXI DMA使用解析及環路測試

provides high-speed data movement between system memory and an AXI4-Stream-based target IP such as AXI

2020-12-31 09:52:02 7166

7166

7166

7166

同步FIFO設計詳解及代碼分享

FIFO (先入先出, First In First Out )存儲器,在 FPGA 和數字 IC 設計中非常常用。 根據接入的時鐘信號,可以分為同步 FIFO 和異步 FIFO 。

2023-06-27 10:24:37 1199

1199

1199

1199

AXI VIP當作master時如何使用

AXI VIP當作master時如何使用。 ??新建Vivado工程,并新建block design,命名為:axi_demo 新建axi vip,參數設置如下,第一個參數設置為Master,其他都保持

2023-07-27 09:19:33 633

633

633

633

XILINX FPGA IP之AXI Traffic Generator

AXI Traffic Generator IP 用于在AXI4和AXI4-Stream互連以及其他AXI4系統外設上生成特定序列(流量)。它根據IP的編程和選擇的操作模式生成各種類型的AXI事務。是一個比較好用的AXI4協議測試源或者AXI外設的初始化配置接口。

2023-11-23 16:03:45 580

580

580

580

AXI-stream數據傳輸過程

。AXI4-Stream的核心思想在于流式處理數據。 圖 4?58 AXI-Stream Interface 全局信號 1.ACLK 全局時鐘信號,在上升沿時對信號采樣。所有的輸入信號都通過上升沿采集,所有

2021-01-08 16:52:32

AXI 1G / 2.5G以太網子系統在AXI4-Stream接口中的最大“數據包”大小是多少?

個恒定的6個32位字,所以必須注意幀數據或控制數據的緩沖區填滿的條件。防止無序狀況。“我還說在AXI4-Stream接口中“數據是以數據包的形式傳輸而不是連續流”。最大9Kb“幀”大小是否也適用于通過AXI4-Stream接口發送的最大“數據包大小”?問候。

2020-05-25 09:37:36

AXI FIFO和AXI virtual FIFO這兩個IP的使用方法

軟件中設置非常簡單。我們需要在軟件中執行以下操作:配置 AXI Stream FIFO讀取FIFO的占用情況從 FIFO 中讀出指定的字數在應用軟件中根據需要處理樣品#include <

2022-11-04 11:03:18

AXI VDMA可以工作,但是少數線路不正確,總是丟包

較大的圖像總是會丟失數據包。我認為問題可能是vdma fifo設置。我的項目:結果比較system.mhs 11 KB以上來自于谷歌翻譯以下為原文Hi, allI met a problem

2019-03-01 12:26:32

AXI4S接口視頻協議在視頻IP中的應用總結

在一起。1.2.2 多像素編碼示例AXI4S視頻接口支持每時鐘雙像素或四像素,對于RGB、YUV444和YUV420色彩空間,每個分量有8位、10位、12位和16位。當參數“每個組件的最大位數”設置為

2022-11-14 15:15:13

AXI接口協議詳解

。 AXI4-Stream:(For high-speed streamingdata.)面向高速流數據傳輸;去掉了地址項,允許無限制的數據突發傳輸規模。 Stream的理解,可以想象一下

2022-10-14 15:31:40

AXI接口協議詳解

機數據本次傳輸有效;(8) TUSER信號 :用戶定義信號,寬度為128bit。對于AXI4-Stream總線命名而言,除了總線時鐘和總線復位,其他的信號線都是以T字母開頭,后面跟上一個有意義的單詞

2022-04-08 10:45:31

AXI流FIFO掛起

“base_address + 0x1C”之前我需要采取的任何步驟以上來自于谷歌翻譯以下為原文I am using the AXI stream FIFO to stream data

2019-04-24 12:54:04

axi4-stream combiner問題的解決辦法?

AXI4-Streamslave接口上TDATA信號的寬度(以字節為單位)。 AXI4-Stream主接口TDATA寬度是此值乘以從屬接口數參數。此參數是一個整數,可以在0到(512 /從站接口數)之間變化。設置為0以省略

2020-08-20 14:36:50

axi4-stream互連問題如何解決

你好,大家好。我正在使用EMI14.4和xc6v315t。我正在嘗試模擬IP CORE.It的axi4-stream interconnect.I配置ip為6siand 4mi。但是當我用ismI模擬它時發現s_tready很低,有什么問題?

2020-06-18 15:08:59

FPGA片內FIFO的Xilinx庫設置和功能仿真

、57、58……。●FIFO為空時,指示信號fifo_empty為高電平,一旦寫入數據后的第2個時鐘周期,fifo_empty為低電平,表示當前FIFO不空。●讀使能信號fifo_rden拉高時,第2個

2019-04-08 09:34:40

FPGA問題 PL端獲取的數據和時鐘 如何存入DDR中

RT,求助自己做了一個PL核 獲取時鐘和數據 并輸出 如何把數據傳入DDR中,有現成的IP核還是有相關的教程嗎開發工具 vivado 除了 使用Video In to AXI4-Stream 和 AXI Video Direct Memroy Access 有沒有別的方法麻煩大家了

2022-07-20 09:24:20

Vivado HLS直通AXI Stream IP-Core如何分配

嗨,我已經創建了一個帶有IP-Core的硬件設計。但它不能正常工作。對于我提到的調試問題,我創建了一個IP-Core,然后通過AXI Stream。所以我可以檢查我的IP-Core是否不起作用

2020-04-14 09:25:10

ZYNQ中不同應用的DMA總結

到 PL 高速傳輸高速通道 AXI-HP<---->AXI-Stream 的轉換AXI-FIFO-MM2S:實現從 PS 內存到 PL 通用傳輸通道 AXI-GP<

2022-03-31 11:39:10

vsync和hsync生成以及視頻輸入到axi流兼容性

視頻信號,而我正在傳輸像素,但我不清楚是否必須包括空白同步。如果存在限制或最小值,我需要多少個時鐘才能保持高hsync和vsync ....使用videoIn_to_axi-stream IP核可

2019-04-23 06:00:37

【FPGA開源教程連載】第十五章 嵌入式塊RAM使用之FIFO

。通過設置雙時鐘FIFO的寫入位寬為16位,讀取位寬為8位,則可以實現將16位的ADC數據轉換為以太網支持的8位發送數據,然后通過以太網發送到PC機。4.實現FIFO的方法在AlteraFPGA中使

2017-01-04 16:41:25

為什么我的vout初始化標志總是向上且沒有達到鎖定狀態?

+ DataPattern >> v_vid_in_axi4s >> AXI4-Stream >> v_axi4s_vid_out \\ ====== VTG(計時)==== //`我

2019-07-15 09:47:54

介紹一下不帶數據的Stream—Event

使用SpinalHDL lib中所提供的Event:Event對應一個payload為NoData的Stream信號,而NoData顧名思義,其實現為一個空的Bundle:》Example這里我們以Axi

2022-06-27 16:07:04

使用外部時鐘驅動AXI外設無法運行

嗨,我一直在嘗試使用外部時鐘驅動一些AXI外設,盡管該設計已經過測試,使用相同頻率的內部時鐘(Zynq PLL生成),但在使用外部時鐘時無法運行。分機時鐘通過時鐘使能引腳提供,路由到MMCM,通過

2019-04-09 09:12:26

關于異步fifo的安全問題:

由于,如果異步fifo的雙口ram真的空了,而跨時鐘域延遲造成的rdempty仍然非空,則讀fifo的邏輯,就有可能根據rdempty信號(非空指示),發出將導致錯誤的讀請求rdreq5. 另外,如果

2018-03-05 10:40:33

可以從AXI流端口獲取輸出采樣數據嗎?

大家好我對7系列家族的XADC向導提出了一個小問題。我設計了我的XADC并且它運行成功,但是因為我想在其后放置一個FIFO內存,我想在XADC中啟用AXI4Stream以實現更好的同步。所以我現在

2020-05-20 14:53:11

可以在EDK中使用Axi4Stream接口/總線嗎?

你好,我正在EDK中使用axi4stream。有人可以幫助我如何使用通過Vivado高級綜合(HLS)生成的ap_fifo / axi4stream接口可以在EDK中使用嗎?我正在使用Export

2019-02-28 13:47:30

如何使用AXI配置的ILA調試PCIe AXI接口?

user_clk從端點連接到AXI configuredILA的時鐘端口時,似乎永遠不會出現在硬件管理器中(在調試探針窗口中)。 a)這是否必須對自由運行時鐘要求做些什么? b)我使用了緩沖的系統時鐘(來自

2019-09-25 09:26:14

如何使用Xilinx AXI VIP對自己的設計搭建仿真驗證環境的方法

到。axi-vip和axi-stream-vip都有自帶的仿真例程,常用的功能在仿真例程中都有涉及。2.1設置VIP支持的Outstanding讀寫深度例如,設置slave vip的outstanding深度為

2022-10-09 16:08:45

如何使用虛擬FIFO控制器從XADC獲取單通道數據

我正在嘗試使用DDR3 RAM作為緩沖器,使用虛擬FIFO控制器從XADC獲取單通道數據。我設置VFIFO的突發模式為4096字節,并分配了8192個4K頁面,這應該給我32MB;從技術上講,我

2020-05-20 14:22:46

如何吧AXI4-stream時鐘轉換器tkeep設置為null?

大家好,我正在兩個時鐘域之間穿過AXI4-Stream,并嘗試使用AXI4-Stream時鐘轉換器核心,使用tkeep端口但是在合成時它被Vivado 2015.2在實例化時刪除了!這是綜合警告

2020-05-08 08:56:14

如何將AXI4-Stream與CH7301接口?

我有SP605&amp; ML506 Xilnx開發板。我想從FPGA驅動CH7301芯片。我正在尋找一些帖子或應用筆記,可以幫助我把這兩件事放在一起。我一直在關注核心AXI4-Stream到視頻

2020-03-20 09:04:51

如何計算異步FIFO深度和單獨的時鐘源

時鐘,使得它們來自單獨的板載振蕩器。這導致了fifo溢出。我將深度更新為128,然后再次運行。如果有人可以告訴我發生了什么,以及這個FIFO設置是否可以可靠地處理來自不同來源的時鐘,我真的很感激。我打算

2019-04-09 06:25:58

有人有經驗AXI4-Stream到視頻輸出IP核嗎?

無論我如何嘗試,AIVO(視頻,Vsync,Hsync,DE)的所有輸出在模擬中始終保持為0。我檢查了端口連接,并單獨模擬VTC和TPG,它們都運行良好。有沒有人有經驗的AXI4-Stream到視頻輸出

2019-03-08 10:00:05

構建自定義AXI4-Stream FIR濾波器的步驟

1、?構建自定義AXI4-Stream FIR濾波器 AMD-Xilinx 的 Vivado 開發工具具有很多方便FPGA開發功能,我最喜歡的功能之一是block design的設計流程

2022-11-07 16:07:43

求助verilog編寫實現AXIStream-FIFO功能思路

),要用verilog實現AXI Stream的異步FIFO1、讀寫不同的時鐘,設一個100M,另一個333M2、讀寫不同的位寬,設寫為8bit,讀為32bit3、fifo深度為324、控制信號沒有

2014-02-21 16:24:45

溢出標志是否在Stream模式下不起作用?

FIFO_SRC_REG中的溢出標志。但它在代碼運行期間從未設置過。所以我不應該在閱讀和打印時丟失任何數據。我的問題:1.溢出標志是否在Stream模式下不起作用?即當新數據被覆蓋時,它是否會保持高位

2019-05-23 08:59:20

看看Stream信號里是如何做跨時鐘域握手的

popArea里stream.m2sPipe,這個版本效率相較于前者,略低一些:StreamFifoCC這個就沒有什么好說的了,通過fifo來實現stream信號的跨時鐘域,效率最高,資源相對也會多

2022-07-07 17:25:02

聊聊SpinalHDL中的FIFO

SpinalHDL對于Stream接口抽象的便捷性。而對于日常的邏輯電路設計而言,出現FIFO Overflow,underflow的常見原因就是我們將ren、wen聲明為寄存器信號,而在處理時序上的不當導致

2022-06-30 15:28:00

請問AXI4-Stream到Video核心的技巧有什么?

大家好。我遇到了xilinx視頻內核的問題,并試圖解決這個問題好幾周但都失敗了。有人能給我一些關于AXI4-Stream到Video核心的技巧嗎?我試圖在我的項目中實現Video Scaler核心

2019-11-08 09:53:46

請問AXI-4流接口有沒有可用的地址線?

嗨,我已經通過以太網MAC IP作為“LogiCORE IP 10千兆以太網MAC v13.1”U.G. PG072。由于我對AXI沒有太多了解,因此我幾乎沒有查詢讀取AXI4-Stream接口

2020-04-28 10:00:42

請問可以使用AXI-Stream Broadcaster作為AXI開關嗎?

我們可以使用AXI-Stream Broadcaster作為AXI開關嗎?如果可能,我們需要控制切換哪個信號?我想開發小型應用程序,它涉及廣播AXI流數據并將AXI流數據切換到特定的從站。在這個應用程序中,我們只有一個主站和8個從站。我們想在從站之間切換流數據。提前致謝。

2020-05-07 09:42:16

請問我對AXI4-Stream FIFO的理解不正確嗎?

嗨,我正在研究Spartan 6的設計。數據來自PCIe IP核,頻率為62.5MHz,通過AXI4-Stream FIFO同步到100 MHz系統時鐘。這是一個示例波形;m_axis_tvalid

2019-08-12 07:29:20

談談FIFO閾值的閾值設置及深度計算

`立即學習—60天FPGA工程師入門就業項目實戰特訓營(3月16日開班) 談談FIFO閾值的閾值設置及深度計算1.什么是FIFO2.什么情況下使用FIFO3.什么FIFO的閾值4.FIFO的閾值

2020-02-19 21:09:35

異步FIFO結構

設計一個FIFO是ASIC設計者遇到的最普遍的問題之一。本文著重介紹怎樣設計FIFO——這是一個看似簡單卻很復雜的任務。一開始,要注意,FIFO通常用于時鐘域的過渡,是雙時鐘設計

2009-10-15 08:44:35 94

94

94

94Xilinx的LogiCORE IP Video In to AXI4

Xilinx的視頻的IP CORE 一般都是 以 AXI4-Stream 接口。 先介紹一下, 這個IP的作用。 下面看一下這個IP 的接口: 所以要把標準的VESA信號 轉為

2017-02-08 08:36:19 531

531

531

531

異步FIFO的設計分析及詳細代碼

位寬(每個數據的位寬) FIFO有同步和異步兩種,同步即讀寫時鐘相同,異步即讀寫時鐘不相同 同步FIFO用的少,可以作為數據緩存 異步FIFO可以解決跨時鐘域的問題,在應用時需根據實際情況考慮好fifo深度即可 本次要設計一個異步FIFO,深度為8,位寬也是8。

2017-11-15 12:52:41 7993

7993

7993

7993

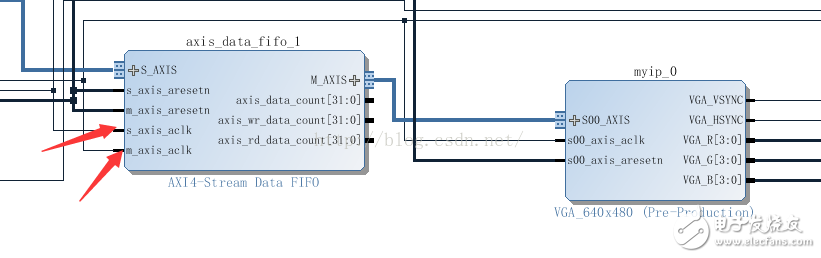

AXI4Stream總線的FPGA視頻系統的開發研究

基于AXI4Stream總線協議,在Xilinx公司提供的FPGA上實現了一個具有缺陷像素校正、色彩濾波陣列插值、圖像降噪實時圖像采集與顯示功能的視頻系統。AXI4Stream總線協議由ARM公司

2017-11-17 08:58:01 4189

4189

4189

4189如何解決異步FIFO跨時鐘域亞穩態問題?

跨時鐘域的問題:前一篇已經提到要通過比較讀寫指針來判斷產生讀空和寫滿信號,但是讀指針是屬于讀時鐘域的,寫指針是屬于寫時鐘域的,而異步FIFO的讀寫時鐘域不同,是異步的,要是將讀時鐘域的讀指針與寫時鐘域的寫指針不做任何處理直接比較肯定是錯誤的,因此我們需要進行同步處理以后進行比較。

2018-09-05 14:29:36 5613

5613

5613

5613HLS Stream案例分析

第二步,不設置任何directive,直接執行C綜合,此時會顯示如下錯誤信息。該信息表明,在非dataflow區域使用默認的FIFO規模(這個FIFO是因為stream而生成的,默認深度

2019-04-24 17:36:14 9564

9564

9564

9564FPGA之FIFO練習3:設計思路

根據FIFO工作的時鐘域,可以將FIFO分為同步FIFO和異步FIFO。同步FIFO是指讀時鐘和寫時鐘為同一個時鐘。在時鐘沿來臨時同時發生讀寫操作。異步FIFO是指讀寫時鐘不一致,讀寫時鐘是互相獨立的。

2019-11-29 07:08:00 1609

1609

1609

1609一文詳解ZYNQ中的DMA與AXI4總線

在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三種總線,但PS與PL之間的接口卻只支持前兩種,AXI-Stream只能在PL中實現,不能直接和PS相連,必須通過AXI

2020-09-24 09:50:30 4289

4289

4289

4289

你必須了解的AXI總線詳解

的轉換 AXI-FIFO-MM2S:實現從 PS 內存到 PL 通用傳輸通道 AXI-GP-----AXI-Stream 的轉換 AXI-Datamover:實現從 PS 內存到 PL 高速傳輸高速

2020-10-09 18:05:57 6391

6391

6391

6391

ZYNQ中DMA與AXI4總線

和接口的構架 在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三種總線,但PS與PL之間的接口卻只支持前兩種,AXI-Stream只能在PL中實現,不能直接和PS相連,必須通過

2020-11-02 11:27:51 3880

3880

3880

3880

AXI-Stream代碼

突發傳輸規模。AXI4-Stream的核心思想在于流式處理數據。 圖 4?58 AXI-Stream Interface 全局信號 1.ACLK 全局時鐘信號,在上升沿時對信號采樣。所有的輸入信號都通過

2020-11-05 17:40:36 2826

2826

2826

2826

如何在Altera FPGA中使用FIFO實現功能設計?

的緩存或者高速異步數據的交互。 二:FIFO有幾種結構 FIFO從大的情況來分,有兩類結構:單時鐘FIFO(SCFIFO)和雙時鐘FIFO(DCFIFO),其中雙時鐘FIFO又可以分為普通雙時鐘

2021-03-12 16:30:48 2796

2796

2796

2796

關于AXI4-Stream協議總結分享

XI4-Stream跟AXI4的區別就是AXI4-Stream去除了地址線,這樣就不涉及讀寫數據的概念了,只有簡單的發送與接收說法,減少了延時。由于AXI4-Stream協議(amba4_axi4_stream_v1_0_protocol_spec.pdf)沒有時序圖,

2022-06-23 10:08:47 1781

1781

1781

1781AXI4-Stream Video 協議和AXI_VDMA的IP核介紹

本文主要介紹關于AXI4-Stream Video 協議和AXI_VDMA的IP核相關內容。為后文完成使用帶有HDMI接口的顯示器構建圖像視頻顯示的測試工程做準備。

2022-07-03 16:11:05 6846

6846

6846

6846AXI4 、 AXI4-Lite 、AXI4-Stream接口

AXI4 是一種高性能memory-mapped總線,AXI4-Lite是一只簡單的、低通量的memory-mapped 總線,而 AXI4-Stream 可以傳輸高速數據流。從字面意思去理解

2022-07-04 09:40:14 5818

5818

5818

5818FIFO的閾值如何設置

FIFO是First in First out 的縮寫,一般是由寄存器reg或者ram搭起來的,相對于普通存儲器而言,FIFO沒有地址可操作的地址總線,因而使用比較方便,但是數據只能像水流一樣排隊進排隊出。

2022-08-19 09:02:47 1830

1830

1830

1830使用AXI4總線實現視頻輸入輸出

Xilinx vivado下通常的視頻流設計,都采用Vid In to axi4 stream --> VDMA write --> MM --> VDMA read -->

2022-10-11 14:26:03 4556

4556

4556

4556同步FIFO之Verilog實現

FIFO的分類根均FIFO工作的時鐘域,可以將FIFO分為同步FIFO和異步FIFO。同步FIFO是指讀時鐘和寫時鐘為同一個時鐘。在時鐘沿來臨時同時發生讀寫操作。異步FIFO是指讀寫時鐘不一致,讀寫時鐘是互相獨立的。

2022-11-01 09:57:08 1315

1315

1315

1315異步FIFO之Verilog代碼實現案例

同步FIFO的意思是說FIFO的讀寫時鐘是同一個時鐘,不同于異步FIFO,異步FIFO的讀寫時鐘是完全異步的。同步FIFO的對外接口包括時鐘,清零,讀請求,寫請求,數據輸入總線,數據輸出總線,空以及滿信號。

2022-11-01 09:58:16 1189

1189

1189

1189AXI FIFO和AXI virtual FIFO兩個IP的使用方法

FIFO 是我們設計中常用的工具,因為它們使我們能夠在進行信號和圖像處理時緩沖數據。我們還使用異步FIFO來處理數據總線的時鐘域交叉問題。

2022-11-04 09:14:11 3214

3214

3214

3214異步fifo詳解

和寫入數據(對于大型數據存儲,在性能上必然緩慢),其數據地址是由內部讀寫指針自動加一完成的,不能像普通的存儲器一樣,由地址線決定讀取或者寫入某個特定地址的數據,按讀寫是否為相同時鐘域分為同步和異步FIFO,這里主要介紹異步FIFO,主要用于跨時鐘域傳輸數據。 FIFO是

2022-12-12 14:17:41 2790

2790

2790

2790Verilog電路設計之單bit跨時鐘域同步和異步FIFO

FIFO用于為匹配讀寫速度而設置的數據緩沖buffer,當讀寫時鐘異步時,就是異步FIFO。多bit的數據信號,并不是直接從寫時鐘域同步到讀時鐘域的。

2023-01-01 16:48:00 941

941

941

941FIFO的原理和設計

FIFO(First In First Out)是異步數據傳輸時經常使用的存儲器。該存儲器的特點是數據先進先出(后進后出)。其實,多位寬數據的異步傳輸問題,無論是從快時鐘到慢時鐘域,還是從慢時鐘到快時鐘域,都可以使用 FIFO 處理。

2023-03-26 16:00:21 1824

1824

1824

1824

FIFO使用及其各條件仿真介紹

FIFO(First In First Out )先入先出存儲器,在FPG設計中常用于跨時鐘域的處理,FIFO可簡單分為同步FIFO和異步FIFO。

2023-04-25 15:55:28 2893

2893

2893

2893

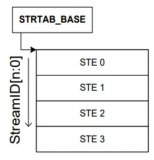

ARM SMMU Data structures之Stream Table

incoming transaction的StreamID可以找到一個STE。SMMU支持兩種Stream table格式,格式由Stream table base registers設置。

2023-05-11 09:22:57 714

714

714

714

跨時鐘域電路設計:多位寬數據通過FIFO跨時鐘域

FIFO是實現多位寬數據的異步跨時鐘域操作的常用方法,相比于握手方式,FIFO一方面允許發送端在每個時鐘周期都發送數據,另一方面還可以對數據進行緩存。需要注意的是對FIFO控制信號的管理,以避免發生

2023-05-11 14:01:27 1641

1641

1641

1641

Video In to AXI4-Stream IP核知識介紹

大家好!今日分享一些關于Video In to AXI4-Stream IP 核的知識。在具體學習IP核的過程中,我也將分享一些關于如何看xilinx英文文檔的技巧。

2023-05-18 14:55:16 966

966

966

966

FIFO設計—同步FIFO

FIFO是異步數據傳輸時常用的存儲器,多bit數據異步傳輸時,無論是從快時鐘域到慢時鐘域,還是從慢時鐘域到快時鐘域,都可以使用FIFO處理。

2023-05-26 16:12:49 978

978

978

978

Xilinx FPGA AXI4總線(一)介紹【AXI4】【AXI4-Lite】【AXI-Stream】

從 FPGA 應用角度看看 AMBA 總線中的 AXI4 總線。

2023-06-21 15:21:44 1729

1729

1729

1729

AXI實戰(二)-AXI-Lite的Slave實現介紹

可以看到,在AXI到UART中,是通過寄存器和FIFO進行中介的。因為從AXI總線往里看,其控制的是就是地址上所映射的寄存器。

2023-06-27 10:12:53 2229

2229

2229

2229

跨時鐘設計:異步FIFO設計

在ASIC設計或者FPGA設計中,我們常常使用異步fifo(first in first out)(下文簡稱為afifo)進行數據流的跨時鐘,可以說沒使用過afifo的Designer,其設計經歷是不完整的。廢話不多說,直接上接口信號說明。

2023-07-31 11:10:19 1220

1220

1220

1220

LogiCORE IP AXI4-Stream FIFO內核解決方案

LogiCORE IP AXI4-Stream FIFO內核允許以內存映射方式訪問一個AXI4-Stream接口。該內核可用于與AXI4-Stream IP接口,類似于LogiCORE IP AXI以太網內核,而無需使用完整的DMA解決方案。

2023-09-25 10:55:33 497

497

497

497

為什么異步fifo中讀地址同步在寫時鐘域時序分析不通過?

為什么異步fifo中讀地址同步在寫時鐘域時序分析不通過? 異步FIFO中讀地址同步在寫時鐘域時序分析不通過的原因可能有以下幾個方面: 1. 讀地址同步在寫時鐘域時序分析未覆蓋完全 在時序分析時,可能

2023-10-18 15:23:55 312

312

312

312同步FIFO和異步FIFO的區別 同步FIFO和異步FIFO各在什么情況下應用

簡單的一種,其特點是輸入和輸出都與時鐘信號同步,當時鐘到來時,數據總是處于穩定狀態,因此容易實現數據的傳輸和存儲。 而異步FIFO則是在波形的上升沿和下降沿上進行處理,在輸入輸出端口處分別增加輸入和輸出指針,用于管理數據的讀寫。異步FIFO的輸入和輸出可同時進行,中間可以

2023-10-18 15:23:58 790

790

790

790AXI傳輸數據的過程

以AXI4為例,有AXI full/lite/stream之分。 在Xilinx系列FPGA及其有關IP核中,經常見到AXI總線接口,AXI總線又分為三種: ?AXI-Lite,AXI-Full以及

2023-10-31 15:37:08 386

386

386

386

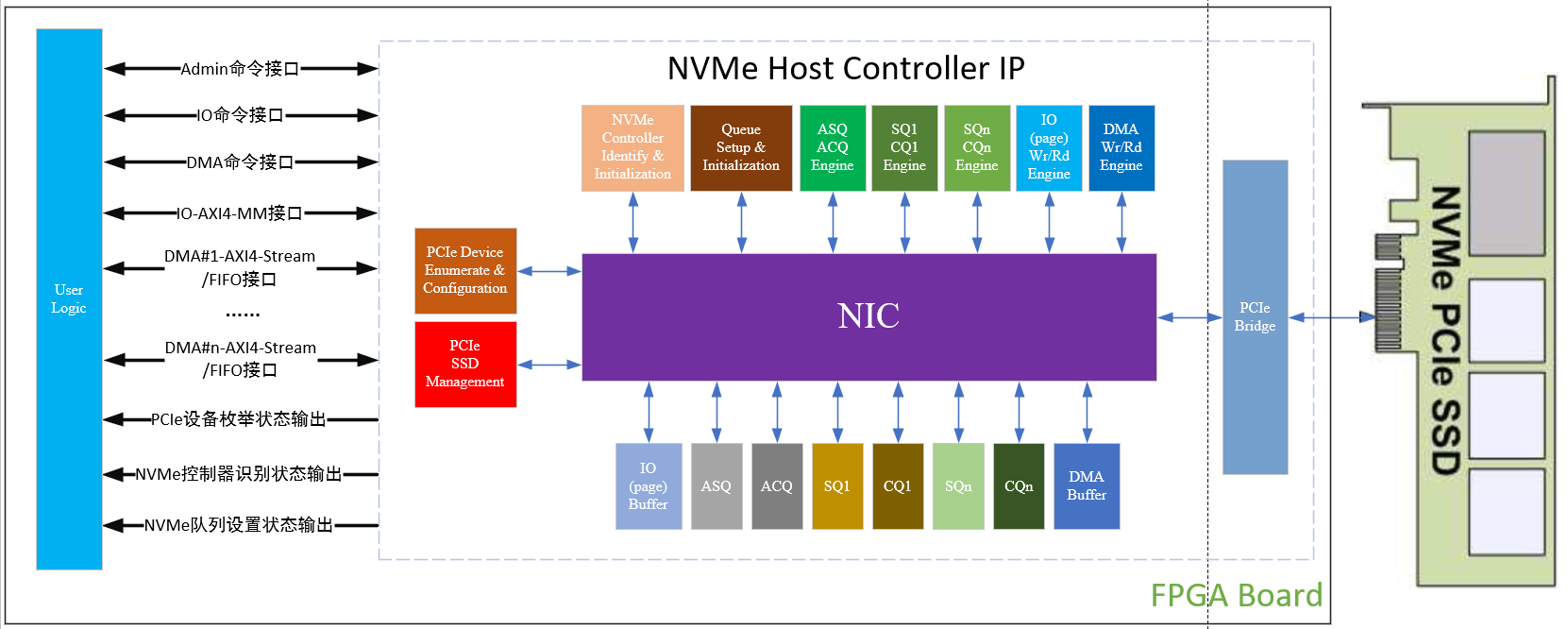

Xilinx FPGA NVMe控制器,NVMe Host Controller IP

NVMe Host Controller IP可以連接高速存儲PCIe SSD,無需CPU和外部存儲器,自動加速處理所有的NVMe協議命令,具備獨立的數據寫入AXI4-Stream/FIFO接口和數

2024-02-18 11:27:50 219

219

219

219

Xilinx高性能PCIe DMA控制器IP,8個DMA通道

或Scather Gather DMA,提供FIFO/AXI4-Stream用戶接口。

基于PCI Express Integrated Block,Multi-Channel PCIe RDMA

2024-02-22 11:11:55 156

156

156

156

電子發燒友App

電子發燒友App

評論