17個(gè)C語(yǔ)言新手編程時(shí)常犯的錯(cuò)誤及解決方式

2018-06-26 09:19:50 5798

5798

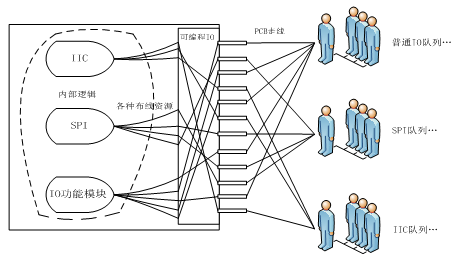

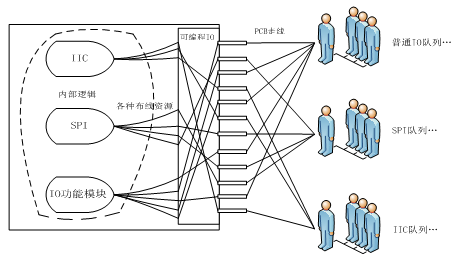

FPGA的IO可編程,這給邏輯設(shè)計(jì)和PCB設(shè)計(jì)帶來(lái)一定的靈活性和獨(dú)立性。在編程器的硬件實(shí)現(xiàn)中,FPGA就是充當(dāng)一個(gè)“千手觀音”的角色,為邏輯設(shè)計(jì)和PCB設(shè)計(jì)鋪路架橋,靈活實(shí)現(xiàn)各種功能。

2015-08-20 09:02:01 2408

2408

前邊寫了很多關(guān)于板上外圍器件的評(píng)測(cè)文章,這篇是FPGA純邏輯設(shè)計(jì),是FPGA的另一部分——算法實(shí)現(xiàn),上篇文章做了HDC1000傳感器的使用,當(dāng)時(shí)說(shuō)FPGA是不支持小數(shù)的,本篇記述的是FPGA如何去做

2020-06-17 10:17:27 6533

6533

請(qǐng)教各位,FPGA在邏輯設(shè)計(jì)中有哪些注意事項(xiàng)?

2021-05-07 07:21:53

圖像采集系統(tǒng)的結(jié)構(gòu)及工作原理是什么FPGA邏輯設(shè)計(jì)中的常見問(wèn)題有哪些

2021-04-29 06:18:07

以及高速數(shù)字電路的時(shí)序設(shè)計(jì)與優(yōu)化。相信通過(guò)三天的學(xué)習(xí),將會(huì)對(duì)學(xué)員在邏輯設(shè)計(jì)領(lǐng)域的工作和學(xué)習(xí)大有裨益。課程時(shí)間的安排上授課占60%,實(shí)驗(yàn)占40%。五、培訓(xùn)對(duì)象課程適合于使用FPGA器件進(jìn)行科研、教學(xué)和產(chǎn)品

2009-07-24 13:13:48

FPGA的設(shè)計(jì)和開發(fā)。1.可編程邏輯設(shè)計(jì)技術(shù)簡(jiǎn)介2.下一代可編程邏輯設(shè)計(jì)技術(shù)展望3.可編程邏輯器件硬件上的四大發(fā)展趨勢(shì)4.EDA軟件設(shè)計(jì)方法及發(fā)展趨勢(shì)5.FPGA的設(shè)計(jì)流程6.FPGA的常用開發(fā)工具

2014-12-12 09:38:19

/1pJ5bCtt Verilog和VHDL,它們的歷史淵源、孰優(yōu)孰劣這里就不提了。美國(guó)和中國(guó)***地區(qū)的邏輯設(shè)計(jì)公司大都以Verilog語(yǔ)言為主,國(guó)內(nèi)目前學(xué)習(xí)和使用Verilog的人數(shù)也在逐漸超過(guò)VHDL。從高

2015-03-16 12:00:54

通過(guò)LUT來(lái)實(shí)現(xiàn)。通常,初學(xué)者可以設(shè)計(jì)出正確的邏輯,但卻很容易忽略時(shí)序。在I/O口的設(shè)計(jì)中,與時(shí)序相關(guān)的缺陷對(duì)于產(chǎn)品是致命的,會(huì)影響產(chǎn)品的可靠性。因此,在掌握了結(jié)構(gòu)后,還必須關(guān)注芯片的一些重要時(shí)序參數(shù)

2014-08-21 15:40:22

與特點(diǎn)。本課程在FPGA應(yīng)用開發(fā)方面主要有:初級(jí)篇內(nèi)容包括Verilog HDL語(yǔ)言基礎(chǔ),Altera公司FPGA設(shè)計(jì)工具Quartus II軟件綜述,FPGA組合邏輯設(shè)計(jì)技術(shù)等,高級(jí)篇內(nèi)容包括

2014-04-23 15:28:29

;nbsp; 同時(shí)隨著FPGA在整個(gè)系統(tǒng)中開始扮演越來(lái)越重要的角色,FPGA的接口技術(shù),以及與外部處理器、功能芯片之間甚至是其他系統(tǒng)之間的接口技術(shù)也成為FPGA

2010-03-10 17:52:19

;nbsp; 同時(shí)隨著FPGA在整個(gè)系統(tǒng)中開始扮演越來(lái)越重要的角色,FPGA的接口技術(shù),以及與外部處理器、功能芯片之間甚至是其他系統(tǒng)之間的接口技術(shù)也成為FPGA

2010-03-10 17:58:29

的。話不多說(shuō),上貨。 在FPGA中何時(shí)用組合邏輯或時(shí)序邏輯 在設(shè)計(jì)FPGA時(shí),大多數(shù)采用Verilog HDL或者VHDL語(yǔ)言進(jìn)行設(shè)計(jì)(本文重點(diǎn)以verilog來(lái)做介紹)。設(shè)計(jì)的電路都是利用

2023-03-06 16:31:59

偏硬件:接口電路中的門組合電路;偏軟件:算法、接口控制器實(shí)現(xiàn)中的狀態(tài)機(jī)群或時(shí)序電路。隨著邏輯設(shè)計(jì)的深入,復(fù)雜功能設(shè)計(jì)一般基于同步時(shí)序電路方式。此時(shí),邏輯設(shè)計(jì)基本上就是在設(shè)計(jì)狀態(tài)機(jī)群或計(jì)數(shù)器等時(shí)序電路

2021-11-10 06:39:25

C語(yǔ)言編程容易混淆的問(wèn)題有哪些?

2021-04-19 11:15:55

后加入深圳某500強(qiáng)通信企業(yè)網(wǎng)絡(luò)產(chǎn)品線邏輯綜合開發(fā)部,從事接入網(wǎng)FPGA業(yè)務(wù)邏輯開發(fā)工作至今。參與或直接負(fù)責(zé)接入邏輯OLT設(shè)備中QM隊(duì)列調(diào)度模塊邏輯設(shè)計(jì),VMAC協(xié)議邏輯設(shè)計(jì),以太OAM協(xié)議邏輯設(shè)計(jì)

2015-03-11 16:13:48

`MCS-51單片機(jī)與FPGA接口的邏輯設(shè)計(jì).........`

2013-06-08 11:25:29

MPEG-2編碼復(fù)用器中的FPGA邏輯設(shè)計(jì),看完你就懂了

2021-04-29 06:13:34

Sequential Logic Design principles 時(shí)序邏輯設(shè)計(jì)原則[hide][/hide]

2009-09-26 13:00:22

;nbsp; 同時(shí)隨著FPGA在整個(gè)系統(tǒng)中開始扮演越來(lái)越重要的角色,FPGA的接口技術(shù),以及與外部處理器、功能芯片之間甚至是其他系統(tǒng)之間的接口技術(shù)也成為FPGA

2010-04-16 14:48:22

請(qǐng)問(wèn)一下,現(xiàn)在c語(yǔ)言編程FPGA并不是十分的廣泛,那么,以后未來(lái)的趨勢(shì)是不是使用c語(yǔ)言來(lái)進(jìn)行FPGA編程,就是DSP,ARM一樣呢?那Verilog和vhdl會(huì)不會(huì)被淘汰啊?

2015-04-15 16:44:11

靜態(tài)時(shí)序分析與邏輯設(shè)計(jì)

2015-05-27 12:28:46

連接到I/O模塊。FPGA的邏輯是通過(guò)向內(nèi)部靜態(tài)存儲(chǔ)單元加載編程數(shù)據(jù)來(lái)實(shí)現(xiàn)的,存儲(chǔ)在存儲(chǔ)器單元中的值決定了邏輯單元的邏輯功能以及各模塊之間或模塊與I/O間的聯(lián)接方式,并最終決定了FPGA所能實(shí)現(xiàn)的功能

2019-08-11 04:30:00

交通燈控制邏輯設(shè)計(jì)n 1、紅、綠、黃發(fā)光二極管作信號(hào)燈,用傳感器或邏輯開關(guān)作檢測(cè)車輛是否到來(lái)的信號(hào),實(shí)驗(yàn)電路用邏輯開關(guān)代替。n 2、主干道處于常允許通行的狀態(tài),支干道有車來(lái)時(shí)才允許通行。主干道亮綠

2017-09-15 10:25:06

的PLD就可以了。CPLD和FPGA??可編程邏輯器件的兩種類型是現(xiàn)場(chǎng)可編程門陣列(FPGA)和復(fù)雜可編程邏輯器件(CPLD)。在這兩類可編程邏輯器件中,FPGA提供了最高的邏輯密度、最豐富的特性和最高

2009-05-29 11:36:21

系統(tǒng)工程師第一階段的課程主要幫助學(xué)員了解FPGA系統(tǒng)設(shè)計(jì)的基礎(chǔ)知識(shí),掌握FPGA最小系統(tǒng)硬件電路設(shè)計(jì)方法,學(xué)會(huì)操作QuartusII軟件來(lái)完成FPGA的設(shè)計(jì)和開發(fā)。1.可編程邏輯設(shè)計(jì)技術(shù)簡(jiǎn)介2.下一代

2018-09-19 11:34:03

華為大規(guī)模邏輯設(shè)計(jì)指導(dǎo)書。非常詳細(xì)地介紹了邏輯設(shè)計(jì)的規(guī)范要求及方法。

2020-01-27 17:58:38

單片機(jī)與FPGA總線接口邏輯設(shè)計(jì)1、利用FPGA內(nèi)部RAM存儲(chǔ)256個(gè)字節(jié)數(shù)據(jù),并將數(shù)據(jù)發(fā)送到單片機(jī)并在串口調(diào)試工具顯示;2、通過(guò)串口調(diào)試工具經(jīng)單片機(jī)發(fā)送數(shù)據(jù)到FPGA,并通過(guò)LED顯示。

2012-03-04 13:09:58

降低設(shè)備復(fù)雜性、強(qiáng)化易配置性、加快產(chǎn)品上市速度的要求使得可編程邏輯技術(shù)在更多的應(yīng)用領(lǐng)域中得到進(jìn)一步地?cái)U(kuò)展和滲透。最近業(yè)界發(fā)生的兩個(gè)事件可充分地證明這一點(diǎn)。 美國(guó)國(guó)家儀器公司(NI)在其最新推出

2019-07-15 08:15:30

完成乘法,實(shí)現(xiàn)3×4,只要通過(guò)寫程序讓3連續(xù)加4次就可以完成了。而可編程邏輯器件的兩種主要類型是現(xiàn)場(chǎng)可編程門陣列(FPGA)和復(fù)雜可編程邏輯器件(CPLD)。 在這兩類可編程邏輯器件中,FPGA提供了

2014-04-15 10:02:54

了如何通過(guò)FPGA實(shí)現(xiàn)RS 232接口的時(shí)序邏輯設(shè)計(jì)。關(guān)鍵詞:FPGA;時(shí)序電路;RS 232;串行通信

2019-06-19 07:42:37

夏宇聞數(shù)字邏輯設(shè)計(jì),學(xué)習(xí)FPGA的前提經(jīng)典功課教程。

2013-02-06 21:45:42

本文使用符合PCI電氣特性的FPGA芯片進(jìn)行簡(jiǎn)化的PCI接口邏輯設(shè)計(jì),實(shí)現(xiàn)了33MHz、32位數(shù)據(jù)寬度的PCI從設(shè)備模塊的接口功能,節(jié)約了系統(tǒng)的邏輯資源,且可以將其它用戶邏輯集成在同一塊芯片,降低了成本,增加了設(shè)計(jì)的靈活性。

2021-05-08 08:11:59

一定難度。而且要更改FPGA內(nèi)部的邏輯也不是十分靈活。本文探討一種在嵌入式系統(tǒng)中,靈活,方便地動(dòng)態(tài)配置FPGA 的方法。 具有FPGA 設(shè)計(jì)能力的硬件工程師可以設(shè)計(jì)各種F...

2021-12-21 06:13:49

目前無(wú)論FPGA還是CPLD的主流設(shè)計(jì)方法都是使用硬件描述語(yǔ)言(通常是verilog 或者VHDL)進(jìn)行,然后借助EDA工具 完成編譯、布局布線。實(shí)際設(shè)計(jì)中很少使用原理圖方式去搭邏輯電路。 因此來(lái)說(shuō)

2014-09-16 17:52:27

部門內(nèi)邏輯開發(fā)問(wèn)題的定位及排障工作;3.與軟件、硬件配合進(jìn)行產(chǎn)品調(diào)試測(cè)試工作。 崗位要求: 1.從事FPGA相關(guān)開發(fā)經(jīng)驗(yàn)在5年以上;2.精通常用接口邏輯,如DDR、SPI、LOCAL BUS、I2C

2016-01-21 14:42:39

要使用哪種方法去驗(yàn)證 FPGA 的邏輯設(shè)計(jì)?FPGA的優(yōu)缺點(diǎn)是什么?

2021-04-08 06:57:32

最近在學(xué)習(xí)使用時(shí)碰到一些麻煩,還望幫助啊。就是想知道如何在Zynq-7000中進(jìn)行FPGA邏輯設(shè)計(jì),產(chǎn)生LTE-A信號(hào),從而輸入到AD9361,搭建成一個(gè)mimo軟件無(wú)線電平臺(tái)。。

2015-04-03 11:03:46

靜態(tài)時(shí)序分析與邏輯設(shè)計(jì)

2017-12-08 14:49:57

本文運(yùn)用黑盒測(cè)試的基本理論,提出了FPGA邏輯設(shè)計(jì)的測(cè)試模型,分析了FPGA邏輯設(shè)計(jì)的基本方法和步驟,最后結(jié)合一個(gè)實(shí)際項(xiàng)目說(shuō)明了FPGA邏輯設(shè)計(jì)的測(cè)試驗(yàn)證過(guò)程。關(guān)鍵詞:黑盒

2009-08-19 09:12:41 9

9 采用 Verilog HDL 語(yǔ)言在Altera 公司的FPGA 芯片上實(shí)現(xiàn)了RISC_CPU 的關(guān)鍵部件狀態(tài)控制器的設(shè)計(jì),以及在與其它各種數(shù)字邏輯設(shè)計(jì)方法的比較下,顯示出使用Verilog HDL語(yǔ)言的優(yōu)越性.關(guān)鍵詞

2009-08-21 10:50:05 69

69 中規(guī)模集成時(shí)序邏輯設(shè)計(jì):計(jì)數(shù)器:在數(shù)字邏輯系統(tǒng)中,使用最多的時(shí)序電路要算計(jì)數(shù)器了。它是一種對(duì)輸入脈沖信號(hào)進(jìn)行計(jì)數(shù)的時(shí)序邏輯部件。9.1.1 計(jì)數(shù)器的分類1.按數(shù)制

2009-09-01 09:09:09 13

13 設(shè)計(jì)一種基于MCS-51 單片機(jī)與FPGA/CPLD 的總線接口邏輯,實(shí)現(xiàn)單片機(jī)與可編程邏輯器件數(shù)據(jù)與控制信息的可靠通信,使可編程邏輯器件與單片機(jī)相結(jié)合,優(yōu)勢(shì)互補(bǔ),組成靈活的、軟硬件

2009-09-22 10:16:40 83

83 本文介紹了一種基于FPGA 的用自定義串口命令的方式實(shí)現(xiàn)MDIO 接口邏輯設(shè)計(jì)的方法,并對(duì)系統(tǒng)結(jié)構(gòu)進(jìn)行了模塊化分解以適應(yīng)自頂向下的設(shè)計(jì)方法。所有功能的實(shí)現(xiàn)全部采用VHDL 進(jìn)行描

2009-12-26 16:48:44 103

103 FPGA編程語(yǔ)言的設(shè)計(jì)

典型的復(fù)雜數(shù)字邏輯系統(tǒng)主要有:1.高速通信系統(tǒng)2.遙測(cè)系統(tǒng) 遙測(cè)系統(tǒng)3.高速并行計(jì)算邏輯4.高速導(dǎo)航系統(tǒng)5.高速對(duì)抗系統(tǒng)6.

2010-02-09 11:24:59 217

217 摘要:“邏輯設(shè)計(jì)”課是近二、三十年隨著信息類一批新專業(yè)(自動(dòng)化、計(jì)算機(jī)、通信和信息等)陸續(xù)建立而開設(shè)的一門重要的學(xué)科基礎(chǔ)課。只要掌握“邏輯設(shè)計(jì)”課的特點(diǎn)和主要問(wèn)題

2010-05-25 10:10:29 0

0 ASIC與大型邏輯設(shè)計(jì)實(shí)習(xí)課

AgendaCell Base IC DesignModelSimLibraryProjectVHDL Compiler & SimulationSimulation WindowsTutorialLab

2010-06-19 09:45:20 0

0 摘要:簡(jiǎn)要介紹了現(xiàn)場(chǎng)可編程門陣列(FPGA)的特性,并結(jié)合MPEG-2編碼復(fù)用器開發(fā)過(guò)程中的經(jīng)驗(yàn),給出了在MAX+ PLUS II提供的設(shè)計(jì)環(huán)境下FPGA邏輯設(shè)計(jì)的

2006-05-26 21:52:22 704

704

摘要:提出了一種基于FPGA的實(shí)時(shí)、多分辨率圖像采集系統(tǒng)的控制邏輯設(shè)計(jì)方案;并對(duì)其中的圖像數(shù)據(jù)預(yù)處理和幀存乒乓刷新機(jī)制這兩個(gè)關(guān)鍵技術(shù)進(jìn)行了闡述;為了

2009-06-20 14:34:06 497

497

摘要:提出了一種基于FPGA的實(shí)時(shí)、多分辨率圖像采集系統(tǒng)的控制邏輯設(shè)計(jì)方案;并對(duì)其中的圖像數(shù)據(jù)預(yù)處理和幀存乒乓刷新機(jī)制這兩個(gè)關(guān)鍵技術(shù)進(jìn)行了闡述;為了

2009-06-20 14:38:05 476

476

摘要:簡(jiǎn)要介紹了現(xiàn)場(chǎng)可編程門陣列(FPGA)的特性,并結(jié)合MPEG-2編碼復(fù)用器開發(fā)過(guò)程中的經(jīng)驗(yàn),給出了在MAX+ PLUS II提供的設(shè)計(jì)環(huán)境下FPGA邏輯設(shè)計(jì)的一些方法和技巧。設(shè)計(jì)的邏

2009-06-20 14:40:35 580

580

為了提高溫度保護(hù)系統(tǒng)的可靠性,在溫度保護(hù)的邏輯設(shè)計(jì)中可采用容錯(cuò)設(shè)計(jì),即盡可能考慮測(cè)溫環(huán)節(jié)在運(yùn)行中容易出現(xiàn)的故障,并通過(guò)預(yù)先設(shè)置的邏輯措施來(lái)識(shí)別錯(cuò)誤的溫度信號(hào),以防保護(hù)系統(tǒng)誤動(dòng)。

2011-01-21 11:16:21 1269

1269

組合邏輯設(shè)計(jì)實(shí)例_國(guó)外:

2011-12-16 15:08:59 24

24 本文利用糾錯(cuò)編碼的基本知識(shí),提出了一種簡(jiǎn)單實(shí)用的能自動(dòng)糾正一位錯(cuò)誤和檢查兩位錯(cuò)誤的編碼方法,并且通過(guò)VHDL語(yǔ)言編程,用FPGA器件來(lái)實(shí)現(xiàn)。在我們自己的嵌入式系統(tǒng)中,EDAC電路

2012-01-18 16:29:15 2387

2387

《數(shù)字電路與邏輯設(shè)計(jì)》答案

2012-06-25 08:19:15 23

23 邏輯綜合帶來(lái)了數(shù)字設(shè)計(jì)行業(yè)的革命,有效地提高了生產(chǎn)率,減少了設(shè)計(jì)周期時(shí)間。在手動(dòng)轉(zhuǎn)換設(shè)計(jì)的年代,設(shè)計(jì)過(guò)程受到諸多限制,結(jié)更容易帶來(lái)人為的錯(cuò)誤。而一個(gè)小小的錯(cuò)誤就導(dǎo)

2012-06-25 15:21:14 44

44 FPGA編程語(yǔ)言的設(shè)計(jì)有需要的下來(lái)看看。

2016-05-10 10:46:40 23

23 市場(chǎng)上邏輯分析儀廠家眾多,大家在選擇邏輯分析儀時(shí)會(huì)關(guān)注存儲(chǔ)深度、采樣率、協(xié)議解碼等的對(duì)比,但往往容易忽略探頭的選擇,在這里跟大家好好分享下探頭在邏輯分析儀中起著什么重要作用。

2016-04-28 17:37:26 2662

2662

多分辨率圖像實(shí)時(shí)采集系統(tǒng)的FPGA邏輯設(shè)計(jì)

2016-08-29 15:02:03 6

6 華為靜態(tài)時(shí)序分析與邏輯設(shè)計(jì),基礎(chǔ)的資料,快來(lái)下載吧

2016-09-01 15:44:10 56

56 分壓電路容易忽略的小錯(cuò)誤,感興趣的小伙伴們可以瞧一瞧。

2016-09-18 17:15:05 0

0 PLD可以是低邏輯密度器件,采用被稱為復(fù)雜可編程邏輯器件(CPLD)的非易失元件構(gòu)建;也可以是高密度器件,基于現(xiàn)場(chǎng)可編程門陣列(FPGA)的SRAM查找表(LUT)搭建。在可配置邏輯陣列中,除了

2017-09-12 17:08:30 14

14 在很多應(yīng)用中,單片機(jī)需要在片外擴(kuò)展相關(guān)資源,如程序存儲(chǔ)器、數(shù)據(jù)存儲(chǔ)器、I/O口以及中斷源等。隨著可編程邏輯器件(PLD)及EDA技術(shù)的發(fā)展,在系統(tǒng)設(shè)計(jì)中經(jīng)常會(huì)用到FPGA/CPLD來(lái)擴(kuò)展單片機(jī)的相關(guān)

2017-11-23 09:37:14 3407

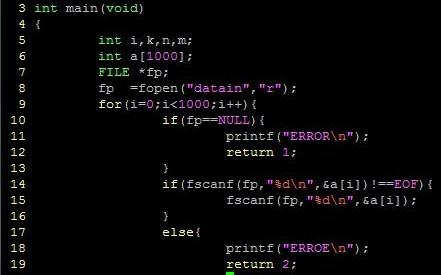

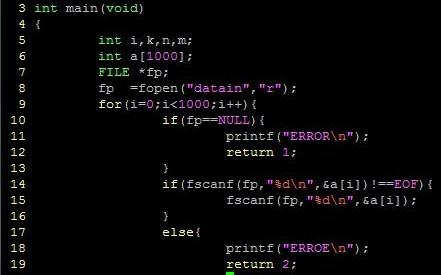

3407 C語(yǔ)言的最大特點(diǎn)是:功能強(qiáng)、使用方便靈活。C編譯的程序?qū)φZ(yǔ)法檢查并不象其它高級(jí)語(yǔ)言那么嚴(yán)格,這就給編程人員留下“靈活的余地”,但還是由于這個(gè)靈活給程序的調(diào)試帶來(lái)了許多不便,尤其對(duì)初學(xué)C語(yǔ)言的人來(lái)說(shuō),經(jīng)常會(huì)出一些連自己都不知道錯(cuò)在哪里的錯(cuò)誤,本文總結(jié)積累了一些C編程時(shí)常犯的錯(cuò)誤以供參考學(xué)習(xí)。

2018-02-27 14:51:49 6018

6018 講解C編程中容易忽視和犯錯(cuò)誤的地方

2018-03-28 17:15:53 2

2 看著有錯(cuò)的程序,不知該如何改起,本人通過(guò)對(duì)C的學(xué)習(xí),積累了一些C編程時(shí)常犯的錯(cuò)誤,寫給各位同學(xué)以供參考。

2018-09-22 15:42:00 2718

2718 知道錯(cuò)在哪里的錯(cuò)誤。看著有錯(cuò)的程序,不知該如何改起,通過(guò)對(duì)C的學(xué)習(xí),積累了一些C編程時(shí)常犯的錯(cuò)誤,以供參考。 1、書寫標(biāo)識(shí)符時(shí),忽略了大小寫字母的區(qū)別 main() { int a=5; printf(“%d”,A); } 編譯程序把a(bǔ)和A認(rèn)為是兩個(gè)不同的變量名

2018-10-24 18:37:01 241

241 中的一種半定制電路而出現(xiàn)的,既解決了定制電路的不足,又克服了原有可編程器件門電路數(shù)有限的缺點(diǎn)。所以,要想玩轉(zhuǎn)FPGA,就必須理解FPGA內(nèi)部的工作原理,學(xué)習(xí)如何利用這些單元實(shí)現(xiàn)復(fù)雜的邏輯設(shè)計(jì)。

2018-11-06 17:20:47 2531

2531 本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA視頻教程之FPGA設(shè)計(jì)中時(shí)序邏輯設(shè)計(jì)要點(diǎn)的詳細(xì)資料說(shuō)明免費(fèi)下載。

2019-03-27 10:56:04 20

20 FPGA 的基本結(jié)構(gòu)包括可編程輸入輸出單元,可配置邏輯塊,數(shù)字時(shí)鐘管理模塊,嵌入式塊RAM,布線資源,內(nèi)嵌專用硬核,底層內(nèi)嵌功能單元。由于FPGA具有布線資源豐富,可重復(fù)編程和集成度高,投資較低的特點(diǎn),在數(shù)字電路設(shè)計(jì)領(lǐng)域得到了廣泛的應(yīng)用。

2019-11-21 07:03:00 1842

1842 本文檔的主要內(nèi)容詳細(xì)介紹的是Verilog HDL語(yǔ)言組合邏輯設(shè)計(jì)方法以及QuartusII軟件的一些高級(jí)技巧。

2019-07-03 17:36:12 19

19 經(jīng)常看到不少人在論壇里發(fā)問(wèn),FPGA是不是用C語(yǔ)言開發(fā)的?國(guó)外有些公司專注于開發(fā)解決編譯器這方面問(wèn)題,目的讓其能夠達(dá)到用C語(yǔ)言替代VHDL語(yǔ)言的目的,也開發(fā)出了一些支持用c語(yǔ)言對(duì)FPGA進(jìn)行編程的開發(fā)工具。但在使用多的FPGA編程語(yǔ)言還是verilog和VHDL語(yǔ)言,一般不使用C語(yǔ)言進(jìn)行編程。

2020-07-29 16:37:37 23118

23118 Python是一門簡(jiǎn)單易學(xué)的編程語(yǔ)言,語(yǔ)法簡(jiǎn)潔而清晰,并且擁有豐富和強(qiáng)大的類庫(kù)。與其它大多數(shù)程序設(shè)計(jì)語(yǔ)言使用大括號(hào)不一樣 ,它使用縮進(jìn)來(lái)定義語(yǔ)句塊。 在平時(shí)的工作中,Python開發(fā)者很容易犯一些小錯(cuò)誤

2021-01-02 10:13:00 838

838 本文檔的主要內(nèi)容詳細(xì)介紹的是華為FPGA硬件的靜態(tài)時(shí)序分析與邏輯設(shè)計(jì)包括了:靜態(tài)時(shí)序分析一概念與流程,靜態(tài)時(shí)序分析一時(shí)序路徑,靜態(tài)時(shí)序分析一分析工具

2020-12-21 17:10:54 18

18 Bash Pitfalls[1] 文章介紹了 40 多條日常 Bash 編程中,老手和新手都容易忽略的錯(cuò)誤編程習(xí)慣。每條作者在給出錯(cuò)誤的范例上,詳細(xì)分析與解釋錯(cuò)誤的原因,同時(shí)給出正確的改寫建議

2022-06-12 16:48:27 1340

1340 我在數(shù)字邏輯設(shè)計(jì)方面并沒(méi)有經(jīng)驗(yàn)。也就是說(shuō),直到最近我才決定嘗試設(shè)計(jì)自己的 CPU,并在 FPGA 上運(yùn)行!如果你也是一名軟件工程師,并對(duì)硬件設(shè)計(jì)有興趣,那么我希望這一系列關(guān)于我所學(xué)到的知識(shí)的文章能夠?qū)δ阌兴鶐椭⒆屇愀械接腥ぁ1鞠盗形恼碌牡谝徊糠种校瑢⒒卮鹨韵聠?wèn)題:

2022-11-01 09:25:03 1254

1254 上文中我們指出,不管我們是創(chuàng)建自定義 ASIC 芯片還是配置 FPGA,都可以使用相同的數(shù)字邏輯設(shè)計(jì)工具。

2022-11-01 09:23:39 1441

1441 XILINX是可編程邏輯芯片,由多個(gè)系列的性能可以滿足一般的邏輯設(shè)計(jì)要求,如賽靈思7系列,Xilinx?7系列FPGA由四個(gè)FPGA系列組成 7A 7V 7S 7K,可滿足各種系統(tǒng)要求,從低

2022-11-03 14:39:54 1446

1446 摘要:FPGA的IO可編程,這給邏輯設(shè)計(jì)和PCB設(shè)計(jì)帶來(lái)一定的靈活性和獨(dú)立性。

2023-07-11 16:27:08 557

557

FPGA(Field-Programmable Gate Array)可以使用多種編程語(yǔ)言進(jìn)行編程,具體選擇的編程語(yǔ)言取決于開發(fā)人員的偏好、設(shè)計(jì)需求和FPGA開發(fā)工具的支持。

2023-07-24 15:06:59 2415

2415 PLC新手在使用和編程PLC時(shí)容易犯以下一些常見錯(cuò)誤: (1)電氣接線錯(cuò)誤:PLC的輸入和輸出需要正確地與外部設(shè)備進(jìn)行連接。新手可能會(huì)犯接線錯(cuò)誤,例如接錯(cuò)線圈端子、斷開或短路電線等。這可能導(dǎo)致PLC

2023-10-11 17:10:01 348

348 PLC在機(jī)械加工類的專用設(shè)備中有很大的應(yīng)用,然而有一個(gè)問(wèn)題常常被初入門的編程人員忽略,即延時(shí)問(wèn)題。

2023-11-29 14:35:15 249

249

更高的靈活性和可重構(gòu)性。在FPGA中,用戶可以通過(guò)編程來(lái)配置硬件單元之間的連接關(guān)系,從而實(shí)現(xiàn)所需的電路功能。接下來(lái),我們將詳細(xì)介紹FPGA的概念、應(yīng)用、編程語(yǔ)言等方面。 一、FPGA的概念與原理 FPGA是一種基于可編程邏輯器件(PLD)的芯片,它具有硬件電路的部分可配置性。與傳統(tǒng)的專

2024-02-04 15:26:30 338

338 電子發(fā)燒友網(wǎng)站提供《數(shù)字電路與邏輯設(shè)計(jì).ppt》資料免費(fèi)下載

2024-03-11 09:21:44 0

0 電子發(fā)燒友網(wǎng)站提供《基于VHDL的組合邏輯設(shè)計(jì).ppt》資料免費(fèi)下載

2024-03-11 09:23:29 2

2 FPGA芯片主要使用的編程語(yǔ)言包括Verilog HDL和VHDL。這兩種語(yǔ)言都是硬件描述語(yǔ)言,用于描述數(shù)字系統(tǒng)的結(jié)構(gòu)和行為。

2024-03-14 16:07:38 85

85 和VHDL都是用于邏輯設(shè)計(jì)的硬件描述語(yǔ)言,并且都已成為IEEE標(biāo)準(zhǔn)。它們能形式化地抽象表示電路的結(jié)構(gòu)和行為,支持邏輯設(shè)計(jì)中層次與領(lǐng)域的描述,具有電路仿真與驗(yàn)證機(jī)制以保證設(shè)計(jì)的正確性,并便于文檔管理和設(shè)計(jì)重用。 fpga用什么語(yǔ)言開發(fā) FPGA(現(xiàn)場(chǎng)可編程邏輯門陣列)的開發(fā)主要使用硬件描述語(yǔ)言(HD

2024-03-14 17:09:32 223

223 FPGA(現(xiàn)場(chǎng)可編程門陣列)的編程主要使用硬件描述語(yǔ)言(HDL),其中最常用的是Verilog HDL和VHDL。

2024-03-14 18:17:17 549

549 FPGA(現(xiàn)場(chǎng)可編程門陣列)的編程涉及到三種主要的硬件描述語(yǔ)言(HDL):VHDL(VHSIC Hardware Description Language)、Verilog以及SystemVerilog。這些語(yǔ)言在FPGA設(shè)計(jì)和開發(fā)過(guò)程中扮演著至關(guān)重要的角色。

2024-03-15 14:36:01 89

89 FPGA(現(xiàn)場(chǎng)可編程門陣列)的通用語(yǔ)言主要是指用于描述FPGA內(nèi)部邏輯結(jié)構(gòu)和行為的硬件描述語(yǔ)言。目前,Verilog HDL和VHDL是兩種最為廣泛使用的FPGA編程語(yǔ)言。

2024-03-15 14:36:34 87

87 FPGA語(yǔ)言,即現(xiàn)場(chǎng)可編程門陣列編程語(yǔ)言,是用于描述FPGA(Field Programmable Gate Array)內(nèi)部硬件結(jié)構(gòu)和行為的特定語(yǔ)言。它允許設(shè)計(jì)師以硬件描述的方式定義FPGA的邏輯

2024-03-15 14:50:26 166

166

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論