研究了相關(guān)的時(shí)序約束后,在設(shè)計(jì)中我們也不能忽視所能運(yùn)用到的物理約束。一個(gè)工程師最常用的物理約束是I/O管腳的放置和與每個(gè)I/O腳相關(guān)的參數(shù)定義(標(biāo)準(zhǔn)、驅(qū)動(dòng)能力等)。然而,還有其它類型的物理約束:

? 放置約束——定義元件位置

? 布線約束——定義信號布線

? I/O腳約束——定義I/O腳位置和I/O腳參數(shù)

? 配置約束——定義配置方法

按照慣例,有一些約束獨(dú)立于這些組之外。Vivado套件有三個(gè)約束,并且主要用于網(wǎng)表:

? DONT_TOUCH——用來防止優(yōu)化。在實(shí)現(xiàn)嚴(yán)格安全和高度可靠系統(tǒng)方面有很大的作用。

? MARK_DEBUG——用來保留一個(gè)RTL以便將來調(diào)試使用

正如上面提到的,最常用的約束同I/O腳放置及其配置相關(guān)。這些設(shè)置選項(xiàng)在較大的系統(tǒng)和硬件中有很重要的影響。總而言之,它們是操作起來很敏感的地方。

在FPGA上,I/O的管腳放置同時(shí)使用了用來定位物理管腳位置的放置約束和來配置I/O口屬性(例如I/O口標(biāo)準(zhǔn)、轉(zhuǎn)換率等)的I/O口約束。現(xiàn)代FPGA可以支持一定數(shù)量的單端和差分I/O口標(biāo)準(zhǔn)。這些是通過I/O約束來定義的。然而,工程師必須小心確保它們遵循著I/O分組規(guī)則,這個(gè)取決于最后的管腳放置。

但什么是I/O分組規(guī)則呢?FPGA上的每一個(gè)用戶I/O被組合在一起,形成有一定I/O腳數(shù)量的組。這些組有獨(dú)立的電壓供應(yīng),與組的層次相適應(yīng),支持寬范圍的I/O標(biāo)準(zhǔn)。

在Zynq Soc和其它賽靈思7系列設(shè)備上,I/O組被進(jìn)一步地分類歸屬到兩個(gè)整體組中的一個(gè)中去,從而進(jìn)一步約束了它們的性能并且要求工程師使用正確分類的正確接口。第一個(gè)I/O組分類是高性能(HP),即被優(yōu)化來獲得更高的數(shù)據(jù)速率。高性能組類中的I/O腳使用較低的操作電壓,并且不支持LVCMOS 3.3V和2.5V I/O電壓級別。寬范圍(HR)組分類被優(yōu)化來支持高性能組所不支持的寬電壓波動(dòng)I/O標(biāo)準(zhǔn)。下面的插圖顯示了賽靈思Kintex XC7K325T FPGA上可用的HR和HP I/O組。

7系列FPGA XC7K325T中HR和HP I/O分組情況

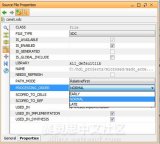

HP和HR組的I/O分組規(guī)則見用戶指南471中的表1-55。在開發(fā)初期,很值得我們花費(fèi)時(shí)間來理解這些規(guī)則。為了有助這個(gè),Vivado套件提供創(chuàng)建I/O布局工程的可能:

一旦我們決定了在哪個(gè)信號中使用哪種I/O組后,我們?nèi)匀挥心芰砀淖冃盘栻?qū)動(dòng)能力和轉(zhuǎn)換率。為了優(yōu)化板子上的信號完整性,這些參數(shù)會(huì)對你的硬件設(shè)計(jì)團(tuán)隊(duì)有很大的吸引力。這些選項(xiàng)也將影響板子設(shè)計(jì)的時(shí)序。

信號完整性(SI)工具需要一個(gè)I/O管腳的IBIS模型,利用文件->導(dǎo)出->導(dǎo)出IBIS模型選項(xiàng),當(dāng)我們已經(jīng)打開工程的時(shí)候,我們可以從Vivado套件中提取IBIS模型。這個(gè)導(dǎo)出文件可以用來關(guān)閉系統(tǒng)級別的SI問題和最終PCB布線的時(shí)序分析。

一旦設(shè)計(jì)團(tuán)隊(duì)總體上對SI性能和系統(tǒng)時(shí)序比較滿意,我們將會(huì)以下面一些設(shè)計(jì)中用到的I/O約束來結(jié)束這部分:

? 設(shè)置屬性管腳包裝 G17 [獲取端口{dout}]

? 設(shè)置屬性 IO標(biāo)準(zhǔn)LVCOMS33 [獲取端口{dout}]

? 設(shè)置屬性轉(zhuǎn)換率[獲取端口{dout}]

? 設(shè)置屬性驅(qū)動(dòng) 4[獲取端口{dout}]

我們也可以利用HP I/O組中可用的數(shù)字控制阻抗來適時(shí)地結(jié)束I/O,來增加系統(tǒng)的信號完整性,而不需要利用外部的結(jié)束計(jì)劃。

我們也必須考慮沒有信號來驅(qū)動(dòng)I/O時(shí)的影響。例如,如果I/O腳和外部連接器相連,我們可以利用I/O約束來實(shí)現(xiàn)一個(gè)上拉或下拉電阻以保護(hù)FPGA輸入信號免于懸空。懸空的輸入可能導(dǎo)致持續(xù)和間歇的系統(tǒng)問題。

當(dāng)然,通過用I/O塊自身來實(shí)現(xiàn)最終的輸出觸發(fā)器,我們也能使用物理約束來改進(jìn)設(shè)計(jì)時(shí)序。這樣做減少了時(shí)鐘輸出時(shí)間。在輸入信號上我們也可以做相同的工作,這樣可使設(shè)計(jì)滿足引腳到引腳所需建立和保持時(shí)間的要求。

在下一期博客中,我們將研究在FPGA邏輯設(shè)計(jì)中可以怎么利用放置和布線約束。

原文鏈接:

?Copyright 2014 Xilinx Inc

如需轉(zhuǎn)載,請注明出處

電子發(fā)燒友App

電子發(fā)燒友App

評論