1.GPU加速:GPU是一種多核處理器,GPU起初是用來進行圖形處理任務的,經過長時間的發展,GPU的發展是日趨復雜的,而且針對不同的領域也有不同。

當GPU被用來進行通用計算時,就產生了一些通用的計算框架,比如說Opencl和CUDA。比如說高端GPU TItan系列,其頻率可以達到1Ghz,擁有330GB的帶寬,提供每秒極高的算力,但是功耗也達到了驚人的250W。對于嵌入式的GPU,比如說TegraX1,擁有256個處理核,帶寬為25GB/s,同樣在1Ghz的頻率下,算力仍可以達到近Titan的十分之一,但是功耗只有10W。

2.ASIC加速:這些芯片分為兩類:第一類,用來做訓練和推理,這些芯片可以用來做DNN的訓練,也可以做DNN的推理。第二類,用來做推理,這些ASICs用來運行在GPU或者其他硬件上已經訓練好的模型,然后對訓練過的網絡進行修改,使得網絡可以運行在不同的ASIC上。

3.FPGA加速:FPGA是一種可以重復配置的電路。在延遲方面,FPGA要比GPU更好。FPGA可以提供很高的帶寬同時也可以降低延遲。

1.2 FPGA實現

要實現某種運算,其中一種方法就是將這種運算以電路的方式實現,而使用FPGA就是其中一個相對簡單的方法,使用者可以將FPGA配置為所需要的電路。基于指令的硬件是通過軟件來實現的,而FPGA是通過專用硬件實現的。對于一些需要低延遲的算法,比如說智能駕駛,FPGA的延遲要比GPU更低。當時用FPGA時,可以將延遲控制在1微秒或者1微秒之外,但是對于CPU來說,延遲低于50微秒,性能就已經很強了。除此之外,FPGA的定制化更強,延遲能夠人為的控制,FPGA不需要操作系統,內部也不需要想CPU一樣通過總線進行通行。

在FPGA中,可以連接任何的數據源,比如說網口或者傳感器,可以直接通過芯片的引腳就可以連接,這就和GPU與CPU形成了鮮明的對比(GPU和CPU與外界數據交互需要標準總線進行連接)。

FPGA的直連技術可以為數據提供很高的帶寬,同時也降低了時延。

2、為什么用FPGA來加速YOLOV2

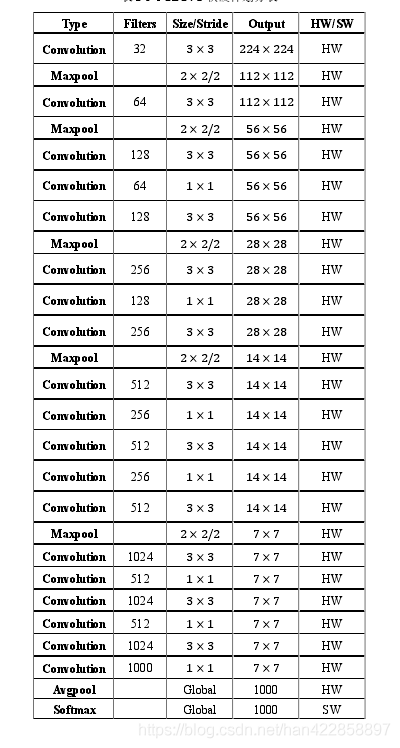

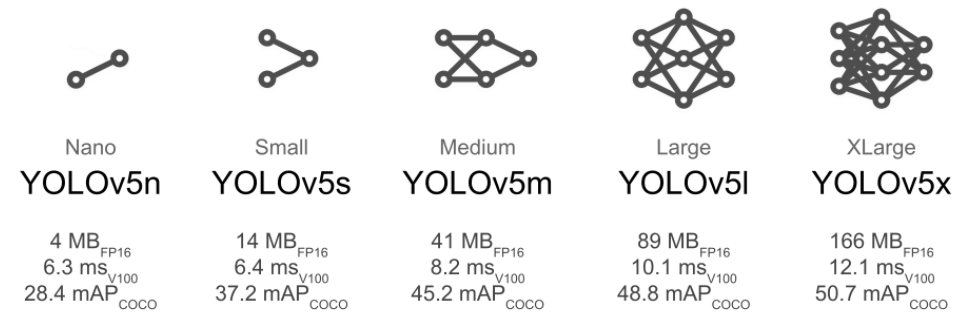

對于卷積核和池化的運算來說,因為是矩陣運算,這就需要相當高的算力。而由于卷積和池化運算都是流式運算,所以將他們放在FPGA中實現從而進行加速是一個很好的選擇。對于YOLOV2中的部分運算,比如說計算坐標圖像的預處理等,都是一些非流式運算,或者是標準運算,這些運算適合放在ARM中進行,于是將YOLOV2中的運算做一下劃分,充分利用軟硬件協同的優勢,從而對整個算法進行加速。

FPGA:卷積層和池化層

ARM:Softmax

3、FPGA簡介

3.1 FPGA的基本結構基本構成:CLB(可配置邏輯塊),IOS(輸入輸出模塊),IR(互聯資源)

FPGA的功能是由SRAM中的數據類配置的,所以大部分FPGA芯片中都是采用查找表結構的。FPGA中組合邏輯使用小型LUT實現的,這些LUT輸出端連接到D觸發器的輸入端,D在連接到其他邏輯電路或者是驅動IO來對其進行驅動。

FPGA中的邏輯是通過加載編程數據來實現的,這些編程數據通過內部靜態存儲單元來進行加載。存儲單元的值可以配置邏輯單元各個模塊的連接通路,以及邏輯單元所實現的功能,也可以配置IO的功能以及電氣鼠性等,這些最終構成了一個可以實現目標功能的FPGA系統。

3.2 FPGA的相對優勢:

與DSP和MCU相比,FPGA的運算速度較快,實現控制功能更加靈活,與傳統的CPLD相比,FPGA更適合做一些規模更大邏輯更復雜的設計。

(1).FPGA有六部分構成:可編程CLB,可編程IO,布線資源,嵌入式RAM,專用迎合以及內嵌功能模塊。CLPD功能更加簡單,構成:可編程IO,基本邏輯單元,布線pool。2).FPGA更容易實現時序邏輯,CPLD更適合大規模組合邏輯。

(3).FPGA連線資源非常豐富,且CLB的利用率很高。

(4)。同專用集成電路比,FPGA更加靈活,開發周期更短,可以降低成本,同時也可以保證保密性和可靠性。

4、PYNQ開發框架與HLS加速理論

4.1 PYNQ

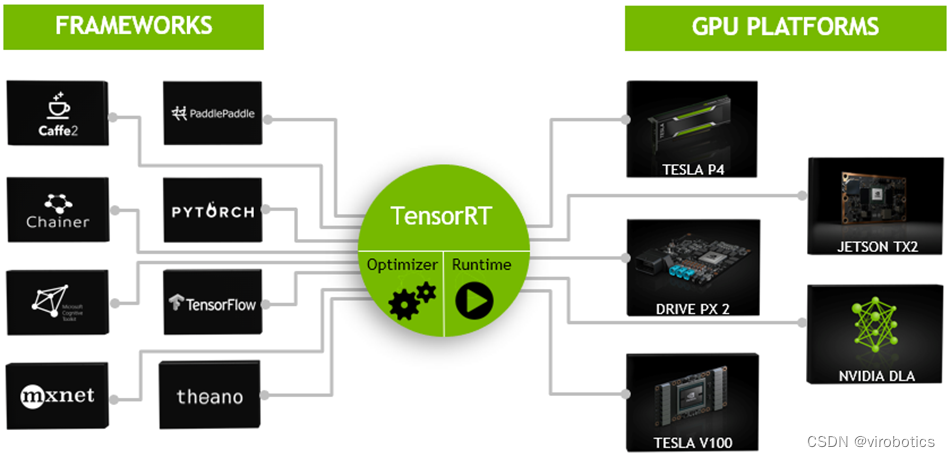

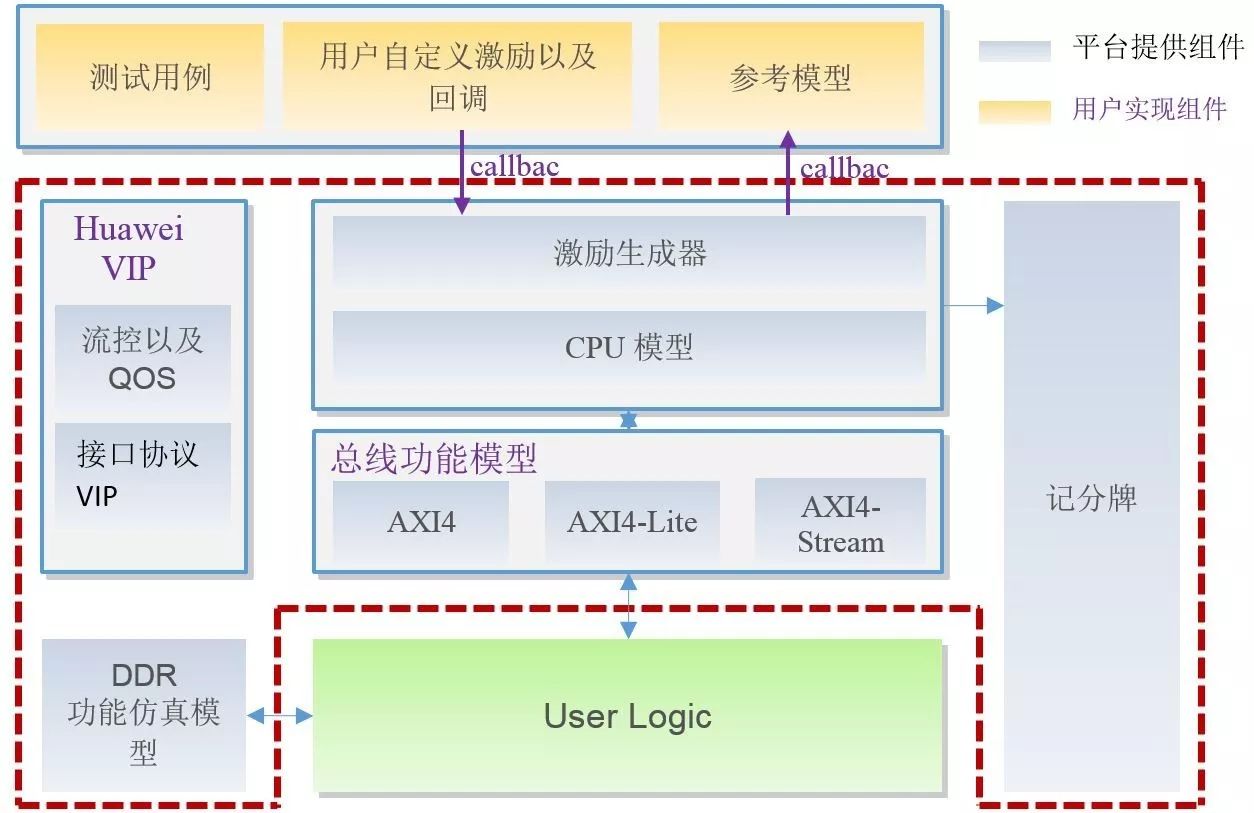

傳統的FPGA的框架有兩種,一種是FPGA與CPU互聯的,另一種是FPGA與RAM互聯的。但是這兩種開發對于然間人員來說很不友好,而PYNQ就很好的解決了這個問題,。PYNQ可以在ZYNQ上面運行,ZYNQ包含PL和PS部分,PS部分是ARM的處理器,上面可以運行LINUX系統,操作系統上運行ptyhon。PL部分是可編程邏輯資源,在開發過程中,首先在PL端設計IP核,將IP核配置成為AXI總線形式,然后在PS中對驅動函數進行調用。

PYQN是一種全新的開發框架,能夠用PYTHON對其進行快速的FPGA部署,在部署過程中不用研究硬件的實現細節。

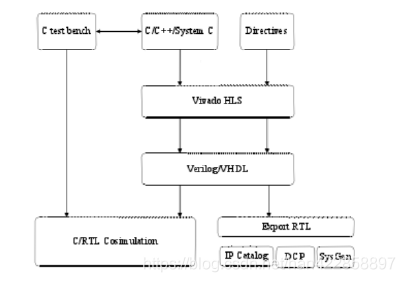

4.2 HLS

開發流程是基于C語言,能夠節約用戶大量的時間。其重要流程包括:C開發,C仿真,C綜合以及RTL綜合等。

4.2.1 用HLS加速IP

內層并行現實化:在FPGA實現深度學習算法中的一層,在計算時候對這一層進行復用,計算完一層以后將數據緩存到片外的DDR中,當進行下一層計算式,再將數據讀入運算單元中,在這個過程中需要FPGA的ARM來對IP核進行配置,包括輸入輸出通道的數量,卷積核的尺寸等。配置完成后,IP和就可以進行相應層的運算。

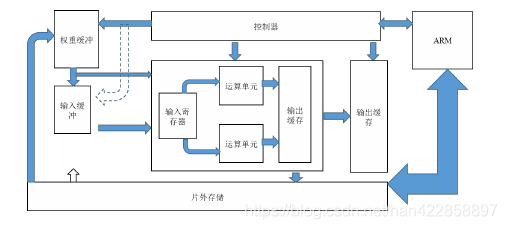

實現卷積IP核的經典架構

這個系統包含了片外DDR,ARM處理器,控制器,運算單元以及各種緩沖器。緩存器:輸入輸出,權重緩沖等。輸入的圖像首先要加載帶輸入的寄存器中,然后通過運算單元執行卷積操作,卷積操作是通過多個運算單元來運算的,以保證運算的速度。在進行卷積運算時,第一季輸出緩存中的數據會被輸出到第二級輸出緩存,在當前層運算完之后,運算結構就會成為下一級的運算輸出,用這樣的方式實現網絡每一層的加速。

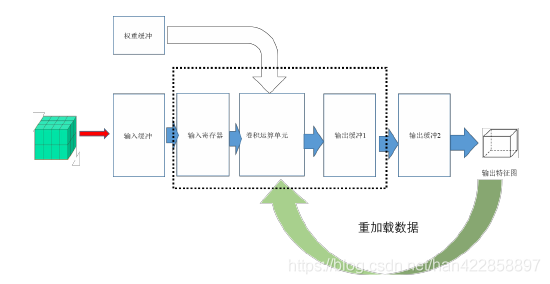

如上圖所展示的流程圖,可以實現網絡在單層內部運算的并行優化,不必將整個網絡全部展開,可以獎勵網絡的資源占用率,進而降低功耗,實現了新跟你乖面積以及功耗的平衡。如果想藥實現單層網絡的加速效果,就需要在層的內部實現流水。所以就需要一種數據拆分機制,將數據分為多個小塊,然后并行去處理這些數據。

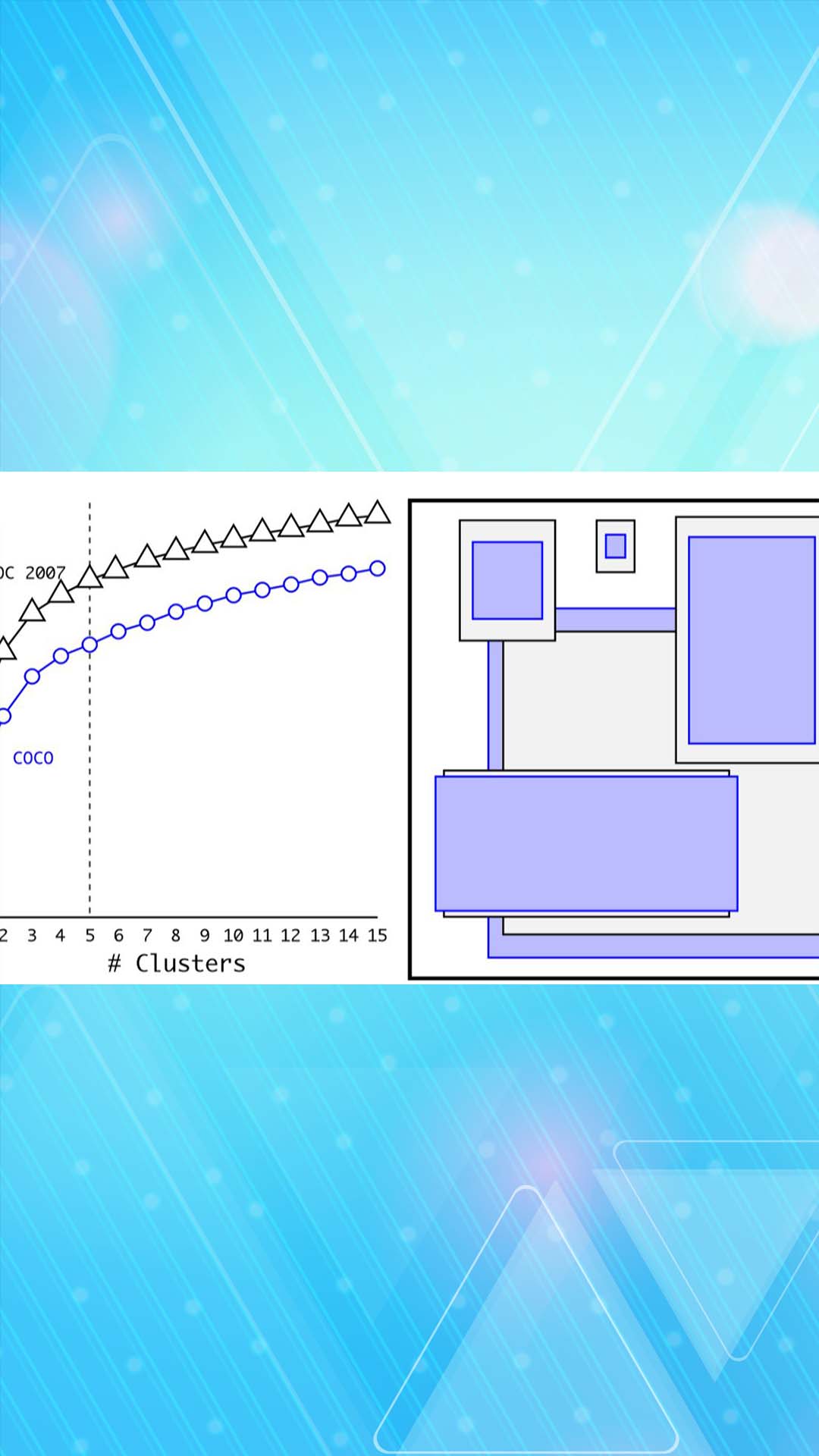

將圖像分割為多個小塊,每個小塊的尺寸為Tr X Tc X Tn,而這一塊經過計算之后得到的結果應該是卷積計算的部分和,尺寸為Th X Tl X Tm,在這個運算過程中,所欲要的權重尺寸是K X K X Tn X Tm。在處理完這一塊數據后,再處理這個特征圖的下一塊數據。這樣按快處理,直到本層的數據處理完成。

4.2.2 循環優化HLS針對循環的優化指令很多,這里只使用Loop Pipeline和Loop Unrolling。

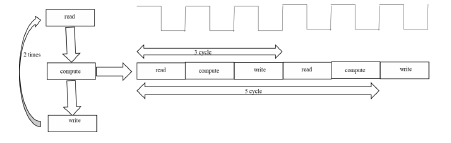

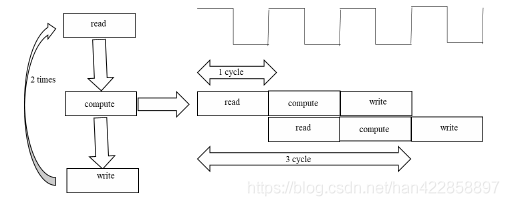

Loop Pipeline的作用是對循環的進行流水線化的并行處理,這種方式可以讓兩輪循環執行時間重疊,使得在本輪循環過程中下一輪循環也可以同時執行。

上述圖片是未經過流水化處理和經過處理的運算步驟,可以清楚地看出,如果以兩次迭代為例,未經過處理的運算需要經過5個時鐘周期才能完成運算,而經過流誰化處理的運算僅僅需要三個時鐘周期。

Loop Unorlling在沒有進行循環優化之前,循環的運行按照默認設置來操作的。而當進行循環展開后,循環的電路會被設置為N份,N一般有HLS中的指令factor來指定。比如說factor為2時,此時的迭代次數為8的話,那么迭代會被分為4次進行,內次是2個循環一次實現的。

4.3 硬件系統的構建

4.3.1 PL部分PL部分使用HLS來實現卷積神經網絡。

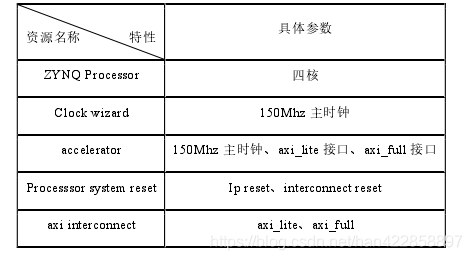

硬件配置如下:

最后將PL端生成的bitfile加載到FPGA中,最后在PC上觀察吃力后的圖像,進行結果分析與統計。

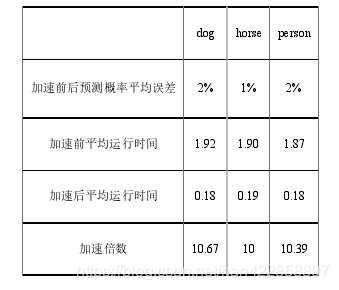

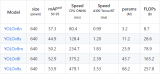

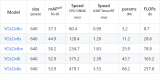

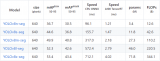

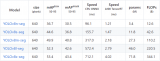

5、實驗結果

加速前后的時間對比。

電子發燒友App

電子發燒友App

評論