0引言

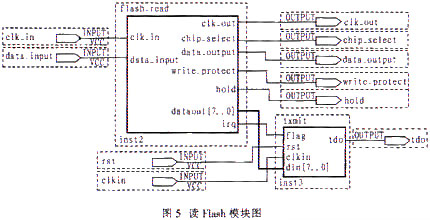

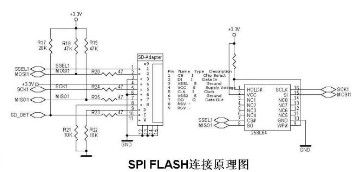

我們在進行嵌入式系統設計的過程中,根據需求,要設計出特定的嵌入式應用系統,而嵌入式應用系統的設計包含硬件系統設計和軟件系統設計兩個部分,并且這兩部分設計是互相關聯、密不可分的,嵌入式應用系統的設計經常需要在硬件和軟件設計之間進行權衡與折中。因此,這就要求嵌入式系統設計者具有較深厚的硬件和軟件基礎,并具有熟練應用的能力。在整個設計過程中,硬件設計是系統設計的基礎和核心,而各功能部件在整個設計中的調試又是該環節的重點和難點。本文詳細介紹嵌入式系統Flash存儲器的接口電路的調試。

1 Flash存儲器接口電路的引腳信號及各項特性

1.1 Flash存儲器接口電路的特點

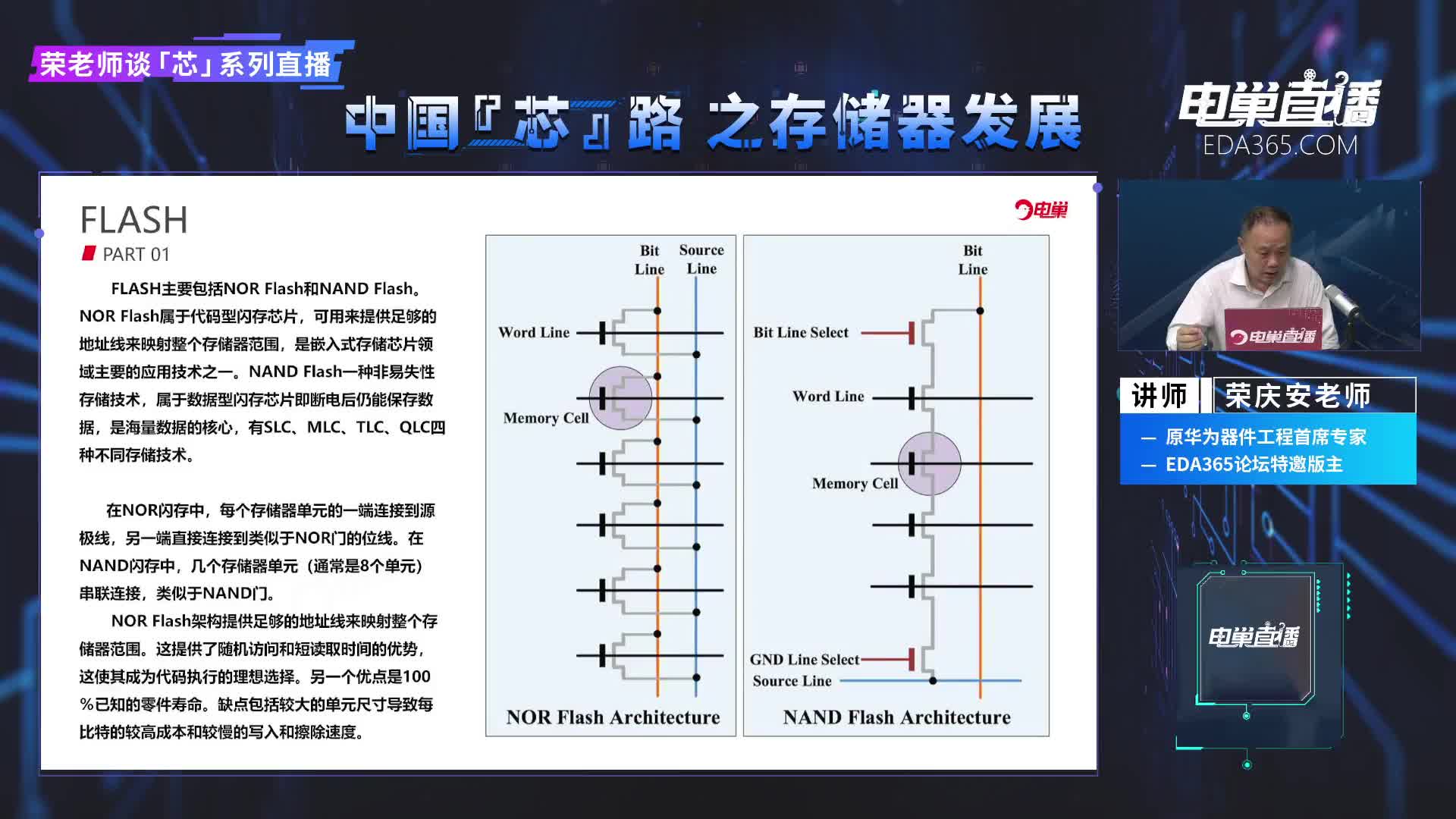

Flash存儲器是一種可在系統(In-System)中進行電擦寫,掉電后信息不會丟失的存儲器。它具有低功耗、大容量、擦寫速度快、可整片或分扇區在系統編程(燒寫)、擦除等特點,并且可由內部嵌入算法完成對芯片的操作,因而在各種嵌入式系統中得到了廣泛的應用。作為一種非易失性存儲器,Flash在系統中通常用于存放程序代碼、常量表以及一些在系統掉電后需要保存的用戶數據等。常用的Flash為8位或16位數據寬度,編程電壓為單3.3V。主要有ATMEL、AMD、HYUNDAI等生產廠商,他們生產的同型器件一般具有相同的電氣特性和封裝形式,可通用。

1.2以HY57V641620為例的SDRAM接口電路的基本特性

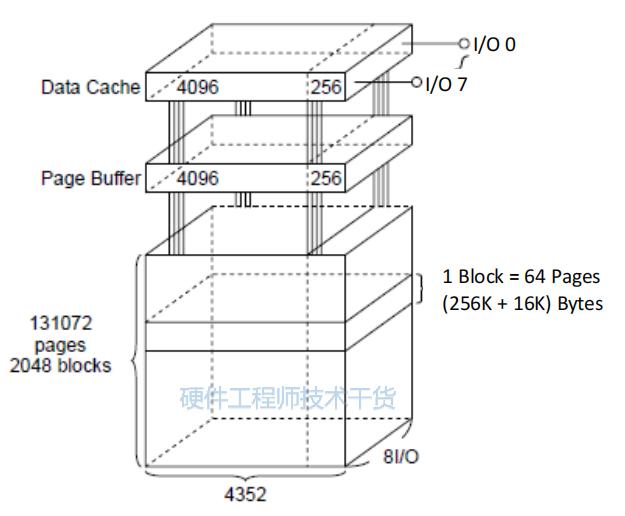

本文以Flash存儲器HY29LV160為例,簡要描述一下Flash存儲器的基本特性:

HY29LV160的單片存儲容量為16M位(2M字節),工作電壓為2.7V~3.6V,采用48腳TSOP封裝或48腳FBGA封裝,16位數據寬度,可以以8位(字節模式)或16位(字模式)數據寬度的方式工作。

HY29LV160僅需單3V電壓即可完成在系統的編程與擦除操作,通過對其內部的命令寄存器寫入標準的命令序列,可對Flash進行編程(燒寫)、整片擦除、按扇區擦除以及其它操作。

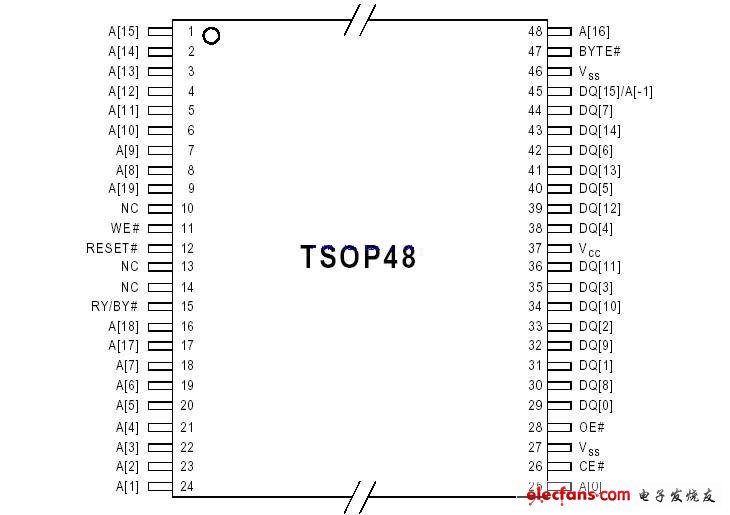

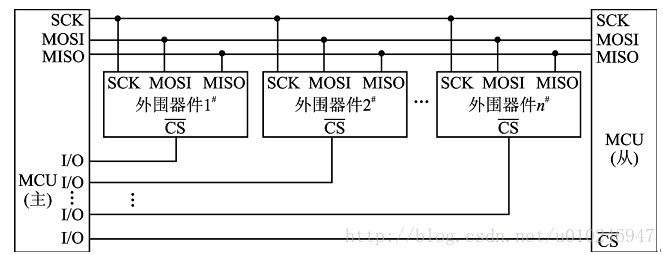

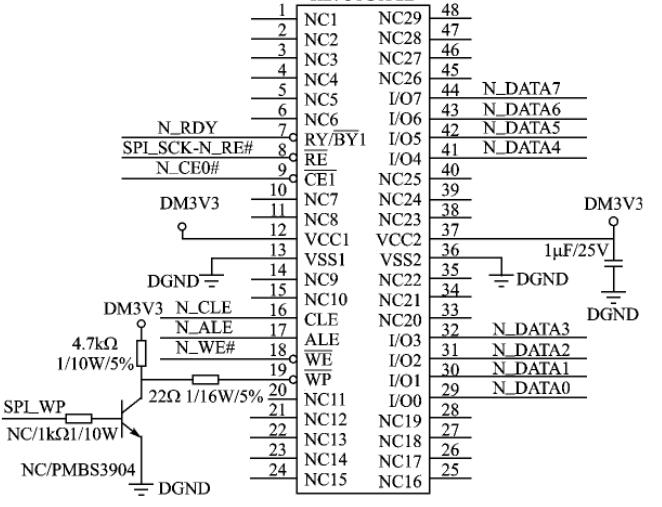

HY29LV160的邏輯框圖、引腳分布及信號描述分別如圖1和表1所示:

?

圖1 HY29LV160引腳分布(TSOP48封裝)

表1 ?HY29LV160的引腳信號描述

?

?

|

引 腳 |

類型 |

描?????? 述 |

|

A[19:0] |

I |

地址總線。在字節模式下,DQ[15]/A[-1]用作21位字節地址的最低位。 |

|

DQ[15]/A[-1] DQ[14:0] |

I/O 三態 |

數據總線。在讀寫操作時提供8位或16位數據的寬度。在字節模式下,DQ[15]/A[-1]用作21位字節地址的最低位,而DQ[14:8]處于高阻狀態。 |

|

BYTE# |

I |

模式選擇。低電平選擇字節模式,高電平選擇字模式 |

|

CE# |

I |

片選信號,低電平有效。在對HY29LV160進行讀寫操作時,該引腳必須為低電平,當為高電平時,芯片處于高阻旁路狀態 |

|

OE# |

I |

輸出使能低電平有效輸出使能,低電平有效。在讀操作時有效,寫操作時無效。 |

|

WE# |

I |

低電平有效寫使能,低電平有效。在對HY29LV160進行編程和擦除操作時,控制相應的寫命令。 |

|

RESET# |

I |

硬件復位,低電平有效。對HY29LV160進行硬件復位。當復位時,HY29LV160立即終止正在進行的操作。 |

|

RY/BY# |

O |

用就緒/忙狀態指示。用于指示寫或擦除操作是否完成。當HY29LV160正在進行編程或擦除操作時,該引腳位低電平,操作完成時為高電平,此時可讀取內部的數據。 |

|

VCC |

-- |

3.3V電源 |

|

VSS |

-- |

接地 |

?

1.3 以HY29LV160為例的Flash接口電路的使用方法

下面,我們使用HY29LV160來構建存儲系統。由于ARM微處理器的體系結構支持8位/16位/32位的存儲器系統,對應的可以構建8位、16位、32位的Flash存儲器系統。32位的存儲器系統具有較高的性能,而16位的存儲器系統則在成本及功耗方面占有優勢,而8位的存儲器系統現在已經很少使用。下面主要介紹16位和32位的Flash存儲器系統的構建。

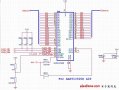

1.3.1.16位的FLASH存儲器系統

在大多數的系統中,選用一片16位的Flash存儲器芯片(常見單片容量有1 MB 、2MB 、4MB 、8MB 等)構建16位Flash的存儲系統已經足夠,在此采用一片HY29LV160構建16位的Flash存儲器系統,其存儲容量為2MB。Flash存儲器在系統中通常用于存放程序代碼,系統上電或復位后從此處獲取指令并開始執行,因此,應將存有程序代碼的Flash存儲器配置到ROM/SRAM/FLASH Bank0,即將S3C4510B的nRCS<0>(Pin75)接至HY29LV160的CE#端。

HY29LV160的RESET#端接系統復位信號;

OE#端接S3C4510B的nOE(Pin72);

WE#端S3C4510B的nWBE<0>(Pin100);

BYTE#上拉,使HY29LV160工作在字模式(16位數據寬度);

RY/BY#指示HY29LV160編程或擦除操作的工作狀態,但其工作狀態也可通過查詢片內的相關寄存器來判斷,因此可將該引腳懸空;

地址總線[A19~A0]與S3C4510B的地址總線[ADDR19~ADDR0]相連;

16位數據總線[DQ15~DQ0]與S3C4510B的低16位數據總線[XDATA15~XDATA0]相連。

注意此時應將S3C4510B的B0SIZE[1:0]置為“10”,選擇ROM/SRAM/FLASH Bank0為16位工作方式。

1.3.2. 32位的FLASH存儲器系統

作為一款32位的微處理器,為充分發揮S3C4510B的32性能優勢,有的系統也采用兩片16位數據寬度的Flash存儲器芯片并聯(或一片32位數據寬度的Flash存儲器芯片)構建32位的Flash存儲系統。其構建方式與16位的Flash存儲器系統相似。

采用兩片HY29LV16并聯的方式構建32位的FLASH存儲器系統,其中一片為高16位,另一片為低16位,將兩片HY29LV16作為一個整體配置到ROM/SRAM/FLASH Bank0,即將S3C4510B的nRCS<0>(Pin75)接至兩片HY29LV16的CE#端;

兩片HY29LV160的RESET#端接系統復位信號;

兩片HY29LV160的OE#端接S3C4510B的nOE(Pin72);

低16位片的WE#端接S3C4510B的nWBE<0>(Pin100),高16位片的WE#端接S3C4510B的nWBE<2>(Pin102);

兩片HY29LV160的BYTE#均上拉,使之均工作在字模式;

兩片HY29LV160的地址總線[A19~A0]均與S3C4510B的地址總線[ADDR19~ADDR0]相連;

低16位片的數據總線與S3C4510B的低16位數據總線[XDATA15~XDATA0]相連,高16位片的數據總線與S3C4510B的高16位數據總線[XDATA31~XDATA16]相連。

注意此時應將S3C4510B的B0SIZE[1:0]置為“11”,選擇ROM/SRAM/FLASH Bank0為32位工作方式。

2.S3C4510B系統管理器關于存儲器映射的工作原理

當系統設計制作完成時,必須經過仔細的調試,才能保證系統按照設計意圖正常工作。盡管系統的調試與個人對電路工作原理的理解和實際的電路調試經驗有很大的關系,但一定的調試方法也是必不可少的。掌握正確的調試方法可使調試工作變得容易,大大縮短系統的開發時間,反之,可能會使整個系統的開發前功盡棄,以失敗告終。

在系統的兩類存儲器中,SDRAM相對于FLASH存儲器控制信號較多,似乎調試應該困難一些,但由于SDRAM的所有刷新及控制信號均由S3C4510B片內的專門部件控制,無需用戶干預,在S3C4510B正常工作的前提下,只要連線無誤,SDRAM就應能正常工作,反之,Flash存儲器的編程、擦除操作均需要用戶編程控制,且程序還應在SDRAM中運行,因此,應先調試好SDRAM存儲器系統,再進行Flash存儲器系統的調試。

基于S3C4510B系統的最大可尋址空間為64MB,采用統一編址的方式,將系統的SDRAM、SRAM、ROM、Flash、外部I/O以及片內的特殊功能寄存器和8K一體化SRAM均映射到該地址空間。為便于使用與管理,S3C4510B又將64MB的地址空間分為若干個組,分別由相應的特殊功能寄存器進行控制:

(1) ROM/SRAM/Flash組0~ROM/SRAM/Flash組5,用于配置ROM、SRAM或Flash,分別由特殊功能寄存器ROMCON0~ROMCON5控制;

(2)DRAM/SDRAM組0~DRAM/SDRAM組3用于配置DRAM或SDRAM,分別由特殊功能寄存器DRAMCON0~DRAMCON3控制;

(3)外部I/O組0~外部I/O組3用于配置系統的其他外擴接口器件,由特殊功能寄存器REFEXTCON控制;

(4)特殊功能寄存器組用于配置S3C4510B片內特殊功能寄存器的基地址以及片內的8K一體化SRAM,由特殊功能寄存器SYSCFG控制;

在系統中,使用了Flash存儲器和SDRAM,分別配置在ROM/SRAM/FLASH組0和DRAM/SDRAM組0,暫未使用外擴接口器件。

3基于S3C4510B的嵌入式系統Flash存儲器接口電路的調試

Flash存儲器的調試主要包括Flash存儲器的編程(燒寫)和擦除,與一般的存儲器件不同,用戶只需對Flash存儲器發出相應的命令序列,Flash 存儲器通過內部嵌入的算法即可完成對芯片的操作,由于不同廠商的Flash存儲器在操作命令上可能會有一些細微的差別,Flash存儲器的編程與擦除工具一般不具有通用性,這也是為什么Flash接口電路相對較難調試的原因之一,因此,應在理解Flash存儲器編程和擦除的工作原理的情況下,根據不同型號器件對應的命令集,編寫相應的程序對其進行操作。

若使用SDT調試環境,調試過程與上述步驟相似。

>obey C:memmap.txt

打開AXD Debugger的命令行窗口,執行obey命令:

此時,2MB的Flash存儲器映射到地址空間的0x0000,0000~0x001F,FFFF處,選擇菜單Processor Views→Memory選項,出現存儲器窗口,在存儲器起始地址欄輸入Flash存儲器的映射起始地址:0x0,數據區應顯示Flash存儲器中的內容,若Flash存儲器為空,所顯示的內容應全為0xFF,否則應為已有的編程數據。雙擊其中的任一數據,輸入新的值,對應存儲單元的內容應不能被修改,此時可初步認定Flash存儲器已能被訪問,但是否能對其進行正確的編程與擦除操作,還需要編程驗證,通過程序對Flash存儲器進行編程和擦除操作。

4結束語

這樣整個基于的嵌入式系統Flash存儲器接口電路的調試基本上完成了,當然對于不同的系統,操作是略有不同的,我們可以根據所要開發或使用的嵌入式系統模式,進行適當的調整,保證我們正確的使用Flash存儲器。

電子發燒友App

電子發燒友App

評論