我有在有license生成的IP核,想移植到其它沒有license的計算機上使用,請問怎樣才能使用 是直接把xco和.v文件復制過去就可以刻么?

2013-10-25 23:58:02

[attach]74350[/attach]IP核互連策略及規范

2012-08-12 12:20:18

IP核加法器

2019-08-14 14:24:38

IP核生成文件:XilinxAlteraIP 核生成文件:(Xilinx/Altera同) IP 核生成器生成ip 后有兩個文件對我們比較有用,假設生成了一個 asyn_fifo 的核,則

2012-08-12 12:21:36

本帖最后由 eehome 于 2013-1-5 09:59 編輯

IP核簡介IP核是指:將一些在數字電路中常用但比較復雜的功能塊,如FIR濾波器、SDRAM控制器、PCI接口等等設計成可修改

2011-07-06 14:15:52

IP核簡介IP核是指:將一些在數字電路中常用但比較復雜的功能塊,如FIR濾波器、SDRAM控制器、PCI接口等等設計成可修改參數的模塊,讓其它用戶可以直接調用這些模塊,以避免重復勞動。隨著CPLD

2011-07-15 14:46:14

我想問一下,在quartus上直接調用IP核和在qsys中用IP核有什么區別?自個有點迷糊了

2017-08-07 10:09:03

我調用了一個ip核 在下載到芯片中 有一個time-limited的問題 在完成ip核破解之后 還是無法解決 但是我在Google上的找到一個解決方法就是把ip核生成的v文件加到主項目文件中就是上面

2016-05-17 10:28:47

想請教各位前輩,wishbone在工作中很常用嗎?我最近在學關于這個的代碼,感覺很難懂,而時間又感覺不大夠用,需要重點攻擊, 所以想知道是否值得投入大量的時間去研究它。望各位前輩不吝賜教

2014-03-02 23:37:04

公司現需12bit sar adc的IP核,國內有哪些公司提供相關方面的服務了?

2015-11-06 08:37:44

用Quartus II 調用IP核時,在哪可以查看IP核的例程

2014-07-27 20:28:04

Altera_IP核,僅供參考

2016-08-24 16:57:15

我用的是xinlinx spartan6 FPGA,我想知道它的IP核RAM是與FPGA獨立的,只是集成在了一起呢,還是占用了FPGA的資源來形成一個RAM?如果我以ROM的形式調用該IP核,在

2013-01-10 17:19:11

本帖最后由 jf_25420317 于 2023-11-17 11:10 編輯

FPGA開發過程中,利用各種IP核,可以快速完成功能開發,不需要花費大量時間重復造輪子。

當我們面對使用新IP核

2023-11-17 11:09:22

FSL總線IP核及其在MicroBlaze系統中的應用

2015-01-18 21:01:20

I2C的 ip核總線中保持時間hold是不是決定了SDA數據在SCL低電平的哪個時候開始變化的,保持時間hold是不是可以幾乎不用,只要建立時間setup

2015-12-07 14:34:09

本帖最后由 gk320830 于 2015-3-8 09:29 編輯

LCD的通用驅動電路IP核設計 摘 要:本文介紹了一種新型的LCD驅動電路IP核的總體設計,采用自頂向下的設計方法將其

2012-08-12 12:28:42

本人使用RS IP核進行編碼時出現IP核后面帶有美元符號,不能正常使用。求大神給予破解幫助。

2019-08-20 11:34:00

請問一下,我使用QuartusII 13.0 生成不了Rapid IO IP核,iP核已破解,其他諸如FIR、CIC、NCO等都能正常生成,到底是怎么回事呢?是Quartus版本的問題嗎?

2017-07-17 16:23:29

大家好,有沒有誰比較熟悉ALTERA公司的VIP系列ip核,我們用該系列IP核中的某些模塊(主要是scaler和interlacer)來實現高清圖像轉標清圖像(具體就是1080p50轉576i30

2015-04-13 14:12:18

發生IP核鎖定,一般是Vivado版本不同導致的,下面介紹幾種方法: 1 常用的方法 1)生成IP核的狀態報告 Report -》 Report IP Status 2)點擊

2021-01-08 17:12:52

在vivado生成ip核后缺少一大片文件,之前是可以用的,中途卸載過Modelsim,用vivado打開過ISE工程,因為工程中很多IP核不能用所以在重新生成過程中發現了這個問題,還請大神告知是怎么回事?

2023-04-24 23:42:21

altera公司IP核使用手冊,分享給想學習altera公司FPGA的IP核使用的親們~~

2013-02-16 22:40:19

在仿真fft ip核時 輸出信號一直為0,檢查了輸入波形,應該沒有問題,大家幫忙看看吧輸入是由rom里面的mif文件產生的信號。

2017-11-21 10:44:53

求用sopc builder定制IP核的步驟,是9.0的軟件,假設硬件代碼已有

2013-09-14 18:35:40

請問哪位高手有ise軟件中的各個ip核的功能介紹

2013-10-08 16:41:25

有哪位大神用過pci ip核,為什么輸入lm_req32請求,pci側沒有reqn請求輸出呢?

2016-06-27 17:56:59

本帖最后由 ys_1*****8201 于 2016-5-19 14:16 編輯

Quartus IP核破解在完成quartus軟件安裝之后,一般都要進行一個軟件破解。對于一般的需求來說

2016-05-19 14:13:09

2.5MHz 振幅0-5V 的正弦信號,請問 data 端口應該輸入怎樣的信號?如果有Altera IP核相關的詳解資料推薦下更好。多謝了。

2014-10-28 12:34:41

ip 核應用

2012-05-26 15:26:27

在quartusII中,應用fft ip核時,variable streaming 模式下的bit-reverse(位翻轉)是什么意思?煩勞詳細幫助新手解釋一下,不甚感激

2017-01-09 10:55:59

quartus的IP核,怎么用啊,有誰有這方面的資料嗎?求助 啊

2014-10-29 10:23:19

大家伙,又到了每日學習的時間了,今天咱們來聊一聊vivado 調用IP核。首先咱們來了解一下vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如

2018-05-15 12:05:13

有沒有大神可以提供xilinx FPGA的FFT IP核的調用的verilog 的參考程序,最近在學習FFT的IP核的使用,但是仿真結果有問題,所以想找些參考設計,謝謝

2016-12-25 17:05:38

通過Quartus II 軟件創建PLL IP核。首先,要新建一個工程,這個方法在之前的帖子中已經發過,不會的可以查看前面的相關帖子。創建好自己的工程:打開如下的菜單

2016-09-23 21:44:10

請問我修改完MIG IP核以后,該如何進行更新呢?搗鼓了半天,要么更新為源代碼,要么就是提示我自己添加的端口不存在

2018-11-12 19:46:15

下載了一個51的ip核,但不知道怎么用,怎么調入quartus

2014-08-08 18:22:21

剛剛接觸IP核做FFT,現在用的是FFTV9.0,已經建立了一個IP核,但是如何仿真呢?是用quartus自帶軟件,還是要用MATLAB?抑或其他?我用的自帶軟件,但是什么也沒有出來。正確的辦法應該怎樣呢,謝謝指點。

2011-04-21 10:22:31

quartus ii9.0創建的ip核,生成的一些文件,(.qip、 add_sub_bb.v、add_sub.v)這些文件都有用嗎,想在其他工程里調用這些IP核,這幾個文件全部要添加嗎?

2013-07-02 17:20:01

的《USB2.0的IP核(詳細verilog源碼和文檔).rar》。下圖是對應的Architecture。具體的文件列表如下圖所示:2、ahb轉wishbone的bridge具體項目參考百度網盤鏈接中

2022-11-23 14:47:33

核的分類和特點是什么?基于IP核的FPGA設計方法是什么?

2021-05-08 07:07:01

本文的應用背景為某一工業測控系統,該系統采用FPGA實現測量數據的采集和控制信號的輸出,通過定制PCI接口IP實現一個32位目標設備的PCI總線接口轉換。PCI核選用AlteraPCI編譯器所包括

2018-12-04 10:35:21

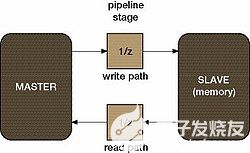

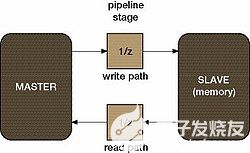

作Slave;下面的框圖代表封裝接口模塊;從Master出來并進入Slave的箭頭表示請求命令,從Slave出來并進入Master的箭頭表示響應;加黑的線段代表片上互連總線。兩個IP核通過接口通信

2019-06-11 05:00:07

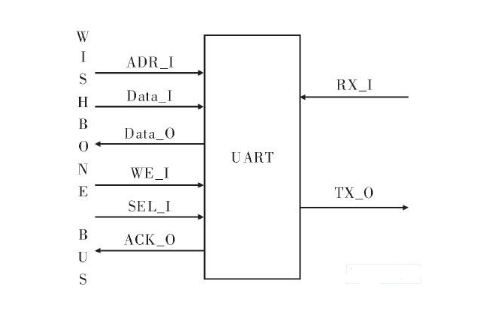

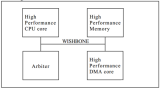

][tr][td] WISHBONE總線簡介WISHBONE總線規范是一種片上系統IP核互連體系結構。它定義了一種IP核之間公共的邏輯接口,減輕了系統組件集成的難度,提高了系統組件的可重用性、可靠性

2018-12-05 10:35:32

UART內部可劃分為哪幾個模塊?這些模塊有什么功能?基于APB總線的UART接口軟核該如何去設計?

2021-06-18 08:20:15

我畢業設計要做一個基于FPGA的IP核的DDS信號發生器,但是我不會用DDS的IP核,有沒有好人能發我一份資料如何用IP核的呀。我的瀏覽器下載不了網站上的資料,所以只能發帖求幫忙了。

2015-03-10 11:46:40

我正在嘗試將Xilinx MIG IP Core從1.7版升級到1.9版。 Coregen UI左側有一個方便的“升級IP核”按鈕,但它顯示為灰色。我需要做什么才能進行IP核升級?我在Kintex

2019-11-04 09:26:19

文章目錄一、 項目介紹:寫命令和寫數據總線介紹寫控制模塊框圖及波形代碼(1)連續寫(2)間隔部分測試代碼一、 項目介紹:本章節將會講解 A7 芯片內自帶的 DDR3 SDRAM 的 IP 核的寫時序

2022-02-08 07:08:01

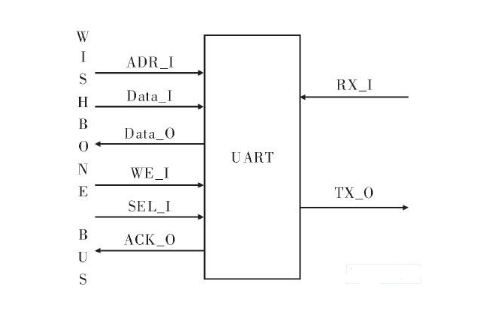

on Chip)是以嵌入式系統為核心,以IP復用技術為基礎,集軟、硬件于一體的設計方法。使用IP復用技術,將UART集成到FPGA器件上,可增加系統的可靠性,縮小PCB板面積;其次由于IP核的特點

2019-08-20 07:53:46

本文利用Altera公司的Quartus開發工具設計了一個基于Avalon總線接口的UPFC控制器IP核,以便于和NiosII組成一個完整的控制系統。

2021-04-08 06:25:12

封裝接口模塊;從Master出來并進入Slave的箭頭表示請求命令,從Slave出來并進入Master的箭頭表示響應;加黑的線段代表片上互連總線。兩個IP核通過接口通信的過程是:作為Master

2018-12-11 11:07:21

所搭的IP軟核的通訊協議與總線支持的通訊協議(ICB)不同怎么轉換?

2023-08-17 07:05:35

經過努力,開源軟核處理器OpenMIPS的實踐版終于新鮮出爐了,相對OpenMIPS教學版而言,OpenMIPS實踐版最大的特點是引入了Wishbone總線接口,組建了SOPC,包括SDRAM控制器

2014-01-06 17:41:21

的是0x00。使用asmi_parallel2 ip核用avalon總線也不能順利讀取,想請教一下,我是讀寫的時序,還是因為自動分配的引腳存在問題?

2018-06-29 21:01:21

本人FPGA小白一枚,最近使用到FPGA的IP核遇到一個問題。比如說:某個IP,用于計算sin函數,使用了流水線機制,所有從輸入到輸出需要20個時鐘周期的延時。另外,還有一個IP,從輸入到輸出需要1

2021-06-19 11:06:07

請問Altera RAM IP核怎么使用?

2022-01-18 06:59:33

這是我們一個小比賽的題面:設計一個簡易的電子計算器電路,包括輸入數據處理電路,算數運算電路(包含加法、減法、乘法、除法等算數運算),運算結果處理電路,所有運算電路的設計均不可使用IP核及查找表進行

2018-04-06 20:46:11

三個問題:Linflexd_Uart_Ip_AsyncReceive 函數被阻塞(與接口的異步特性不一致)。測試的串口數據接收接口為Uart_AsyncReceive,調用了Linflexd_Uart_Ip

2023-03-21 07:20:15

一個基于Avalon總線接口的UPFC控制器IP核,以便于和NiosII組成一個完整的控制系統。1 UPFC控制器IP的主要功能UPFC控制器的IP主要用來輸出3路相位分別相差2π/3的正弦波

2019-06-03 05:00:05

電平,控制總線暫停。 當主節點要求總線暫停時亦可采用同樣的方法。圖1是CPLD向外圍I2C器件發送01010011 和01001001這兩個數據的情況。 3 在MaxplusII環境下I2C串行擴展IP核

2019-04-12 07:00:09

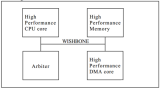

介紹了基于IP 的可重用的SOC 設計方法;選用MC8051 IP 核為核心控制器,自主開發了UART IP 核、I2C IP 核、USB IP 核,采用Wishbone 片上總線架構,集成了一個MCU 系統;同時設計了針對此MCU

2009-11-30 15:06:20 33

33 以 FPGA 技術為基礎,以Verilog HDL 為載體,設計了遵守Wishbone 片上總線規范的IP 核接口,實現了片上系統的IP 核互聯。

2010-01-13 15:09:14 13

13 摘要:基于IP可重用的設計方法,利用WISHBONE總線協議,把兩個已成功開發出的具有自主知識產權的THUMP內核在一個芯片上,實現了片上多處理器FPGA。開發重點是實

2009-06-20 15:29:35 656

656

本文簡要介紹了AMD 公司Am29LV160D 芯片的特點,并對WISHBONE總線作了簡單的介紹,詳細說明了FLASH memory 與WISHBONE 總線的硬件接口設計及部分Verilog HDL 程序源代碼。

2011-06-23 16:32:40 18

18 通用IO接口是Soc系統中非常重要的一種外圍端口.本文完成了一種基于WISHBONE總線的GPIO_W B拉制器的邏拜設計和物理實現.文中較其體地介紹了GPIO_W B核的體系結構以及WISHBONE接Q和DMA傳偷方式

2011-09-21 16:57:22 32

32 該設計采用了自頂向下的模塊化劃分和有限狀態機相結合的方法,由于其應用了標準的Wishbone總線接口,從而使微機系統與串行設備之間的通信更加靈活方便。驗證結果表明,這種新的架構

2011-10-19 15:01:54 27

27 介紹了基于硬件描述語言Verilog HDL設計的SDX總線與Wishbone總線接口轉化的設計與實現,并通過Modelsim進行功能仿真,在QuartusⅡ軟件平臺上綜合,最終在Altera公司的CycloneⅢ系列FPGA上調試。實驗

2012-01-11 10:21:21 25

25 本文以UART IP核和PLB總線為例,討論了在SoPC系統下UART IP核的設計方法,該方法對其他IP核的設計有一定的參考作用。

2013-01-08 09:03:27 4429

4429

基于AMBA與WISHBONE的SoC總線橋KBar控制器的設計_陳俊銳

2017-03-19 11:31:31 0

0 支持用戶定義的標簽。這些標簽可以用于為地址、數據總線提供額外的信息如奇偶校驗,為總線周期提供額外的信息如中斷向量、緩存控制操作的類型等。Wishbone規范只定義標簽的時序,而標簽的具體含義用戶可自行定義。支持用戶定義的標簽是Wishbone規范區別與其他片上總線規范的重要特征之一;

2018-07-06 08:07:31 2713

2713

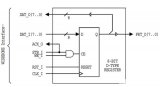

前文曾經指出,Wishbone總線規范是"輕量級(Lightweight)"規范,它實現起來非常簡單緊湊,接口需要的互聯邏輯非常少。這里給出一個Wishbone從設備的一個例子,如圖21所示

2018-07-31 09:11:30 4148

4148

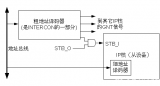

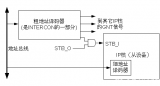

Wishbone部分地址譯碼的實現如圖26所示。對于圖中所示IP核,我們假設其只有4個地址,對應4組寄存器。地址譯碼器首先譯碼出其地址并給出選擇信號,該選擇信號與共享總線的STB_O相與輸入到IP核的STB_I。而地址總線的最低2位被直接連接到IP核,IP核再根據這兩位譯碼出當前操作選中的是具體哪個寄存器。

2018-08-05 08:44:59 3421

3421

在以上介紹的三種總線中,CoreConnect雖免費不過需要IBM 公司許可,ARM 沒有明確的正式說法,可能也會免費,而Wishbone 是絕對免費的。三種總線都是同步的總線,使用時鐘上升沿驅圖7 8-bit SLAVE輸出端口動和采樣信號。

2018-08-11 09:14:22 4391

4391

用于便攜式IP核的WISHBONE1片上系統(SoC)互連結構是一種靈活的設計方法,可用于半導體IP核。其目的是通過緩解片上系統集成問題來促進設計重用。這是通過在IP核之間創建一個公共接口來實現的。這提高了系統的可移植性和可靠性,并縮短了最終用戶的上市時間。

2021-01-19 15:23:59 21

21 Gowin UART Master IP 和 Slave 參考設計用戶指南主要包括功能簡介、

信號定義、工作原理、GUI 調用等,旨在幫助用戶快速了解 Gowin UART

Master IP 和 Slave 參考設計的特性及使用方法。

2022-09-15 10:11:24 0

0 電子發燒友網站提供《Gowin I2C UART IP用戶指南.pdf》資料免費下載

2022-09-16 14:29:01 10

10 電子發燒友網站提供《Gowin SDIO UART IP用戶指南.pdf》資料免費下載

2022-09-16 14:27:25 0

0 Wishbone B.3總線。以類似的方式,Altera引入了自己的互連方案,稱為Avalon Bus,SOPC Builder和Nios(II)系統就是圍繞該方案制造的。Xilinx 還推出了自己的總線,稱為片上外設總線與處理器本地總線 相結合。

2022-11-14 15:38:55 790

790

LogiCORE IP AXI 通用異步接收發送器 (UART) 16550 連接到高級微控制器總線架構 (AMBA) AXI,為異步串行數據傳輸提供控制器接口。該軟 IP 核旨在通過 AXI4-Lite 接口進行連接。

2023-10-16 11:02:01 1762

1762

電子發燒友App

電子發燒友App

評論