像485 232 還有can這種線需不需要使用差分布線規(guī)則

2019-06-17 15:23:18

新手,正在設(shè)計6678與V7用RapidIO 4X模式通信的硬件電路,與FPGA連接的4對收、4對發(fā)差分對信號線要分別做等長設(shè)計嗎?????

2018-08-03 06:57:16

`各位大神,如下圖片的以太網(wǎng)布線的原因,要求,作用。`

2017-03-02 16:51:39

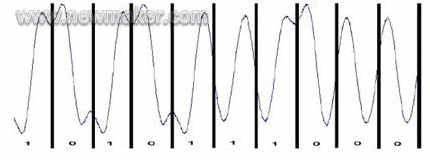

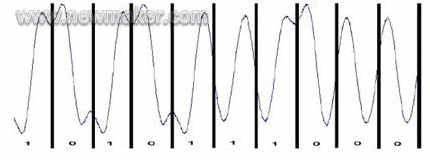

。 2. 以太網(wǎng)的信號線是以差分對(Rx±、Tx±)的形式存在,差分線具有很強共模抑制能力,抗干擾能力強,但是如果布線不當(dāng),將會帶來嚴(yán)重的信號完整性問題。下面我們來一一介紹差分線的處理要點: a

2018-09-19 16:24:17

以太網(wǎng)的接口信號,在PCB走線的時候,差分可以不等長么?如果要等長,誤差是多少?

2023-04-07 17:38:17

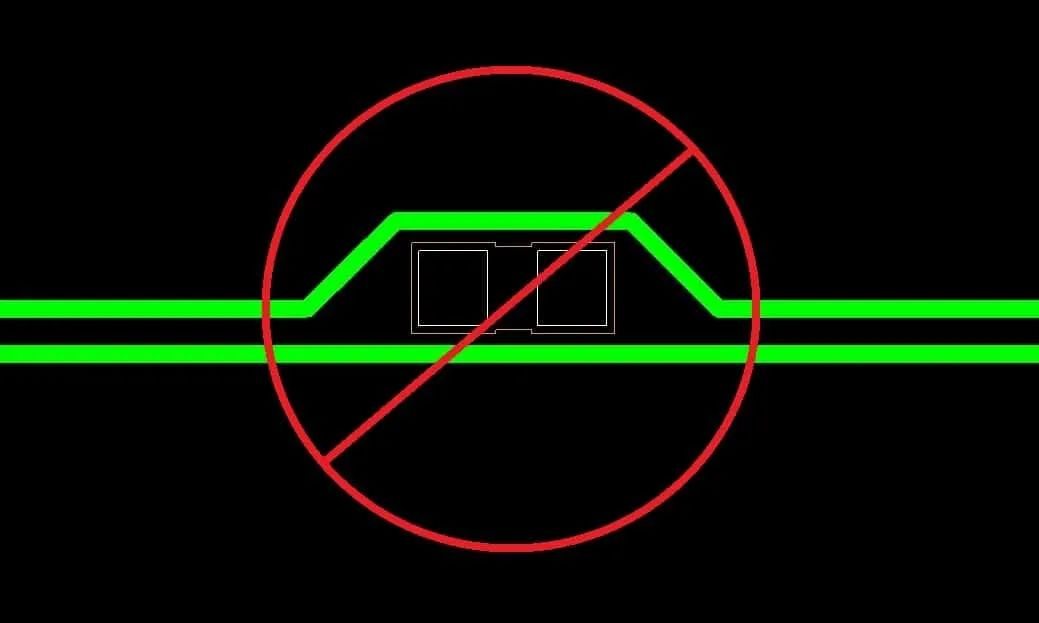

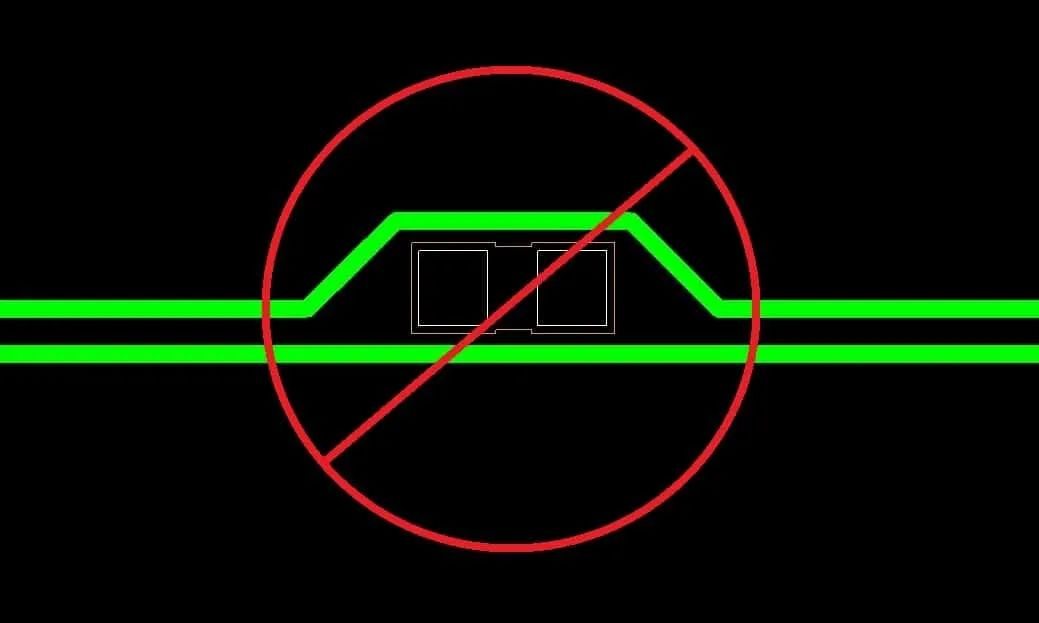

差分對布線時交叉的方法打孔靠譜嗎?這兩種畫法哪個比較好呢?還是另有其他更好的方法呢?謝謝。。。

2014-06-16 17:20:31

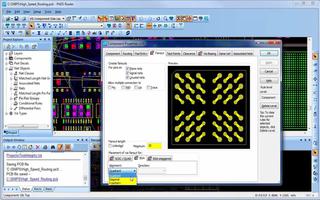

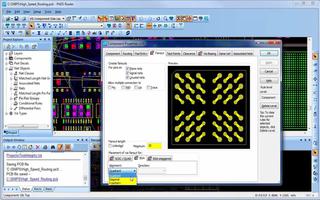

在Layout cross-section中設(shè)置正在使用的差分對的差分阻抗為100歐,打開D:\diffPair\PCI2.brd。

2019-06-03 07:31:57

我PCB已經(jīng)分配了器件模型 但是由于布線不好走進行了原理圖信號調(diào)整 再從網(wǎng)絡(luò)表導(dǎo)入進來 發(fā)現(xiàn)我原來設(shè)置的差分對約束有些亂了 不是配對信號 怎么回事?

2015-02-03 10:26:08

差分對線距規(guī)則設(shè)置為6mil,是不是因為在clearance中設(shè)置最小間隔為10mil就會報錯,該怎么解決?一般的差分對線寬,間距都設(shè)置多少基本滿足一般需求?

2019-05-21 05:35:24

ad 21 我有百多對差分線過孔 我改了過孔間距規(guī)則 需要重新調(diào)整差分對過孔 但是太多了 調(diào)整太慢了 有沒有簡單的方式一次調(diào)很多個

2022-05-18 20:06:54

彼此的點,即交越點。因此,信號須同時到達接收器才能正常工作。2、差分對內(nèi)的走線布線須彼此靠近如果一對中的相鄰線路之間的距離大于電介質(zhì)厚度的2倍,則其間的耦合會很小。此規(guī)則也是基于差分信號相等但相反這一

2018-08-18 06:20:23

我的AD9446的工作在LVDS模式下,請問對于AD9446(100MHz),LVDS信號線的PCB走線的差分對間等長有沒有要求?(PS:16對差分線,都做等長好復(fù)雜)謝謝!

2023-12-18 06:26:51

請問,pcb中已經(jīng)布完差分對后,發(fā)現(xiàn)有部分差分對需要調(diào)整線寬和線間距,現(xiàn)在只知道修改RULES,然后重新走一遍布線,相當(dāng)于重新布線了,量大很麻煩。有沒有便捷的方法呢?

2016-08-03 14:50:36

我看別人的板子差分對走線之間的過孔距離很寬,而我的這個差分對走線過孔離得很近,這個之間的規(guī)則是怎么設(shè)置的啊?沒找到呢,。。

2018-08-13 10:42:05

Altium Designer 蛇行 等長 布線 技巧一. 設(shè)置需要等長的網(wǎng)絡(luò)組點擊主菜單 Design-->Classes,在彈出的窗口中單擊 Net Classes,并右鍵,點 Add

2013-01-12 15:18:43

本帖最后由 xiaokangkp 于 2013-12-22 14:49 編輯

講解蛇行等長布線的具體操作步驟 順便分享一下不同走線的區(qū)別

2013-12-22 14:42:32

AltiumDesigner等長布線操作 我為大家介紹 等長布線,”等長走線“簡單的理解就是讓指定網(wǎng)絡(luò)的走線”長度“一樣。等長走線的主要目的是為了補償同一組時序相關(guān)的信號線中延時較小的走線,盡量減小

2018-03-09 09:54:43

Altium+Designer6+蛇行等長布線

2012-08-20 23:54:42

Bus總線布線時如何做到等長?

2021-04-26 06:57:47

PCB布線中,有著許多需要注意的點,比如:1.高頻時鐘線需要蛇形走線2.有些信號線需要設(shè)置差分對,差分走線

2019-05-31 06:23:05

manager約束管理器。比如我們常見的電氣規(guī)則,物理規(guī)則,差分對規(guī)則,拓?fù)?b class="flag-6" style="color: red">規(guī)則等都可以在原理圖添加完成,接下來詳細(xì)敘述添加約束規(guī)則過程。(2)開啟OrCAD Caputre軟件的時候需要選擇PCB

2020-07-06 15:00:43

DDR-Topology DDR布線通常是一款硬件產(chǎn)品設(shè)計中的一個重要的環(huán)節(jié),也正是因為其重要性,網(wǎng)絡(luò)上也有大把的人在探討DDR布線規(guī)則,有很多同行故弄玄虛,把DDR布線說得很難,我在這里要

2019-05-31 07:52:36

等長是PCB設(shè)計的時候經(jīng)常遇到的問題。存儲芯片總線要等長,差分信號要等長。什么時候需要做等長,等長約束條件是什么呢?首先,等長的作用。由于信號在PCB走線上存在延時,正比于信號線的長度。假設(shè)PCB

2014-12-01 11:00:33

漏線2、信號線是否有優(yōu)化好,間距規(guī)則有沒有設(shè)并已清完相關(guān)DRC3、DDR布線是否滿足要求,如同組走同層,線寬是否正確4、繞線時需要注意你所做的部分對周邊布局布線是否造成影響5、是否明確繞線規(guī)則,如幾倍

2017-10-16 15:30:56

的線寬間距,并設(shè)置到約束管理器。 差分線通過互相耦合來減少共模干擾,在條件許可的情況下要盡可能平行布線,兩根線中線不能有過孔或其他信號。 差分對需要嚴(yán)格控制相位,所以對內(nèi)需要嚴(yán)格控制等長。 為減少

2023-04-12 15:08:27

請教PCIEx8布線問題: 8個Lane之間的差分對與差分對需要等長嗎(即Lane0~lane7的所有TX等長,所有RX等長)?還是只需保證每對差分線等長即可?

2016-10-19 17:46:54

為何我選擇差分對右擊選擇特性過后,卻沒有彈出差分對特性,反而是設(shè)計特性,這是什么情況,怎么調(diào)成差分對特性?如圖

2016-12-19 19:29:38

自己總結(jié)下差分對規(guī)則的設(shè)置

2016-03-01 01:48:30

現(xiàn)在學(xué)習(xí)cadence,PCB布線時,感覺命令不聽使喚,總是繞的亂不七八糟,但是取消差分對采單個模式又擔(dān)心達不到效果,求有經(jīng)驗的前輩說說看

2015-12-28 22:38:54

本帖最后由 cooldog123pp 于 2019-8-10 22:49 編輯

設(shè)置差分對,有好幾種方法,下面我就來一一介紹方法一:原理圖中直接設(shè)置好,然后導(dǎo)入到PCB中,如圖,給要設(shè)置的差

2016-09-27 09:19:50

工業(yè)現(xiàn)場的環(huán)境比普通環(huán)境都要惡劣,至少在震動,濕氣,溫度上都要比普通環(huán)境惡劣,工業(yè)以太網(wǎng)需要更多專業(yè)的知識和實踐經(jīng)驗。如果你正在安裝或者使用一種工業(yè)以太網(wǎng)(工業(yè)以太網(wǎng)交換機),那么關(guān)于布線、信號質(zhì)量

2016-12-01 21:43:36

工業(yè)現(xiàn)場的環(huán)境比普通環(huán)境都要惡劣,至少在震動,濕氣,溫度上都要比普通環(huán)境惡劣,工業(yè)以太網(wǎng)需要更多專業(yè)的知識和實踐經(jīng)驗。如果你正在安裝或者使用一種工業(yè)以太網(wǎng)(工業(yè)以太網(wǎng)交換機),那么關(guān)于布線、信號質(zhì)量

2016-12-06 21:29:49

新人,第一次用allegro,在pcb editor里布線,設(shè)置了差分對規(guī)則,返回布線的時候,選中差分對其中的一個引腳布線,但是只拉出來了一根線,右鍵里也沒有單根走線模式可選。求解。。。。。。

2015-04-15 17:38:54

為何差分對的布線要靠近且平行?

2009-09-06 08:42:55

畫千兆以太網(wǎng)接口,有4組差分對,每對靜態(tài)相位誤差設(shè)置的是5mil;同時這幾組差分對相互之間有等長約束。粗略的連好之后準(zhǔn)備繞線,現(xiàn)有如下問題:1.如何繞線使靜態(tài)相位誤差符合要求?目前我使用Delay

2017-12-08 21:08:13

`1.我依照別人的約束管理器設(shè)置,像下圖這樣,對4對差分對進行了等長設(shè)置但是這里并沒有指定以誰為target,這樣沒問題嗎?2.看到有的約束管理器在這里設(shè)置的容差單位是ns而不是mil。這里我選

2017-11-29 11:04:52

剛學(xué)ALLEGRO,一直搞不懂差分對設(shè)置等長跟阻抗匹配的關(guān)系,不知附圖那樣設(shè)置對不對,求指點

2014-11-30 22:41:22

絡(luò)是兩條存在耦合的傳輸線,一條攜帶信號,另一條則攜帶它的互補信號。使用差分對布線前要對設(shè)定差分對網(wǎng)絡(luò)進行設(shè)置。設(shè)置可以在原理圖中設(shè)置,也可以在PCB中進行設(shè)置。a 原理圖中添加差分對規(guī)則: 在命名差分對

2016-10-12 23:05:44

(Rename Class),加入需要的Net。2.在Design-Rules中,High Speed中新建一個匹配等長規(guī)則(MatchedLengths),為其命名,選擇Net Class,修改容差

2018-03-13 10:59:31

,必須匹配其MOSFET。這意味著兩個MOSFET的通道尺寸必須相同,并且布線應(yīng)該是平衡的。差分對左右兩邊的寄生效應(yīng)的任何差異都會降低其性能。我們可以使用傳統(tǒng)的原理圖編輯器和Pulsic提供的插件輕松

2023-02-02 17:22:49

本帖最后由 一只耳朵怪 于 2018-6-25 14:19 編輯

1、在對6678中SRIO進行PCB布線時遇到一個疑問。若需要使用SRIO 4X模式時,PCB布線是否有必要對4組TX和RX差分信號分別進行等長處理?2、若不進行等長處理,4組差分信號的相位差應(yīng)該控制在多少范圍內(nèi)?

2018-06-25 04:40:30

對于差分對有哪些要求?如何去設(shè)計差分對?

2021-05-20 06:15:42

一、差分對內(nèi)兩信號的走線長度相等該要求是基于以下兩個因素而提出的。(1) 時序要求:由于差分信號的時需參考點是對內(nèi)兩信號邊沿的交叉點,差分對內(nèi)兩信號走線長度的差異會造成交叉點的偏移,可能

2023-03-16 11:24:22

,必須匹配其MOSFET。這意味著兩個MOSFET的通道尺寸必須相同,并且布線應(yīng)該是平衡的。差分對左右兩邊的寄生效應(yīng)的任何差異都會降低其性能。我們可以使用傳統(tǒng)的原理圖編輯器和Pulsic提供的插件輕松

2023-02-15 13:43:37

連上這些飛線即可。當(dāng)然走線之前肯定需要對差分對賦予規(guī)則約束的。打開約束管理器,點擊差分對約束(如下圖)在對應(yīng)線寬間距處填入相應(yīng)的數(shù)值即可。當(dāng)然,根據(jù)層疊的厚度和阻抗值得不同,填入的數(shù)值肯定不一樣,內(nèi)外

2018-01-12 17:09:48

上述要求,A線路和B線路應(yīng)該在它們的物理布局布線中保持高對稱。發(fā)射器和接收器也應(yīng)該在它們的A和B線路電路中保持高對稱,這樣的話,它們在A線路和B線路上的電氣負(fù)載相等。設(shè)計差分對,以最大限度地減少失真

2018-09-11 11:50:09

集成10/100/1000千兆以太網(wǎng)收發(fā)器RTL8211E,RTL8211EG為了達到布線優(yōu)化,需要注意以下事項。①首先是各個元器件之間的距離。PHY離開MAC的距離最好不要不超過2.5

2016-04-07 14:10:35

請大神指點一下以太網(wǎng)知識!如何布線更好!中間沒有變壓器,RJ45直接到主芯片!一個網(wǎng)口作為輸入,一個網(wǎng)口作為輸出!1、以太網(wǎng)口RJ45的TX+ TX- RX+ RX-布線到主芯片上,是否要走線差分對?2、差分對是否需要等長。3、RJ45的TX+ TX- RX+ RX-周邊是否要鋪地。

2019-12-18 11:21:13

請教各位大神, allegro 差分對與差分對之間的間距如何設(shè)置?謝謝! 版本16.6。我在網(wǎng)上看到可以在class to class中設(shè)置,嘗試后發(fā)現(xiàn)需要為每一對差分對設(shè)置一個NetClass屬性

2017-02-24 14:21:34

:比如說AD1_PAD1_N與AD2_PAD2_N這兩對之間的差距小于150mil?還是還是一對差分線中的P線和N線的相差長度小于150mil? 問題2:我在PCB布線上遇到了難題,不知道要保證每對等長需要

2019-01-04 10:00:40

請問ADS5474在PCB布線時,數(shù)據(jù)輸出和時鐘輸出共16對差分線需不需要保持等長,如果要的話誤差可以控制在多少個mil?

2019-03-04 07:31:34

HDMI差分對PCB怎么走線?要計算匹配阻抗嗎?差分對走多長有要求嗎?四對差分對要走一樣長嗎?

2019-05-31 05:35:21

的將來,隨著對差分對原理和設(shè)計規(guī)則的了解加深,將會有超過90%的電路板使用它 歡迎轉(zhuǎn)載,信息維庫電子市場網(wǎng)(www.dzsc.com):

2018-11-27 10:56:15

一系列阻抗問題。 高速設(shè)計的另一個關(guān)鍵領(lǐng)域是差分對的布線。差分對通過以互補的方式驅(qū)動兩個信號跡線來操作。差分對提供出色的抗噪聲能力和更高的S / N比。然而,實現(xiàn)這些優(yōu)勢有兩個限制: 1、兩條走線

2023-04-12 15:20:37

布線技巧四:10Base—T/2/5/F/35—以太網(wǎng)

90年代早期到中期,當(dāng)100 Mbps 網(wǎng)卡和集線器/交換機非常昂貴時,10Base-T UTP以太網(wǎng)和10Base-2 Coax以太網(wǎng)受

2009-04-23 17:54:03 6441

6441 Bus/總線布線時如何做到等長

Bus走線模式是在13.6版本中可以實現(xiàn)的模式,現(xiàn)在14.x以及15.0都已

2009-09-28 12:45:58 1580

1580 以太網(wǎng)相較工業(yè)以太網(wǎng)有以下四大缺陷,要使以太網(wǎng)符合工藝上的要求,還必須克服這4大缺陷

2011-12-12 15:16:59 3687

3687 AD_等長線布線方法與查看方式,詳細(xì)軟件操作

2015-12-11 17:00:06 0

0 pcb布線設(shè)計規(guī)則.pdf,pcb布線設(shè)計規(guī)則.pdf

2015-12-28 11:31:11 0

0 Altium-Designer-蛇形等長布線和如何查看NET總長度,感興趣的可以看看。

2016-07-22 16:18:06 0

0 蛇行等長線布線方法

2017-10-13 09:45:38 7

7 Altium_Designer6_蛇行等長布線

2017-10-18 14:25:17 15

15 Altium Designer6蛇行等長布線

2017-11-01 11:04:18 14

14 的Net。 2.在Design-Rules中,High Speed中新建一個匹配等長規(guī)則(MatchedLengths),為其命名,選擇Net Class,修改容差(Tolerance=100mil),匹配

2018-05-22 10:45:56 17737

17737 10G以太網(wǎng)在數(shù)據(jù)中心的迅速普及使得10G綜合布線設(shè)備備受關(guān)注,在進行布線系統(tǒng)搭建時,可選擇光纖系統(tǒng)與銅纜系統(tǒng),對于中小企業(yè)來說,萬兆銅纜布線具有明顯的優(yōu)勢,設(shè)備端口成本低,設(shè)備安裝方便,維護簡單,且能夠滿足基本的傳輸特性與距離需求,因此成為了眾多數(shù)據(jù)中心布線的首選。

2018-07-13 14:29:00 3373

3373 PADS 為高速網(wǎng)絡(luò)布線提供了一個可擴展的環(huán)境,在該環(huán)境中可進行交互和自動兩種模式。高速網(wǎng)絡(luò)的規(guī)則,例如匹配長度、差分對等,非常容易設(shè)置。在布線過程中,您將得到針對關(guān)鍵和敏感網(wǎng)絡(luò)的實時布線長度反饋。PADS 高速布線可成為提高您 PCB 設(shè)計生產(chǎn)率的“利器”。

2019-05-14 06:02:00 3230

3230

本文首先介紹了以太網(wǎng)的概念,其次介紹了以太網(wǎng)連接寬帶的方法,最后闡述了以太網(wǎng)與寬帶區(qū)別。

2020-03-20 10:02:09 82143

82143

現(xiàn)實生活中,以太網(wǎng)可謂無處不在,而對它進行測試與分析也是通信領(lǐng)域經(jīng)久不衰的話題。要想透徹掌握以太網(wǎng)測試要領(lǐng),必須首先了解以太網(wǎng)物理層信號的基本特點。基于此,本文將具體介紹三種速率以太網(wǎng)標(biāo)準(zhǔn)的不同物理層編碼規(guī)則、完整測試涉及到的共性問題,以及基于力科示波器的以太網(wǎng)一致性測試方案。

2021-06-24 17:00:02 9509

9509

POE (Power Over Ethernet)指的是在現(xiàn)有的以太網(wǎng)布線基礎(chǔ)架構(gòu)不作任何改動的情況下,在為一些基于IP的終端(如IP電話機、無線局域網(wǎng)接入點AP、網(wǎng)絡(luò)攝像機等)傳輸數(shù)據(jù)信號的同時

2022-01-06 16:01:18 15

15 我們現(xiàn)今使用的網(wǎng)絡(luò)接口均為以太網(wǎng)接口,目前大部分處理器都支持以太網(wǎng)口。目前以太網(wǎng)按照速率主要包括10M、10/100M、1000M三種接口,10M應(yīng)用已經(jīng)很少,基本為10/100M所代替。目前

2022-02-11 17:14:21 56

56 本文解釋并比較了兩種類型的以太網(wǎng):快速以太網(wǎng)與千兆以太網(wǎng)。快速以太網(wǎng)和千兆以太網(wǎng)之間的最大區(qū)別在于速度。

2022-05-06 16:35:23 3678

3678

在密集配線的空間里,細(xì)型線纜可以促進空氣的流通,節(jié)省布線空間,讓整個布線的環(huán)境更為有序。為了進一步滿足客戶以太網(wǎng)布線的多元需求,L-com諾通推出了一系列新型超細(xì)6類以太網(wǎng)線纜組件。

2022-10-28 15:08:18 721

721 不過,差分對布線可能沒那么容易,因為它們必須遵循特定的規(guī)則,這樣才能確保信號的性能。這些規(guī)則決定了一些細(xì)節(jié),如差分對的走線寬度和間距,以及許多其他方面,如導(dǎo)線如何在電路板上一起布線。

2022-12-30 14:09:12 3474

3474 以太網(wǎng),特別是工業(yè)以太網(wǎng)最近變得流行起來 制造業(yè)的行業(yè)術(shù)語。雖然相似,但它們都提供不同的 特點和好處。本文將探討哪些以太網(wǎng) 和工業(yè)以太網(wǎng)是以及它們有何不同。

2023-01-03 14:16:31 1208

1208 :較之單一的走線,差分對布線更受青睞。不過,差分對布線可能沒那么容易,因為它們必須遵循特定的規(guī)則,這樣才能確保信號的性能。這些規(guī)則決定了一些細(xì)節(jié),如差分對的走線寬度和

2022-12-05 11:06:06 881

881

部署以太網(wǎng)布線是網(wǎng)絡(luò)的核心組件,是可靠、高速數(shù)據(jù)傳輸?shù)墓歉伞Ec無線相比,利用以太網(wǎng)具有重要的優(yōu)勢,例如減少延遲、提高安全性和整體穩(wěn)定性。

2023-09-24 10:37:33 582

582 高效差分對布線指南:提高 PCB 布線速度

2023-11-29 16:00:52 690

690

為何差分對的布線要靠近且平行? 差分對是一種電路設(shè)計中常見的布線方式,它的作用是減小信號傳輸?shù)母蓴_和噪音。差分信號傳輸是指將信號分解成兩個相等幅值、相位相反的信號,通過同時傳輸這兩個信號來進行

2023-11-24 14:38:13 334

334

電子發(fā)燒友App

電子發(fā)燒友App

評論