本文主要介紹以太網Drive Side接口(MAC和PHY之間的接口),也被稱為MII(Media Independent Interface),支持從10M到100G的不同應用場合,主要包括MII

2020-10-08 00:09:00 8774

8774

DP83822 是一款低功耗單端口10/100Mbps以太網PHY。它提供通過標準雙絞線電纜發送和接收數據或者連接到外部光纖收發器所需的所有物理層功能。

2021-03-13 12:17:44 11270

11270

千兆以太網轉換PORT口,集成了2個10/100/1000Mbps三重速率的以太網發送器(PHY),1個(G)MII接口,3個SERDES接口用來連接外部...

2021-07-28 08:05:14

MII接口.png (39.24 KB, 下載次數: 0)下載附件1 小時前 上傳MII (Media Independent Interface(介質無關接口);或稱為媒體獨立接口,它是

2018-05-12 12:50:21

MII接口有何功能?RMII接口有何功能?MII接口和RMII接口對應的引腳有哪些?

2021-10-26 06:12:11

MII支持10兆和100兆的操作,一個接口由14根線組成,它的支持還是比較靈活的,但是有一個缺點是因為它一個端口用的信號線太多,如果一個8端口的交換機要用到112根線,16端口就要用到224根線,到

2019-10-18 09:11:36

開發板使用MII接口,但是由于我們要使用串口,所以LAN8720接到6748的RMII接口。那么問題來了,開發板中初始化EMAC_initialize()函數內使用EMACPinMuxSetup

2019-08-27 11:12:07

,G.723.1,G.729A,G.729B),回音消除及多種普通電話技術。CM5000提供2個10/100M快速以太網地址支持全/半雙工模式,端口基于VLAN,MII接口和2K字節的FIFO封包緩存

2008-06-07 12:12:33

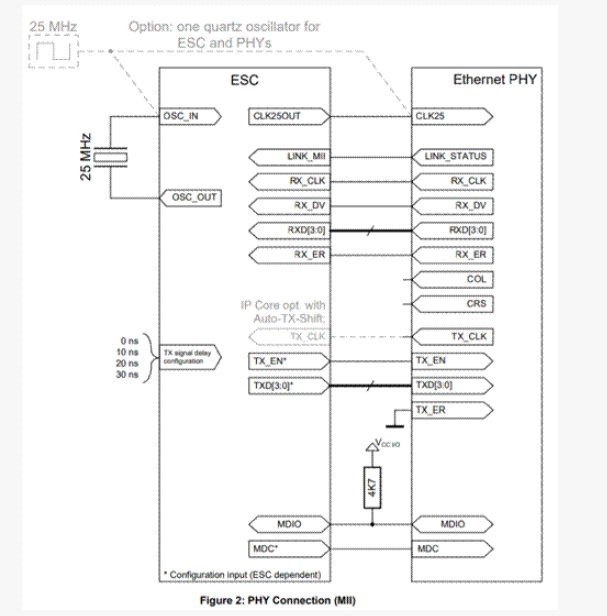

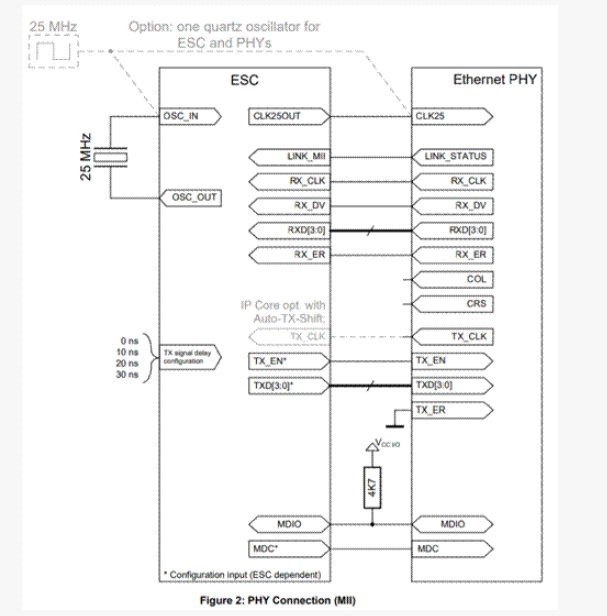

Controller,ESC)和物理層接口PHY實現EtherCAT的應用。ESC通常會支持PHY使用MII,RMII和RGMII接口,由于RMII和RGMII接口包含TX FIFO,會增加EtherCAT從站

2022-11-07 07:55:18

) eth_example: Ethernet Started可以看到,網速協商失敗。1)RTL8201F默認是MII接口,根據官方手冊PDF說將第8腳RXDV通過4.7K電阻上拉到3.3V,這樣芯片

2023-03-13 08:38:57

TI的工程師,你們好,由于用F28M35H52C1的MII接口外擴以太網占去了將近20個pin,我們的IO資源比較緊張,于是將注意力集中在了 datasheet 第六章 boot 啟動引腳GPIO35 47 43上,除了這幾個引腳配置從FLASH等啟動,還有其他方式可以配置嗎?

2020-05-07 09:32:54

100BASE-FX。這些設備專為成本敏感型系統而設計,但仍提供多種功能,如交換機管理,基于端口和標簽的VLAN,QoS優先級,一個MII接口以及CPU控制和數據接口。 KSZ8873MLL是VoIP電話,機頂盒/游戲盒,SOHO住宅網關,工業以太網系統以及獨立3端***換機的絕佳選擇

2020-05-15 06:16:58

可以直接進行數據傳輸。與串口或SPI接口的以太網模塊相比,這可以極大的提升數據傳輸帶寬。MAC控制器通過MII或RMII接口與外部PHY芯片連接,然后轉換成RJ45可以連接到主機或路由器。MII接口模式

2022-12-01 15:34:15

我們用Sc573來設計一個音頻攪拌器產品, 希望使用 DP83848 phy( MII 接口), 并且這些電源比 DP83865 便宜, 但現在這個Ethernet 失敗了。 或者 ADI 可以向我們建議低價的PHY芯片?

感謝 謝謝

2023-11-29 07:11:26

不到DSP發送的數據包,用示波器觀察DSP與PHY之間的MII接口信號,均正常,TXEN,TXCLK,TXD[3:0]等數據線上,波形均無異常,但是PC端就是接收不到數據包,請問這是什么問題?能否給點建議?謝謝

2020-05-22 08:51:57

我將 RT1061 與第二個網絡接口 (ENET2) 一起使用。Ethernet-Phy(KSZ8863MLL)通過 MII 接口連接。

不幸的是,在打開電源后并不總是建立網絡連接。

使用 DHCP 演示,在網絡上的錯誤狀態下看不到發送報文(DHCP 發現)。

此配置是否存在任何已知問題?

2023-05-05 14:24:09

做畢設需要用到RealTek公司的10/100M物理層收發器芯片RTL8201BL,使用外部電路配置為自協商、MII操作模式,再通過網絡變壓器連接RJ45接口,與電腦通過網線連接后,能夠自適應成功

2012-07-05 09:34:48

帶有雙MII接口的單片5端口10/100MBPS開關控制器

2023-03-28 18:13:14

功能,無阻塞交換結構,地址管理,一般使用MII接口,8個10/100Base-TX收發器,和9個媒體訪問控制器成單一的0.18μmCMOS器件。它提供了與所有業界標準的以太網和快速以太網設備的兼容性

2016-06-03 13:49:32

目錄01、MII接口方案02、RMII接口方案2.1、外部晶振(2個晶振)2.2、外部晶振(1個晶振)2.3、需要強力PHY在之前的推文中《STM32網絡之SMI接口》《STM32網絡之MII

2021-07-29 07:47:55

ST2014官方tcp/ip協議培訓視頻高清全集,包含內容:地址解析協議ARP以太網基礎介紹1介紹了以太網的物理層和鏈路層,重點討論了MII接口和RMII接口的信號定義和硬件設計,此外,介紹了在官方

2014-08-07 00:10:10

,希望可以對需要進行以太網電路設計的朋友提供幫助。二. 以太網接口STM32 的以太網支持 10M/100M bits 的全雙工和半雙工的工作方式,其中的 MAC 通過 MII 接口或者RMII 接口

2021-01-28 13:17:17

本文使用的是STM32F207VCT6平臺,MII接口的RTL8201EL網絡芯片,LWIP版本是1.4.1基礎工程是:已經實現了10ms定時,led燈1s閃爍,還有串口打印歡迎查看本文所在的系列

2021-08-04 09:21:45

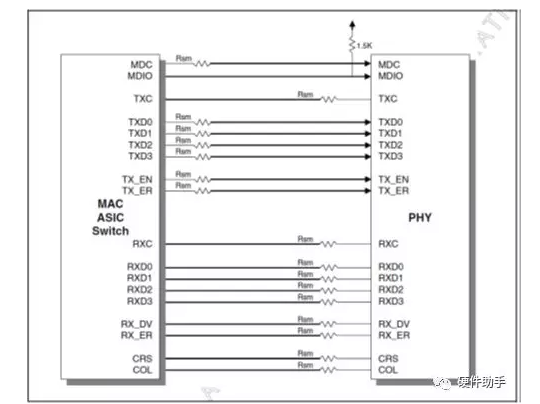

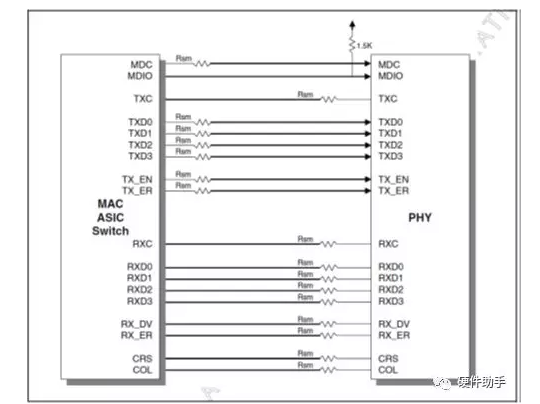

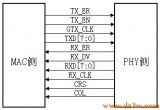

bits的全雙工和半雙工的工作方式,其中的 MAC通過 MII接口或者RMII接口與PHY通訊。 1.MII 如圖 1所示,MII接口標準定義了 16跟信號線,根據功能將其可以分為 3組(發送,接收,載波

2014-11-19 18:20:12

傳輸的,是通過MII接口或者RMII通信的。1、MII接口介質獨立接口(MII)定義了10 Mbit/s和100 Mbit/s的數據傳輸速率下MAC子層與PHY之間的互連。管腳定義介紹:MII_TX_CLK:連續時鐘信號。該信號提供進行TX數據傳輸時的參考時序。標稱頻率為:速率...

2021-08-05 07:01:43

地址支持全/半雙工模式,端口基于VLAN,MII接口和2K字節的FIFO封包緩存器。用戶能通過MII接口與外部PHY或以太網交換芯片構建VoIP網關和IP電話。當CM5000作為IP電話芯片應用時,也

2010-06-02 09:27:34

功應用的設計方案,希望可以對需要進行以太網電路設計的朋友提供幫助。二. 以太網接口STM32 的以太網支持 10M/100M bits 的全雙工和半雙工的工作方式,其中的 MAC 通過 MII 接口或者RMII

2021-08-10 11:28:38

并不是通過SMI接口傳輸的,是通過MII接口或者RMII通信的。1、MII接口介質獨立接口(MII) 定義了10 Mbit/s 和100 Mbit/s 的數據傳輸速率下MAC 子層與PHY 之間的互連。?管腳定義介紹:MII_TX_CLK:連續時鐘信號。該信號提供進行 TX 數據傳輸時的參考時序。

2021-08-05 07:28:55

攝像頭的相關對比介紹。關于圖像傳輸 AC620開發板上有一個百兆以太網PHY芯片RTL8201,對FPGA提供MII接口,使用該芯片,我們可以自己編寫以太網MAC層,然后使用MII接口與RTL8201

2017-06-14 11:51:47

AC620開發板通過一片Realtek的RTL8201以太網PHY提供對以太網連接的支持,RTL8201是一片10M/100M自適應以太網收發器,提供MII/SNI接口的MAC連接。在Cyclone

2017-07-29 23:20:58

1.獨立于介質的接口(MII)獨立于介質的接口(MII)用于MAC與外接的PHY互聯,支持10Mbit/s和100Mbit/s數據傳輸模式。MII的信號線如下圖所示:?MII_TX_CLK:發送數據

2019-05-22 09:02:39

內容及要求檢測MII接口的以太網幀頭,保存ICMP(ping指令)包一個。(1)接收以太網物理芯片傳來的4bit無結構數據,探測幀頭,恢復數據結構;(2)輸入數據時鐘采用PHY的時鐘;(3)將

2018-11-28 17:56:53

。 ? 時鐘產生模塊:產生 MII 接口的時鐘信號,這個時鐘信號需要滿足外部 PHY 芯片對時鐘的要求。? 輸出控制模塊:因為 MII 連接到外部 PHY 的數據線實際只有一根線,輸出控制模塊需要將輸出、輸入

2018-12-29 10:59:10

100BASE-FX。這些設備專為成本敏感型系統而設計,但仍提供多種功能,如交換機管理,基于端口和標簽的VLAN,QoS優先級,一個MII接口以及CPU控制和數據接口。 KSZ8873FLL是VoIP電話,機頂盒/游戲盒,SOHO住宅網關,工業以太網系統以及獨立3端***換機的絕佳選擇

2020-05-20 16:00:17

? ? ? ? ? 疑惑#1:MII接口和RMII接口哪個快?我看MII要比RMII分別多出兩根數據線和地址線,PHY同樣頻率的情況下,是不是MII要快些?

? ? ? ? ? 疑惑#2:看了手冊上

2018-06-21 07:09:52

EVB-LAN9353,評估板,利用LAN9353提供具有雙RMII或單MII / RMII / Turbo MII接口的全功能三端口以太網交換機。 EVB-LAN9353通過板載RJ45連接器提供

2020-08-17 09:39:14

是DP83848,工作在MII接口模式,時鐘頻率是25MHz。現在的LwIP版本已經發展到了lwIP 2.0.3 版。 但是看了具體的代碼后發現一些跟1.4.1對比之下不同之處,其中包含但不全部: 1、IPv...

2021-08-06 06:39:39

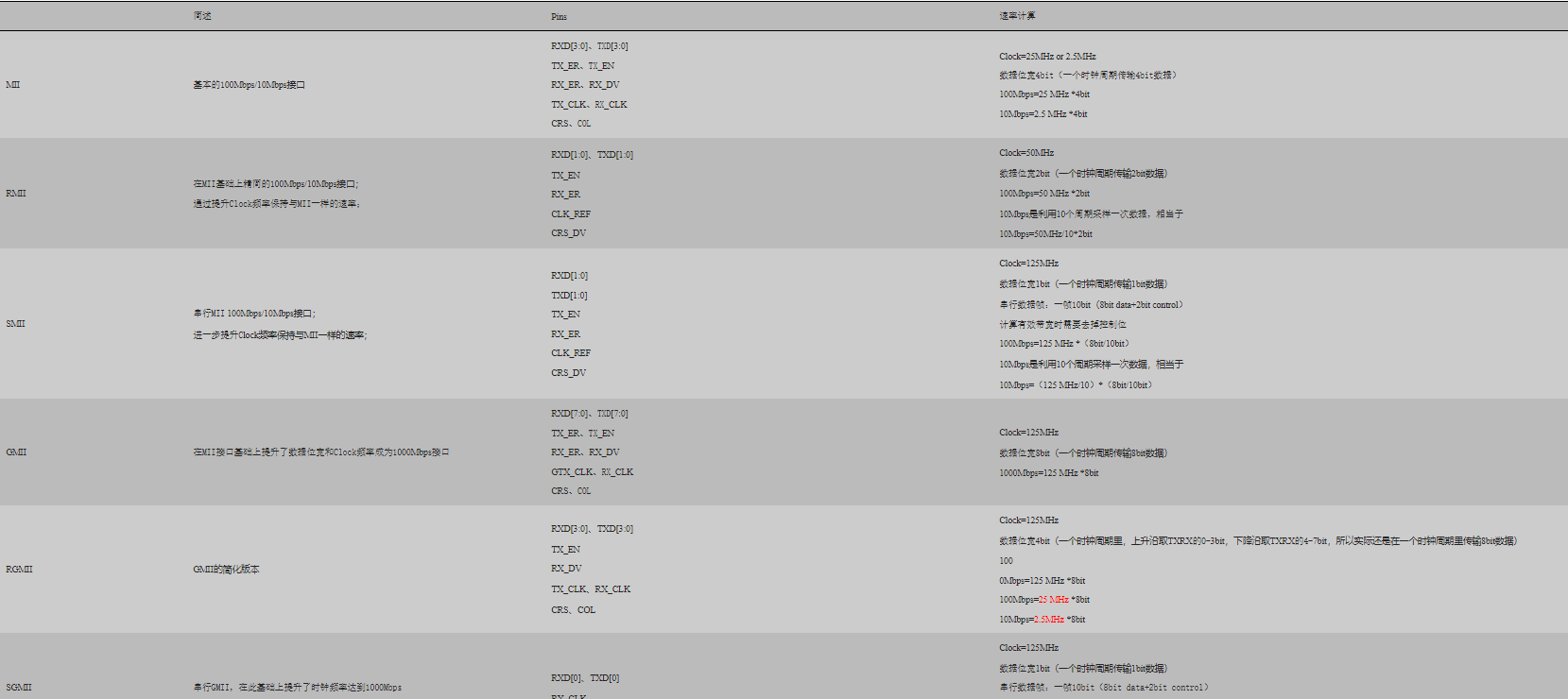

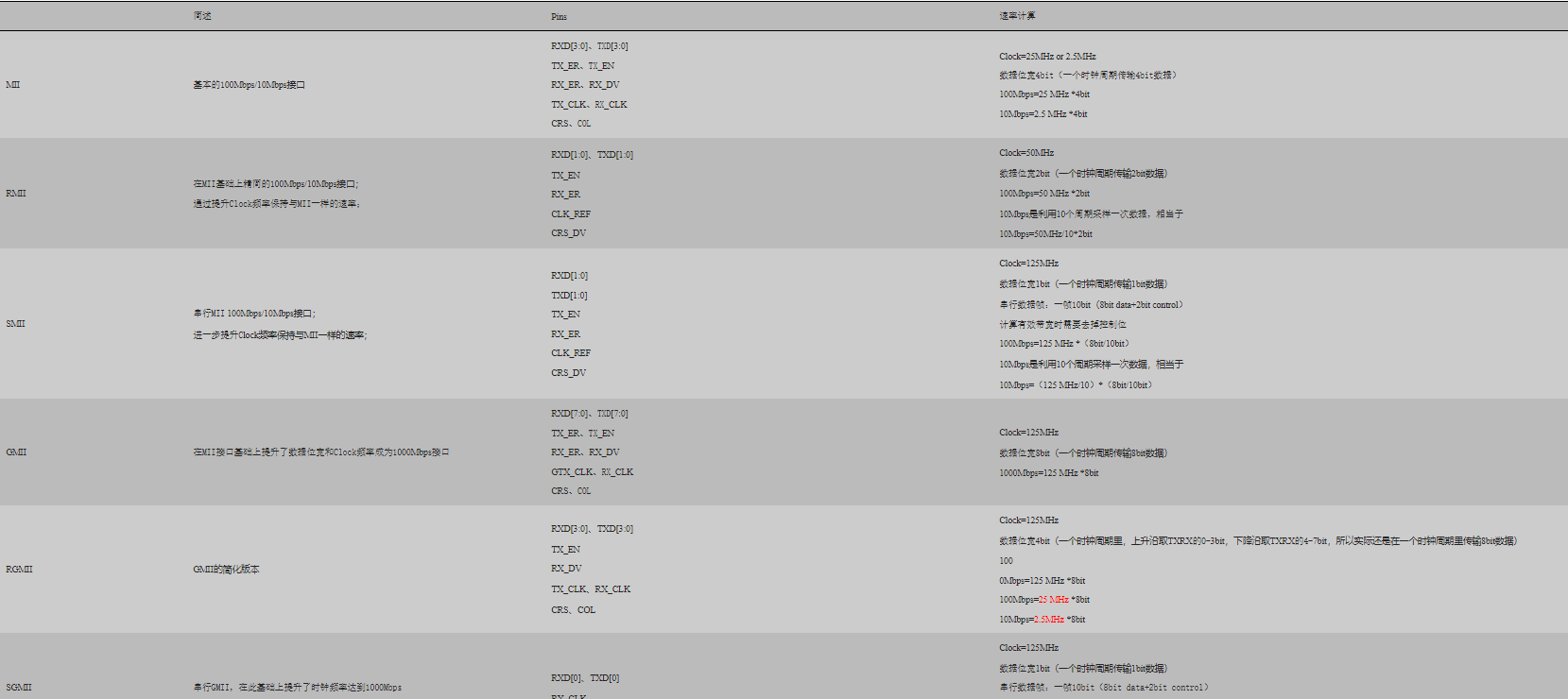

之前介紹MII接口時,有介紹過RGMII接口的由來,下面在貼一下:表8?7 MII接口介紹簡述Pins速率計算MII基本的100Mbps/10Mbps接口RXD[3:0]、TXD[3:0]...

2021-07-20 08:09:53

碼IEC61850的SV和GOOSE。以太網PHY通過MII接口和FPGA,因此FPGA與外部的接口有4路MII接口。項目初期是實現1路光以太網接口,并且驗證功能正確之后,但是后期變成的4路光以太網時,總會存在1路

2018-04-03 11:19:08

協商? - 這個TEMAC核心是否支持autoneg?在此先感謝。任何幫助都會很棒PS:我必須使用沒有可選管理接口(MDIO)的MII接口。

2019-11-05 09:46:20

某些phy芯片同時支持rmii和mii接口,比如ksz8863,那么工作的時候是自動識別連接方式嗎?

2019-09-26 04:13:47

接口MII,RMIIMII即“媒體獨立接口”,也叫“獨立于介質的接口”。它是IEEE-802.3定義的以太網行業標準。它包括一個數據接口,以及一個MAC和PHY之間的管理接口。RMII全稱為“簡化的媒體獨立接口”,是IEEE-802.3u標準中除MII接口之外的另一種實現。1.1. 獨立于介

2021-08-05 07:27:44

通過ODC寄存器,它變高(2伏,不是我預期的3)。謝謝。PS:以太網控制器與PIC32MZ的接口是RMII:這很重要,因為Reduced MII不使用PIN 121,而在MII接口中,這個PIN專用

2020-05-06 13:27:39

大家好我必須與Spartan 6設備建立100 Mbps以太網連接(MII接口)。有沒有人有一個不僅模擬硬件的例子?我試圖從xilinx核心生成器開始工作,但直到現在還沒有成功......也許

2019-05-22 12:47:15

特定應用,RTL8367RB支持兩個額外的接口,可以將其配置為RGMII / MII接口,本工程為普通交換機,

2021-07-27 07:55:40

MII接口的管腳定義有哪些?怎樣通過MII或者RMII接口進行網絡通信呢?

2021-10-28 08:03:00

MII接口模式連接以太網CTLR單芯片10Mbps / 100Mbps

2020-07-15 09:27:57

開發板:杜邦線傳輸高速數字信號容易出錯,所以在用面包板搭建開發環境時,最好使用25MHz時鐘的MII接口。如果要用50MHz的RMII接口,那么杜邦線必須要非常非常短,否則時鐘信號一旦失真,就無法收發數據!【代碼講解】程序里面使用的lwip2...

2021-08-20 06:44:23

看了IP175C和RTL8306,感覺兩個芯片功能類似,對于交換機的應用還好理解,可是將芯片中的MAC5通過MII接口連到外部CPU這里實在費解,既然說MII是PHY和MAC之間的接口,那么這種模式

2012-08-30 14:45:05

PHY 收發器所需的所有其他電壓均在內部產生。特性 符合 EN55011 A 類放射要求低功耗 = 264 mW配置用于 MII 接口的 DP83848K 以太網 PHY用于鏈路和活動的可編程 LED

2022-09-19 07:52:24

PHY 收發器所需的所有其他電壓均在內部產生。主要特色符合 EN55011 A 類放射要求低功耗 = 264 mW配置用于 MII 接口的 DP83848K 以太網 PHY用于鏈路和活動的可編程

2018-12-19 14:39:27

PHY 收發器所需的所有其他電壓均在內部產生。 特性符合 EN55011 A 類放射要求低功耗 = 264 mW配置用于 MII 接口的 DP83848K 以太網 PHY用于鏈路和活動的可編程 LED

2015-04-28 11:45:21

100BASE-FX。這些設備專為成本敏感型系統而設計,但仍提供多種功能,如交換機管理,基于端口和標簽的VLAN,QoS優先級,一個MII接口以及CPU控制和數據接口。 KSZ8873RLL是VoIP電話,機頂盒/游戲盒,SOHO住宅網關,工業以太網系統和獨立3端***換機的絕佳選擇

2020-05-15 08:48:50

是,數據包進來了,但是不知道為何DSP接收到了很多碎片,請問這是什么問題呢?之前這一塊通路還是好的,但是現在突然就不好了,通過示波器觀察MII接口的TXCLK,TXEN,TXD,RXCLK,TXDV,RXD都沒看到異常。

2018-07-25 09:19:45

FETA40i核心板的RGMII接口電壓等級是2.5V嗎?(開發板把它用作MII接口,手冊上寫的是3.3V,現在想用作RGMII做千兆以太網。)

2022-01-05 06:33:48

FETA40i核心板的RGMII接口電壓等級是2.5V嗎?(開發板把它用作MII接口,手冊上寫的是3.3V,現在想用作RGMII做千兆以太網。)[/td]

2022-01-13 06:24:34

原子的例程是RMII接口用的是以太網中斷,我看ST官方例程中用的外部中斷,我使用的是MII接口,沒弄成功,我想問一下這個接口和中斷有沒有必然的聯系?

2019-11-05 03:47:55

本帖最后由 一只耳朵怪 于 2018-6-4 16:35 編輯

am335x,開發板上網口使用的是RGMII或MII接口,但是我們的PHY使用的是RMII接口。我找到

2018-06-04 03:29:39

我想stm32f407通過MII接口接以太網芯片LAN8720A,然后與另外一片以太網芯片對接,rx與tx相連,這樣就雙工了。但是不通過網口,這個可行嗎?我要是想要通過以太網主動發送數據,該怎么實現,還是必須有客戶端和服務器建立連接,這時候才能發數據嗎?

2019-08-14 00:16:59

的右圖)。浩普電子的開發板是印制PCB板,上面采用的是RMII接口,能夠調通。但是面包板搭的那塊板子,背面全是自己接的線,只能調通MII接口(25MHz時鐘),無法調通RMII接口(5...

2022-01-26 07:01:22

您好!客戶想通過cyw43907 Wi-Fi使以太網轉換器。在這種情況下,cyw43907將通過MII接口接收以太網幀傳送Wi-Fi如下。(不要在這種情況下,使用L3層或更高)主機CPU = MII

2018-09-28 15:44:21

制器只負責往協議棧結構芯片的某個寄存器里放上適當的數據。與此同時,用FPGA實現單片機系統接入因特網的方法也日益受到人們的重視。本文提出采用FPGA實現網絡協議棧,介紹100M以太網MII接口協議

2019-04-30 07:00:16

交換機管理,基于端口和標簽的VLAN,QoS優先級,兩個MII接口以及CPU控制和數據接口。 KSZ8873MML是VoIP電話,機頂盒/游戲盒,SOHO住宅網關,工業以太網系統以及獨立3端***換機的絕佳選擇

2020-05-19 09:30:50

HS3210M采用LQFP208和QFP208兩種封裝,內嵌高性能32位嵌入式RISCCPU核,采用龍芯CPU技術,支持通用MIPS32指令集,主頻可達266MHz。網絡方面內置MAC,提供MII

2021-04-15 07:39:51

的微控制器。TMC8460 提供 a/b/n 增量、PWM、SPI 和步進/方向接口、通用 IO,并通過兩個 MII 接口連接到 EtherCAT? 現場總線。該器件需要

2022-11-03 11:58:35

具有工業溫度范圍的低延遲 10/100Mbps PHY、MII 接口和 ENHANCED 模式 Datarate (Mbps) 10/100 Interface type MII

2022-12-07 14:28:27

具有 MII 接口和 ENHANCED 模式的低延遲 10/100Mbps 以太網 PHY Datarate (Mbps) 10/100 Interface type MII

2022-12-07 14:28:27

芯片特點 支持4個10M/100M全雙工以太網MII接口到SONET/SDH的復用與解復用 支持一個1000M全雙工以太網GMII接口到SONET/SDH的復用與解復用 支持HDLC、LAPS及GFP協議封裝

2010-08-02 12:09:57 25

25 RMII接口信號定義 RMII接口(Reduced MII接口)是簡化的MII接口。它也分為MAC模式和PHY模式。 RMII接口接收、發送和控制的同步參考時鐘REF_CLK是由外部時鐘源提供的50MHz信號。這與原來的MII接口

2011-03-28 16:20:33 118

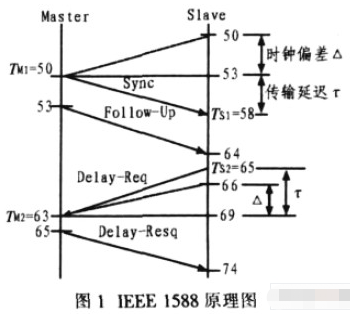

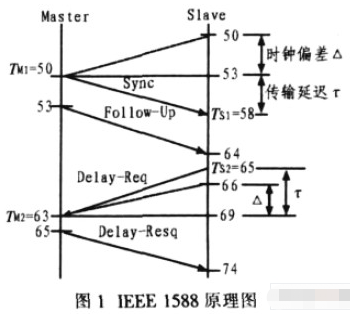

118 MAX24288是一個靈活的,低成本的IEEE 1588時鐘和與SGMII或1000BASE - X串行接口和并行MII接口,可用于GMII,RGMII,或10/100 MII配置timestamper

2011-06-27 11:21:09 2194

2194

MAC發送模塊可將上層協議提供的數據封裝之后通過MII接口發送給PHY。

2017-02-11 04:29:11 6460

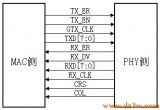

6460 千兆以太網MII接口類型主要有GMII、RGMII、SGMII、TBI和RTBI 五種 GMII接: 與MII接口相比,GMII的TX/RX數據寬度由4位變為8位,GMII接口中的控制信號

2018-05-18 13:54:00 18517

18517

介紹了以太網的物理層和鏈路層,重點討論了MII接口和RMII接口的信號定義和硬件設計,此外,介紹了在官方的例程中如何根據不同的PHY進行軟件的修改。

2018-07-03 05:10:00 18662

18662 IP113SLF內置1個3口交換控制器,1個OAM引擎,1個快速以太網收發機制,1個百兆光口PHY和1個百兆電 (光) 口,1個MII接口,也可配置成為2個SMII接口的PHY使用,強大的交換機

2019-04-16 08:00:00 3

3 在開發以太網接口的過程中經常看到 MII、RMII、GMII、RGMII等英文縮寫名稱。在開發接口前,先將這些名詞搞清楚。 1 MII MII(Medium Independent

2021-01-18 10:34:13 2441

2441

之前介紹MII接口時,有介紹過RGMII接口的由來,下面在貼一下: 表8?7 MII接口介紹 RGMII是GMII的簡化版本,發送端信號:TXD[3:0]、 TX_CLK、TX_EN,接收端信號

2021-04-11 11:04:23 8479

8479

每個節點包含CPU、以太網媒體訪問控制器(MAC)、以太網物理層收發器(PHY)、FPGA等4種主要器件。物理層收發器和MAC控制器通過標準的MII接口相連,CPU通過總線與MAC控制器和FPGA相連。物理層收發器、MAC控制器和CPU構成通訊協議棧完成數據包的發送和接收。

2021-06-10 15:27:59 4535

4535

的右圖)。浩普電子的開發板是印制PCB板,上面采用的是RMII接口,能夠調通。但是面包板搭的那塊板子,背面全是自己接的線,只能調通MII接口(25MHz時鐘),無法調通RMII接口(5...

2021-12-01 18:51:08 23

23 從硬件上來說,一般PHY芯片為模數混合電路,負責接收電、光這類模擬信號,經過解調和A/D轉換后通過MII接口將信號交給MAC芯片進行處理。一般MAC芯片為純數字電路。物理層定義了數據傳送與...

2021-12-29 18:52:36 1

1 是千兆網的MII接口,這個也有相應的RGMII接口,表示簡化了的GMII接口;GMII是8bit并行同步收發接口,采用8位接口數據,工作時鐘125MHz,因此傳輸速率可達1000Mbps。同時兼容MII所規定的10/100 Mbps工作方式。

2022-06-02 14:45:33 2201

2201 的獨立于介質接口),相比較于MII接口(媒體獨立接口),RMII通信所需要的引腳數更少,根據IEEE802.3標準,MII接口需要16個信號引腳,RMII接口則只

2022-09-26 11:38:47 784

784

的獨立于介質接口),相比較于MII接口(媒體獨立接口),RMII通信所需要的引腳數更少,根據IEEE802.3標準,MII接口需要16個信號引腳,RMII接口則只

2023-06-06 10:17:06 595

595

本文主要介紹以太網的MAC(Media Access Control,即媒體訪問控制子層協議)和PHY(物理層)之間的MII(Media Independent Interface ,媒體獨立接口),以及MII的各種衍生版本——GMII、SGMII、RMII、RGMII等。

2023-07-26 11:48:08 6211

6211

MII接口進行通信和連接,到了MultiG車載以太網時,MII接口就包含了更多芯片廠商的接口比如SGMII,USXGMII,XFI等等, 但是往往這些接口是非標準的而且速率越來越高,怎么樣才能更好的進行測試呢? content 直播預告 本期云上大講堂, 泰克技術經理

2023-08-30 10:15:02 427

427

電子發燒友App

電子發燒友App

評論