隨著系統帶寬不斷增加至多吉比特范圍,并行接口已經被高速串行鏈接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是獨立的ASSP 或ASIC 器件。在過去幾年中已經看到有內置SERDES 的FPGA 器件系列,但多見于高端FPGA芯片中,而且價格昂貴。

2015-02-02 17:32:52 2204

2204

GMII、SGMII和SerDes的區別和聯系? GMII和SGMII區別,上一篇已經介紹了,這一篇重點介紹SGMII和SerDes區別。 GMII和SGMII SGMII接口 SGMII

2020-10-09 11:31:29 29958

29958

端高速串行信號重新轉換成低速并行信號。 ? 采用SerDes技術的高速串行接口增加了帶寬,減少了信號數量,同時帶來了諸如減少布線沖突、降低開關噪聲、更低的功耗和封裝成本等許多好處,相比傳統并行總線架構有不少的提升。 ? 并行接口與SerDes ? 串行接口和并行接口的發展

2023-10-12 09:02:14 1624

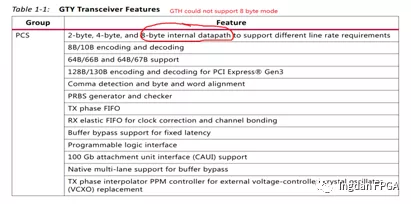

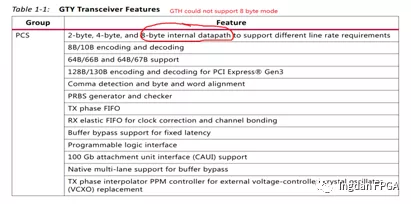

1624 10Gbps的數據,再進行后續的處理。在100G流量獲取中,包括PMA、PCS和MAC共三個模塊。PMA實現100GE的介質接口,由高性能FPGA自帶的高速SERDES實現,一個100GE接口需要10路高速

2014-10-25 16:20:12

串行接口常用于芯片至芯片和電路板至電路板之間的數據傳輸。隨著系統帶寬不斷增加至多吉比特范圍,并行接口已經被高速串行鏈接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是獨立

2019-05-29 17:52:03

隨著接口頻率的提高,在系統同步接口方式中,有幾個因素限制了有效數據窗口寬度的繼續增加。

2019-05-23 07:42:43

FPGA發展到今天,SerDes(Serializer-Deserializer)基本上是標配了。從PCI到PCI Express, 從ATA到SATA,從并行ADC接口到JESD204, 從RIO

2021-07-28 07:02:12

SerDes的發送端TX的均衡原理是什么?怎樣利用高速接口SerDes去實現芯片間信號的有線傳輸?

2021-06-17 07:15:16

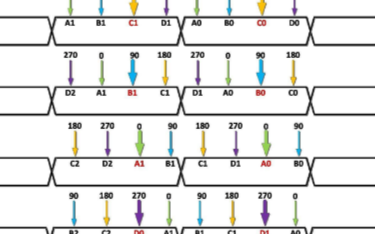

一、SERDES的作用1.1并行總線接口在SerDes流行之前,芯片之間的互聯通過系統同步或者源同步的并行接口傳輸數據,圖1.1演示了系統和源同步并行接口。隨著接口頻率的提高,在系統同步接口方式中

2021-07-26 07:33:44

一、SERDES的作用1.1并行總線接口在SerDes流行之前,芯片之間的互聯通過系統同步或者源同步的并行接口傳輸數據,圖1.1演示了系統和源同步并行接口。隨著接口頻率的提高,在系統同步接口方式中,有幾個因素限制了有效數據窗口寬度的繼續增加。a)、時鐘...

2021-07-28 08:35:42

是否可以將數據總線寬度配置為24位?我檢查了8, 16位和32位之間的差異,只改變了最后8位中的第七十九行(CyuU3pIPIBGPGIFIFBuxCONFIG)。我需要24位數據寬度和SPI為我的啟動從SPI閃存(固件)。如果我查看數據表中的PIN表,可以看到數據總線和SPI總線之間沒有交叉點。

2019-08-21 09:02:22

,極其注重精確性與快速性,GPMC并口“小數據-低時延”的特點顯得格外耀眼,能夠很好地提高數據傳輸效率,降低傳輸成本。

(2)大數據-高帶寬

大數據時代對能源電力領域的數據量傳輸、數據處理等方面

2023-08-22 10:58:39

串行接口常用于芯片至芯片和電路板至電路板之間的數據傳輸。隨著系統帶寬不斷增加至多吉比特范圍,并行接口已經被高速串行鏈接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是獨立

2019-10-23 07:16:35

并口“小數據-低時延”的特點顯得格外耀眼,能夠很好地提高數據傳輸效率,降低傳輸成本。

(2)大數據-高帶寬大數據時代對能源電力領域的數據量傳輸、數據處理等方面提出了更高的要求。GPMC提供了最大

2023-09-30 23:43:29

接口,及串行EPROM接口。LOCAL總線的數據寬度為32位,時鐘頻率可達到50MHZ, 并且支持數據預取功能。PCI9054的總線操作包括PCI總線操作和本地總線操作。對于PCI總線操作,它完全遵守

2008-10-09 11:23:38

:PCI總線接口,LOCAL總線接口及串行EPROM接口。LOCAL總線的數據寬度為32位,時鐘頻率可達到50MHz并且支持數據預取功能。PCI9054的總線操作包括PCI總線操作和本地總線操作。對于PCI

2018-12-05 10:12:42

目錄1、cpu處理的數據寬度2、數據總線寬度3、地址總線寬度4、性能差別1、cpu處理的數據寬度CPU處理的數據的寬度,參與運算的寄存器的數據長度代表單片機的位數。也就是一個一個時鐘周期里,處理器

2021-07-13 06:20:07

嗨,我在我的項目中使用SRIO Gen2 v4 ipcore。我已經在kintex 7(xc7k160t)中實現了它。生成的ipcore具有數據寬度為64的用戶axi接口。有沒有選項可以將用戶界面總線寬度更改為32或16.我無法在ipcore GUI中找到這樣的選項。

2020-04-27 09:52:17

引進。我們在研制某新型飛機火控雷達系統的檢測設備的過程中,組建了VXI總線雷達自動檢測系統。在研制該系統過程中,我們開發了一種利用CPLD和雙口RAM設計的寄存器基VXI總線儀器接口電路,下面我們就這一

2018-11-27 11:48:33

串隨著數據速率的增加,有關實施并行總線的問題也隨之增多。較快總線比較慢總線功耗高,而且由于定時容差的降低,信道數量的增加,布局難度也越來越大。隨著數據速率的增加,保持信道間的時滯也日益重要,原因是較大的時滯差異會導致系統定時問題…

2022-11-21 06:38:25

如何利用以太網硬件協仿真接口實現便捷和高帶寬的仿真?

2021-05-28 06:36:35

的命令隊列。這樣不同的端口都可以訪問Memory接口,完成對Memory的讀寫操作。MPFE都是基于Avalon總線的時序進行地址、命令和數據的交互的。在實際有效帶寬一定的情況下,MPFE可以將帶寬按照

2019-06-13 05:00:06

TMS320C32的外部存儲器接口的特點 TMS320C32是一個32位微處理器,它可以通過24位地址總線、32位數據總線和選通信號對外部存儲器進行訪問。其外部存儲器接口結構如下圖l所示。 在圖l中

2019-06-14 05:00:08

帶寬、易擴展等優點,已經逐漸成為現代數據傳輸的發展趨勢。基于USB的數據采集系統充分利用USB總線的上述優點,有效地解決了傳統數據采集系統的缺陷。USB的規范能針對不同的性能價格比要求提供不同的選擇,以

2009-04-11 17:20:15

串行接口常用于芯片至芯片和電路板至電路板之間的數據傳輸。隨著系統帶寬不斷增加至多吉比特范圍,并行接口已經被高速串行鏈接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是獨立的ASSP 或ASIC 器件。

2019-10-14 06:39:42

(ALE)信號支持區分地址與數據周期.

[size=13.3333330154419px]其實其他系列也都有的。

外部總線接口有下列功能:

? 支持外部設備最大64K字節 (8位數據寬度

2023-06-16 06:41:36

如何利用485總線去傳輸數據呢?傳輸過程是怎樣的?

2022-03-01 07:39:30

什么是DSP流水線協議?如何利用FPGA與ADSP TS201去設計總線接口?

2021-04-28 06:31:06

在雷達信號處理、數字圖像處理等領域中,信號處理的實時性至關重要。由于FPGA芯片在大數據量的底層算法處理上的優勢及DSP芯片在復雜算法處理上的優勢,DSP+FPGA的實時信號處理系統的應用越來越廣泛。那么,我們該怎么利用FPGA與ADSP TS201設計總線接口呢?

2019-08-09 06:56:11

PCI總線是什么?有什么特點?如何利用FPGA去設計PCI總線的接口電路?設計PCI總線接口時應注意哪些問題?

2021-05-31 06:37:24

本文將以嵌入式實時視頻數據存儲系統為例,說明如何利用FPGA作為嵌入式處理器的數據協處理器,利用CPLD進行主處理器與協處理器之間數據通信的方案來解決處理器接口總線速度對系統性能的影響。該方案對解決類似的問題具有一定的參考作用。

2021-05-10 06:30:18

什么是PCI總線?它有什么特點?如何利用FPGA設計PCI總線的接口電路?設計PCI總線接口時應注意哪些問題?

2021-04-29 06:10:31

如何利用雙端口RAM去實現PCI總線接口?

2021-05-06 06:30:53

`我們都知道CAN 總線以其可靠性高、成本優等特點在汽車、工業局域通訊得到廣泛應用。但是隨著各種專用控制器的蓬勃發展,控制功能的需求逐漸復雜多樣化,隨之帶來的是各控制器之間的交互也日趨復雜。CAN

2019-12-19 15:09:07

Recovery,時鐘數據恢復),完成100~200Mhz的板間SERDES單通道通信,該SERDES接口方案具有成本低、靈活性高、研發周期短等特點。

2019-10-21 07:09:44

嗨,在xilinx應用筆記(XAPP973第2頁)中,我發現聲明“iMPACT僅支持通過Virtex-5 FPGA系列成員進行間接編程的16位數據總線寬度。”它是否仍適用于Virtex 6 FPGA

2020-06-08 13:10:56

帶來了總線效率的問題,針對變長數據輸入的情景,當芯片內部總線位寬變大時,若每個總線字在數據傳輸過程中不能被有效利用,則可能導致總線效率降低。原作者:徐銘偉、劉歡

2022-10-11 14:27:34

是高精度的在線測量設備,應用于扁平吊帶的自動寬度測量當中,可配備軟件分析系統,為您帶來高質量的多種數據信息,提升生產效率,對扁平吊帶進行實時監測。</p> 扁平吊帶寬度的在線精準測量`

2018-12-13 10:09:58

的,但是現在提一下,基頻的計算方式,若當前serdes傳輸0101的方波pattern,可以使得信號變化最劇烈,這時候信號的帶寬是最高的,方波信號的周期就是data rate/2。例如:一個時鐘信號

2023-03-24 15:12:28

PCI總線特點及開發現狀PCI接口配置空間的實現求一款在PCI總線上利用FPGA技術設計PCI總線接口的設計方案

2021-04-15 06:17:20

使用 cyusb3014 主模式時出現數據寬度問題。

我將 AutoMaster 的示例更改為在 FPGA 中訪問標準 FIFO。 有兩個變化:

1. GPIF 狀態機要兼容標準 FIFO 接口時序

2024-02-23 06:16:59

傳輸,最大總線速度是40 MB/s。1996年的新標準VME64(ANSI/VI-TA1-1994)將總線數據寬度提升到64位,最大數據傳輸速度為80 MB/s。而由FORCE COMPUTERS制定

2019-04-22 07:00:07

;(2)設置本地數據總線的寬度是16位時,分別表示(高字節有效)、(低字節有效)、LA1(地址位1)信號::,LD[07..00]有效;:LA1;:沒有使用;:,LD[15..08]有效;(3)設置

2019-05-30 05:00:02

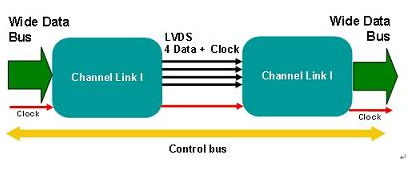

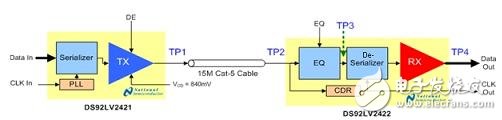

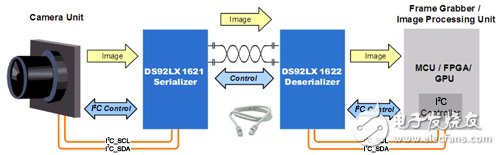

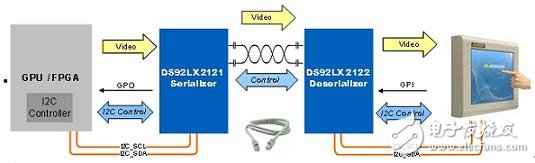

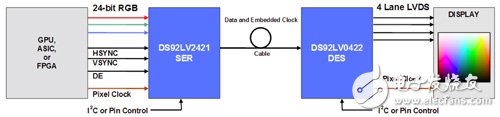

姚琳為了滿足視頻系統、工業和醫療顯示和視頻傳送等應用消除較長連接電纜限制、提高數據速率,以及需要雙向傳輸輔助數據的要求,Intersil公司推出了一款采用雙向I2C接口的SERDES IC

2019-05-08 07:00:01

親愛的先生,FX3支持32位GPIF II接口。我們使用GPIF設計器1來繪制接口和狀態機圖。在接口中只有8、16、24、32選擇GPIF數據總線寬度。但是我需要12 GPIF數據總線。請幫助選擇12位GPIF數據總線。謝謝你最好的問候,拉米什

2019-09-17 12:28:17

求一頻帶寬度測量量方法。

2012-04-08 10:42:06

SERDES結構是怎樣構成的?高速SERDES接口在網絡方面有哪些應用?

2021-04-28 07:19:38

利用單總線傳輸數據與電源

2009-05-04 13:33:12 28

28 PCI 總線是先進的高性能32/64 位局部總線,成為微機總線標準。PCI 總線接口設計較其它總線接口設計復雜,本文討論了接口設計的方案,選擇CH365 作為接口芯片,描述了數據采集

2009-08-19 10:19:55 27

27 提出了一種利用USB總線接口的數據采集系統的設計方案,并給出了系統的硬件與軟件的具體實現方法。通用串行總線作為一種嶄新的微機總線接口規范,其特點十分適合應用

2009-08-31 11:40:19 19

19 M31 SerDes PHY IP M31 SerDes PHY IP為高帶寬應用提供高性能、多通道功能和低功耗架構。SerDes IP支持從1.25G到10.3125Gbps的數據速率

2023-04-03 20:29:47

串行接口常用于芯片至芯片和電路板至電路板之間的數據傳輸。隨著系統的帶寬不斷增加至多吉比特范圍,并行接口已經被高速串行鏈接,或SERDES (串化器/ 解串器)所取代。起初

2010-02-25 23:03:44 38

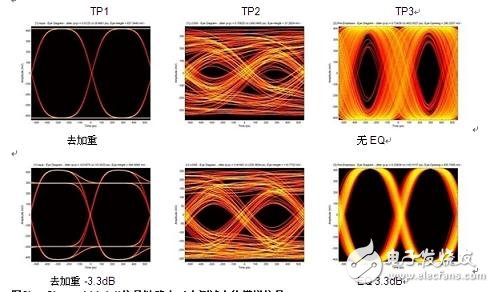

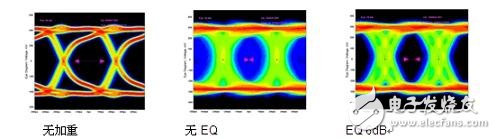

38 利用眼圖模板評估串行器和解串器(SerDes)的性能

Abstract: Maxim has developed a family of serializer and deserializer

2008-11-26 14:08:24 2054

2054

利用TJA1080的FlexRay總線接口設計

介紹基于TJA1080的FlexRay總線在數字信號處理器(DSP)C5509上的實現。整個系統以DSP為核心,采用TJA1080總線控制器實現F

2009-03-29 15:13:40 9009

9009

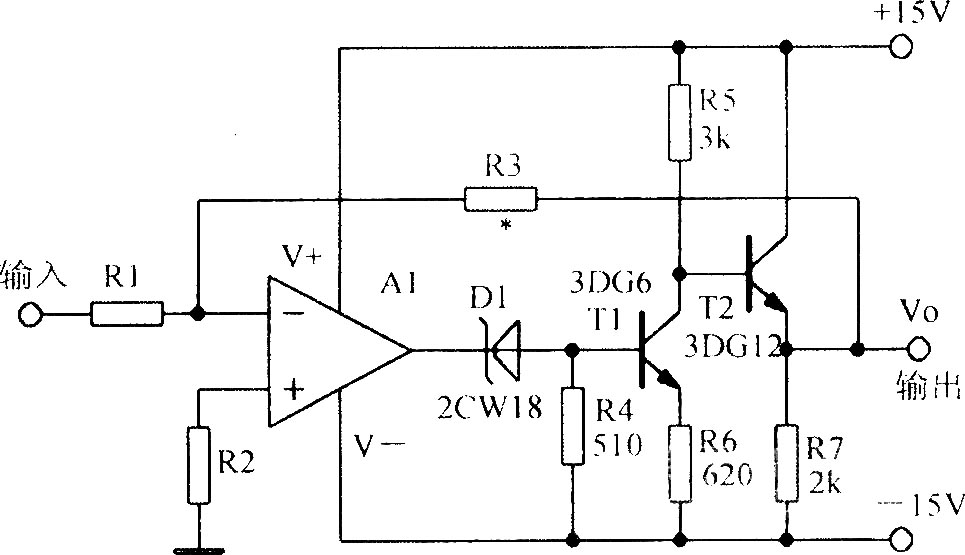

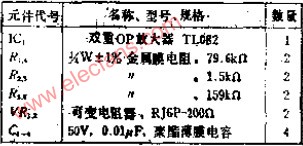

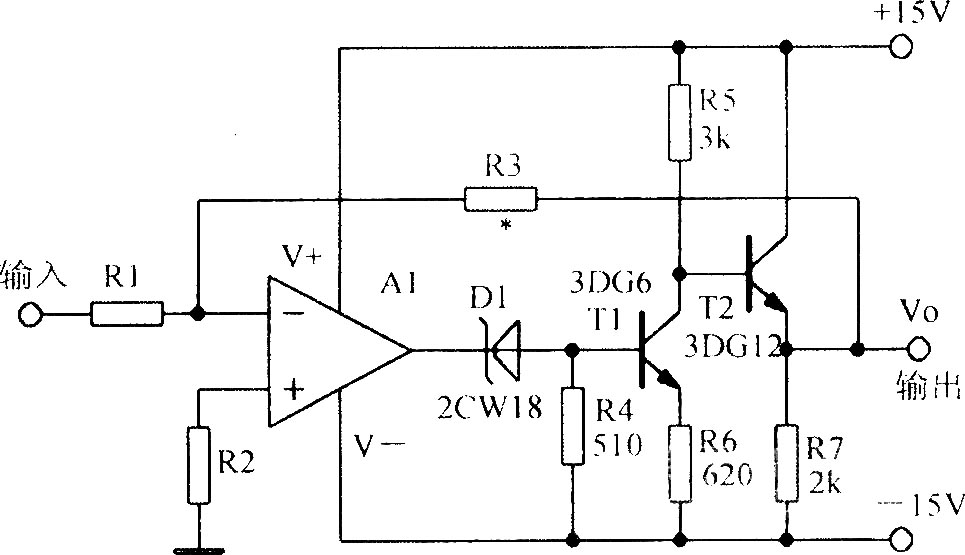

能夠擴展頻帶寬度的放大電路圖

2009-04-02 15:54:42 1414

1414

條碼打印機的碳帶寬度/碳帶長度 碳帶寬度

2009-12-30 11:49:58 1797

1797 什么是數據總線寬度/地址總線寬度?

數據總線寬度

數據總線負責整個系統的數據流量的大

2010-02-04 10:25:01 6588

6588 高帶寬嵌入式應用中SoC微控制器的新型總線開發

傳統SoC總線架構已不能滿足新的聯網嵌入式設計對高帶寬數據流進行實時控制的需求, NetSilicon開發的可編程總線帶寬

2010-03-03 16:16:51 622

622

什么是交換帶寬/背板帶寬

交換機的背板帶寬,是交換機接口處理器或接口卡和數據總線間所能吞吐的最大數據量。背板帶寬標志了交

2010-04-07 16:35:17 720

720 可擴大通帶寬度的有源雙調諧電路

電路的功能

帶通濾波器為了獲得

2010-05-14 12:04:44 1037

1037

PC/104作為一種嵌入式總線標準已經被很多控制系統所采用,而PCIE/104接口的提出將未來最為流行的串行差分總線結構,引入到了這種嵌入式總線標準,從而為各種高速、高帶寬的嵌入式系

2011-08-17 11:04:06 4109

4109

數字系統的設計師們面臨著許多新的挑戰,例如使用采用了串行器/解串器(SERDES)技術的高速串行接口來取代傳統的并行總線架構。基于SERDES的設計增加了帶寬,減少了信號數量,同時帶來了諸如減少布線

2017-10-26 15:37:45 4

4 Recovery,時鐘數據恢復),完成100~200Mhz的板間SERDES單通道通信,該SERDES接口方案具有成本低、靈活性高、研發周期短等特點。

2019-05-24 15:33:25 4072

4072

只要SERDES接口的高級架構是合理的,SERDES總線的成功實現就歸結為“實現細節”。

2019-08-14 17:57:00 2615

2615 很多人把計算機總線寬度和總線帶寬混為一談,其實他們是不一樣的。

2019-09-01 09:52:44 13427

13427 串行接口常用于芯片至芯片和電路板至電路板之間的數據傳輸。隨著系統帶寬不斷增加至多吉比特范圍,并行接口已經被高速串行鏈接,或SERDES (串化器/ 解串器)所取代。

2020-05-18 10:51:18 2964

2964

總線而成為高速接口設計的主流。 如今,隨著SerDes接口的廣泛應用,許多高端的FPGA都內嵌有SerDes接口硬核。在FPGA中內嵌的SERDES的硬核,可以大大地擴張FPGA的數據吞吐量,節約功耗,提高性能,使FPGA在高速系統設計中扮演著日益重要的角色。 國產

2020-07-28 12:05:16 1128

1128 速度的并行總線傳輸串行化的數據。一個實例是用單個PCI-Express 通道,替代傳統的32 位、64MHz PCI 總線(可達到2.112Gb/s) ,僅用4 條線(運行在2.5GHz) ,可達到4Gb/s總數據率。簡言之, SERDES 協議允許用較少的引腳數傳輸較高的數據率。

2020-10-09 17:25:07 18

18 因為攝像頭輸出的LVDS信號速率會達到600Mbps,我們將不能夠通過FPGA的I/O接口直接去讀取這么高速率的信號。因此,需要使用Xilinx FPGA內的SerDes去實現高速數據的串并轉換。

2020-12-30 17:24:00 39

39 AD5425:帶串行接口的8位高帶寬乘法DAC數據表

2021-04-14 12:53:57 11

11 AD5452W:帶串行接口的12位高帶寬乘法DAC數據表

2021-04-14 13:04:56 0

0 盡管SERDES(SERializer/DESerializer)擁有十分復雜的設計和驗證過程,但已成為SoC中不可或缺的組成部分。成熟穩定的SERDESIP,降低了設計成本和風險,加快了產品SoC

2021-07-23 11:21:19 3986

3986 SERDES的優勢 引腳數量和通道優勢 SERDES最明顯的優勢是具備更少的引腳數量和線纜/通道數量。對于早期的SERDES,這意味著數據可以通過同軸電纜或光纖發送。 對于現代的SERDES來說

2021-07-23 11:59:46 3794

3794 總線帶寬就是總線的最大傳輸速度,帶寬越大速度就越快。但是總線帶寬的計算公式里卻要除以一個8很多人都不知道為什么,接下來詳細介紹一下:

2022-01-29 17:04:00 14959

14959 本文給大家提供利用axi_master接口指令端的幾個靜態參數的優化技巧,從擴展總線接口數量,擴展總線位寬,循環展開等角度入手。最核心的優化思想就是以資源面積換取高帶寬的以便并行計算。

2022-07-01 09:39:14 1015

1015 在Serdes流行之前,芯片之間的數據傳輸主要靠低俗串行接口和并行接口,存在諸如傳輸速率低、占用IO數量多、硬件連接復雜化等弊端。Serdes的出現簡化了數據傳輸接口的硬件設計,大大提升了數據

2022-08-02 11:28:14 4854

4854

鋁帶寬度測量(激光三角反射傳感器測寬方案)

2022-09-21 17:34:31 194

194

首先我們要了解什么是SerDes,SerDes的應用場景又是什么呢?SerDes又有哪些常見的種類?

2023-06-06 17:03:55 4706

4706

? 串行接口常用于芯片至芯片和電路板至電路板之間的數據傳輸。隨著系統帶寬不斷增加至多吉比特范圍,并行接口已經被高速串行鏈接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是獨立

2023-07-27 16:10:01 1565

1565

FPGA發展到今天,SerDes(Serializer-Deserializer)基本上是器件的標配了。從PCI發展到PCI-E,從ATA發展到SATA,從并行ADC接口到JESD204,從RIO

2023-10-16 14:50:37 558

558

呢? 1. 帶寬利用率:SerDes技術可以通過將多個并行數據通道轉換為單個高速串行鏈路來提高帶寬利用率。這種方式可以減

2023-11-07 10:26:07 512

512

電子發燒友App

電子發燒友App

評論