并行PCB設(shè)計的原則

隨著它們承載的器件的復(fù)雜性提高,PCB設(shè)計也變得越來越復(fù)雜。相當(dāng)長一段時間以來,電路設(shè)計工程師一直相安無事地獨立進行

2009-09-25 10:35:09 1071

1071

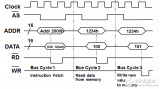

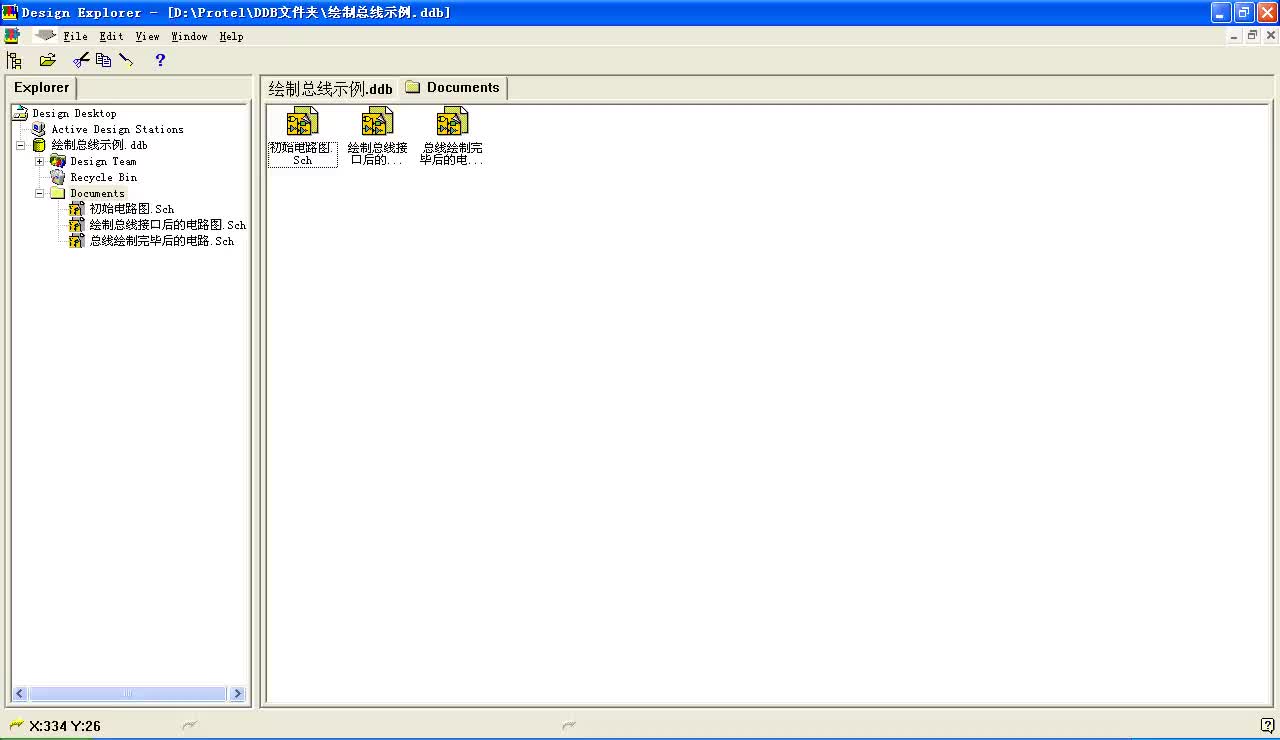

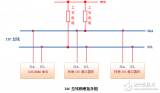

由于FPGA技術(shù)和ARM技術(shù)應(yīng)用越來越廣泛,通過設(shè)計并行總線接口來實現(xiàn)兩者之間的數(shù)據(jù)交換,可以較容易地解決快速傳輸數(shù)據(jù)的需求,因此設(shè)計滿足系統(tǒng)要求的FPGA并行總線顯得尤為重要。本文設(shè)計的FPGA的ARM外部并行總線接口,滿足了總線的時序要求,并在某航空機載雷達應(yīng)答機中進行了應(yīng)用.

2013-08-15 10:44:19 7204

7204

作為一名PCB設(shè)計工程師,具備一些高速方面的知識是非常有必要的,甚至說是必須的。就信號來說,高速信號通常見于各種并行總線與串行總線,只有知道了什么是總線,才能知道它跑多快,才能開始進行布線。

2022-12-29 14:23:12 1438

1438

。還要理解一些長用的總線的概念和信號特性,最簡單的例子,只有理解了串行總線和并行總線之間的差異,才能更好的在PCB上針對串行和并行信號做最佳的處理,只有理解了差分信號的特性,才能更好的對USB

2014-11-07 09:27:40

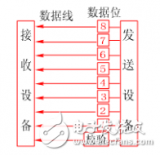

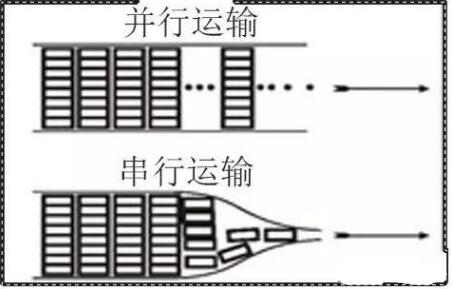

速度快,處理簡單。 串行數(shù)據(jù)傳輸時,數(shù)據(jù)是一位一位地在通信線上傳輸?shù)模扔删哂袔孜?b class="flag-6" style="color: red">總線的計算機內(nèi)的發(fā)送設(shè)備,將幾位并行數(shù)據(jù)經(jīng)并--串轉(zhuǎn)換硬件轉(zhuǎn)換成串行方式,再逐位經(jīng) 傳輸線到達接收站的設(shè)備中,并在接收端

2018-01-11 09:40:02

,還可附加一位數(shù)據(jù)校驗位。接收設(shè)備可同時接收到這些數(shù)據(jù),不需要做任何變換就可直接使用。并行方式主要用于近距離通信。計算 機內(nèi)的總線結(jié)構(gòu)就是并行通信的例子。這種方法的優(yōu)點是傳輸速度快,處理簡單。串行

2017-11-24 18:24:57

串行通信中的IIC總線工作原理51本身不帶IIC總線 ,使用程序模擬IIC通信協(xié)議常用的串行總線協(xié)議UART、1-wire、I2C和SPI總線UART:是以異步方式進行通信(一條數(shù)據(jù)輸入線,一條

2021-12-08 07:52:26

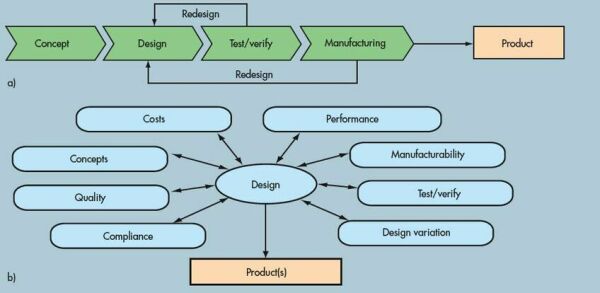

本文總結(jié)了并行PCB設(shè)計各個階段的關(guān)鍵準(zhǔn)則。

2021-02-24 08:36:59

的另一個因素。串行總線架構(gòu)比并行總線架構(gòu)更受青睞,這就要求PCB設(shè)計工程師對損耗、耦合傳輸線及詳盡的過孔模型實施仿真。 物理實現(xiàn) 當(dāng)通過仿真剔除性能問題后,下一步是對電路進行布局布線以生成物理原型。布局

2018-09-30 11:46:23

?管腳數(shù)多少?管腳配置怎樣? 3. 基于成本和性能的權(quán)衡,采用幾層PCB? 4. 時鐘頻率和信令速度等參數(shù)的目標(biāo)值是什么? 此外,設(shè)計工程師還應(yīng)考慮總線架構(gòu)、是采用并行還是串行連接等因素,以及阻抗匹配

2018-11-23 11:02:36

本文匯總了并行PCB設(shè)計的一些關(guān)鍵準(zhǔn)則。

2021-04-26 06:42:38

作者:周偉本篇這里所指并行信號和串行信號,包括了傳輸(通信)方式,又有接口類型,同時還有數(shù)據(jù)本身的協(xié)議特點,信號、協(xié)議、總線和接口。想了解信號、協(xié)議、總線和接口之間的區(qū)別的,可以看前一篇文章:高速串行簡史(一):信號、接口、協(xié)議及總線

2019-07-23 08:42:37

IO 口分別賦值,同時進行信號輸出,類似于有 8 個車道同時可以過去 8 輛車一樣,這種形式就是并行的,我們習(xí)慣上還稱 P0、P1、P2 和 P3 為 51 單片機的 4 組并行總線。而串行通信,就如...

2022-01-19 06:42:28

AD1847串行端口音頻編解碼器如何與并行總線接口的實例

2009-05-13 09:57:27

FPGA 中模擬 I2C 接口已成為 FPGA 開發(fā)必要的步驟。I2C 協(xié)議作為一個串行總線標(biāo)準(zhǔn)盡管沒有并行總線的數(shù)據(jù)吞吐能力,但是它的以下特點使其有著廣泛的應(yīng)用:? 只需要兩條總線—串行數(shù)據(jù)線 SDA

2018-09-29 09:37:11

復(fù)雜度日益增加的系統(tǒng)設(shè)計要求高性能FPGA的設(shè)計與PCB設(shè)計并行進行。通過整合FPGA和PCB設(shè)計工具以及采用高密度互連(HDI)等先進的制造工藝,這種設(shè)計方法可以降低系統(tǒng)成本、優(yōu)化系統(tǒng)性能并縮短

2018-09-21 11:55:09

IIC總線串行技術(shù)的電子書

2013-02-19 16:32:23

PCI總線PCB布線有什么要求嗎?

2015-10-23 15:46:31

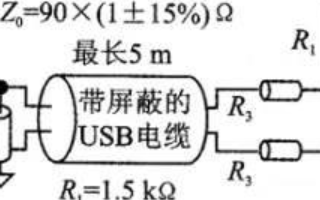

USB通用串行總線是什么?USB通用串行總線有哪些技術(shù)指標(biāo)呢?

2021-10-14 13:51:51

Allegro高速PCB設(shè)計技巧視頻--PCB設(shè)計必備免費分享有問題加QQ451701569 [qq]451701569[/qq]自行下載學(xué)習(xí)鏈接: http://pan.baidu.com/s

2016-05-10 19:54:57

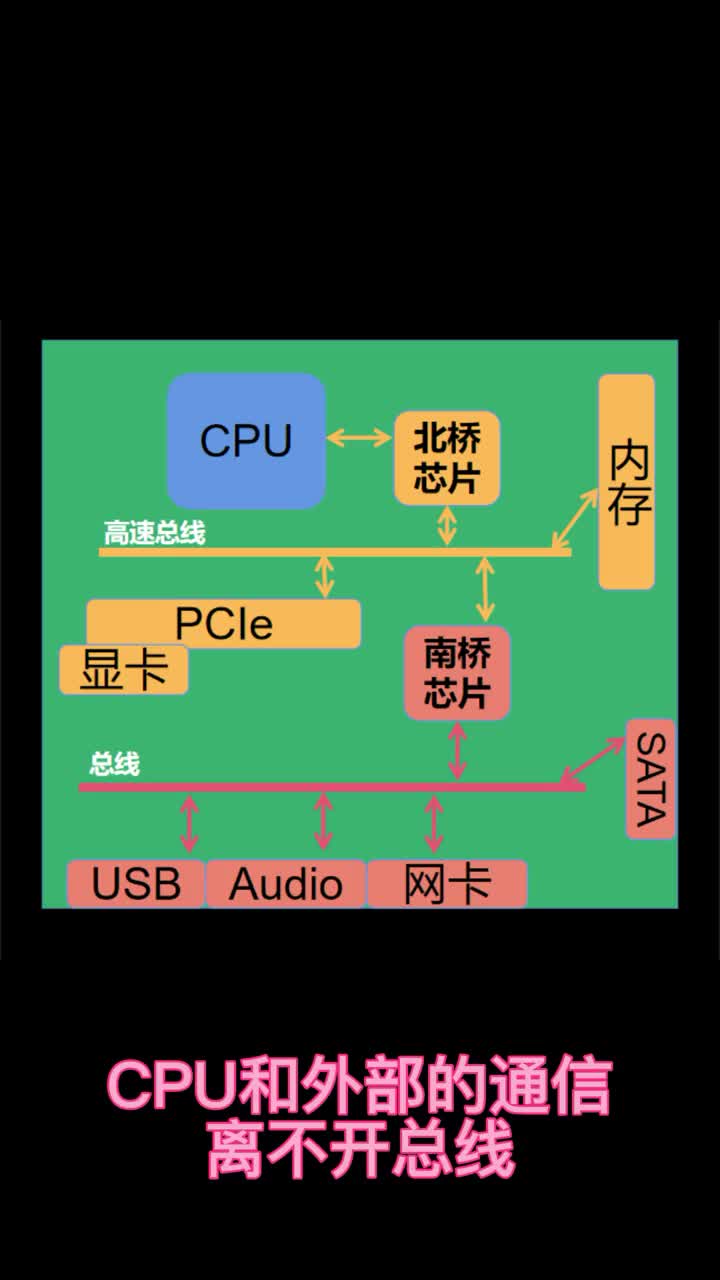

PCIe總線概述隨著現(xiàn)代處理器技術(shù)的發(fā)展,在互連領(lǐng)域中,使用高速差分總線替代并行總線是大勢所趨。與單端并行信號相比,高速差分信號可以使用更高的時鐘頻率,從而使用更少的信號線,完成之前需要許多單端并行數(shù)據(jù)信號才能達到的總線帶寬。PCI總線使用并行總線結(jié)構(gòu),在同一條總線上的所有外...

2021-07-29 07:07:06

Part1.基礎(chǔ)知識小tip:計算機USB接口: 全稱Universal Serial Bus(通用串行總線) ,即日常生活中的USB數(shù)據(jù)線串口:串行數(shù)據(jù)接口,串行發(fā)出數(shù)據(jù),與并行傳輸數(shù)據(jù)不同,串口

2022-02-23 06:38:58

做PCB設(shè)計的都知道,沒有一點高速方面的知識,你就不是一個有經(jīng)驗的PCB設(shè)計工程師。高速信號常見于各類的串行總線與并行總線,只有你知道是什么總線,你還得知道它跑多快,才能開始進行布線。什么是串行總線

2019-10-01 07:00:00

等串行總線接口只能實現(xiàn)FPGA 和ARM 之間的低速通信 ;當(dāng)傳輸?shù)臄?shù)據(jù)量較大.要求高速傳輸時,就需要用并行總線來進行兩者之間的高速數(shù)據(jù)傳輸.

2019-09-17 06:21:10

Motorola開發(fā)。SPI為并行同步總線(兩條串行數(shù)據(jù)線,一條串行時鐘線)通過SPI的互連可構(gòu)成各種應(yīng)用系統(tǒng)。SCI為異步通信接口。 ·VESA總線(Video ELECTRONICS

2008-08-05 06:09:58

正如標(biāo)題所說,我想將 ESP32 連接到 32 位并行總線。我想知道是否可以使用 4 個 8 位串行到并行移位寄存器并使用 QSPI 連接它們,以便每個 8 位寄存器連接到它自己的 QSPI 數(shù)據(jù)信號。這當(dāng)然只有在可以為此目的規(guī)避/濫用 QSPI 命令、地址等階段時才有效。

2023-04-12 06:39:24

串行總線的發(fā)展一共目前可以總結(jié)分為]時鐘并行總線:小于]源同步時鐘并行總線:小于 3200Mbps,比如 DDRr1234 系列,MII,EMMC高速串行總線:最高有]那么對于這些信號的重要線信號的處理我們在設(shè)計過程中應(yīng)該注意哪幾點?

2019-09-12 16:28:07

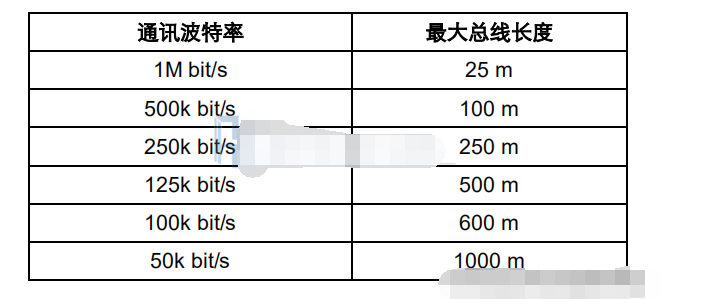

小編補充CAN總線通信的相關(guān)知識

2021-05-14 06:55:27

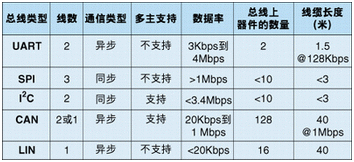

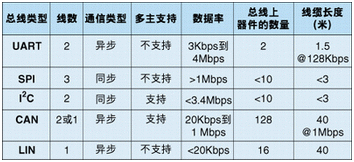

一、常用的串行總線協(xié)議目前常用的微機與外設(shè)之間進行數(shù)據(jù)傳輸?shù)?b class="flag-6" style="color: red">串行總線主要有UART、1-write、I2C和SPI總線。1.UART:異步方式進行通信(一條數(shù)據(jù)輸入線、一條數(shù)據(jù)輸出

2021-11-03 07:14:31

常用的串行總線協(xié)議I2C總線、SPI總線、SCI總線I2C總線:同步串行2線方式進行通信(一條時鐘線,一條數(shù)據(jù)線)SPI總線:同步串行3線方式進行通信(一條時鐘線,一條數(shù)據(jù)輸入線,一條數(shù)據(jù)輸出

2021-11-19 06:46:41

常用的串行擴展總線有:I2C總線,SPI總線,單總線,Microwire/PLUS。I2C串行總線概述I2C串行總線,是具備多主機系統(tǒng)所需的包括總線裁決和高低速器件同步功能的高性能串行總線。I2C

2022-01-11 08:15:08

主板、聲卡、顯卡、網(wǎng)卡等多塊PCB板連接在一起。PCI總線是典型的并行總線,缺點是占用芯片管腳數(shù)量太多,不利于系統(tǒng)數(shù)據(jù)交換容量的提升。所以,在并行總線的基礎(chǔ)上,出現(xiàn)了串行總線、一對差分串行信號的信號速率

2016-10-14 16:53:15

PCB設(shè)計團隊的組建建議是什么高性能PCB設(shè)計的硬件必備基礎(chǔ)高性能PCB設(shè)計面臨的挑戰(zhàn)和工程實現(xiàn)

2021-04-26 06:06:45

IC串行總線一般有兩根信號線,一根是雙向的數(shù)據(jù)線SDA,另一根是時鐘線SCL,其時鐘信號是由主控器件產(chǎn)生。所有接到IIC總線設(shè)備上的串行數(shù)據(jù)SDA都接到總線的SDA上,各設(shè)備的時鐘線SCL接到總線

2022-01-14 07:40:31

)的基本知識、架構(gòu)、性能及選型5) ;常用總線的基本知識、性能詳解6) ;各種存儲器的詳細性能介紹、設(shè)計要點及選型7) ;Datacom、Telecom領(lǐng)域常用物理層接口芯片基本知識,性能、設(shè)計要點及選型

2015-02-03 15:17:07

萌新求助關(guān)于PCB設(shè)計的知識點

2021-04-27 06:28:15

請問如何對FlexRay串行總線進行調(diào)試?

2021-05-10 07:11:49

世界通信。然而今天,嵌入式系統(tǒng)設(shè)計中使用的越來越多的構(gòu)件將用串行總線代替寬并行總線,原因如下:■ 減少了要布線的信號數(shù)量,降低了要求的電路板空間■ 降低了成本■ 降低了功率要求■ 減少了封裝上的針腳

2008-11-26 09:33:38

通用串行總線USB是什么?通用串行總線USB的特點有哪些?通用串行總線USB有哪些技術(shù)指標(biāo)?

2021-10-18 08:52:21

高速串行總線與并行總線的差別是什么?高速測試方面的挑戰(zhàn)是什么?遠端環(huán)回的優(yōu)點是什么?

2021-05-12 06:31:54

幾乎任何地改變都是趨利避害:拿芯片間通信為例,過去幾乎完全是并行總線,礙于技術(shù)限制,使用串行總線所需的serialize(串行化)以及deserialize(解串行化)所需的邏輯量遠遠超過了減少引腳數(shù)量所帶來的節(jié)省。得不償失!

2021-07-27 06:50:27

對于60M10路并行總線一般采取多大的線寬和線間距,保證不會有串?dāng)_。芯片手冊上說的是這10路電平的上升和下降沿的時間為1ns,我用Allegro 定義的約束規(guī)則是:傳輸線阻抗70歐姆,傳輸延遲為0.1ns~0.5ns。板材為4層板,F(xiàn)R4。謝謝!

2014-04-12 23:15:26

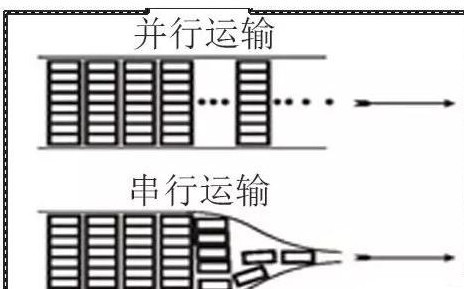

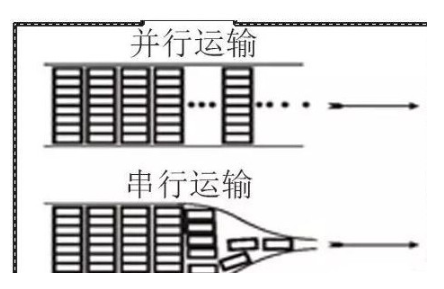

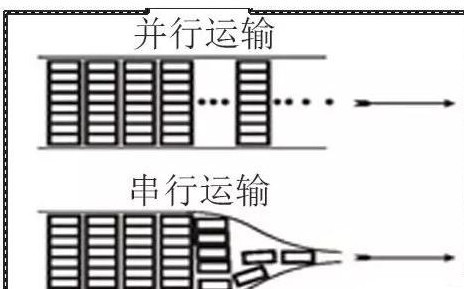

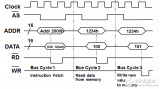

調(diào)試嵌入式系統(tǒng)設(shè)計中的低速串行總線:并行與串行比較在并行結(jié)構(gòu)中,總線的每個組件都有自己的信號路徑。可能有16 條地址線、16 條數(shù)據(jù)線、一條時鐘線和各種其它控制信號

2008-11-26 09:26:34 28

28 pcb設(shè)計教程內(nèi)容有:高速PCB設(shè)計指南之一 高速PCB設(shè)計指南之二 PCB Layout指南(上) PCB Layout指南(下) PCB設(shè)計的一般原則 PCB設(shè)計基礎(chǔ)知識 PCB設(shè)計基本概念 pcb設(shè)計注意

2009-01-18 13:08:07 0

0 AD1847串行端口音頻編解碼器如何與并行總線接口的實例

2009-05-13 09:54:41 25

25 AD1847串行端口音頻編解碼器如何與并行總線接口的實例

2009-05-15 15:13:14 27

27 本文研究 CAN 總線在電梯串行通訊中的應(yīng)用。論文對比RS-485 通訊方式,分析CAN 總線應(yīng)用于電梯串行通訊中的優(yōu)點,采用SJA1000 設(shè)計了CAN 總線通訊硬件,優(yōu)化CAN總線的通信參數(shù),提高

2009-06-25 13:28:03 27

27 PCB設(shè)計與技巧知識

2009-11-19 17:28:48 79

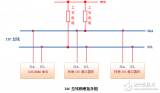

79 總線時鐘結(jié)構(gòu)科利登系統(tǒng)有限公司大部分并行總線和高速串行總線的區(qū)別主要在于發(fā)送端和接收端不同的同步方式。由于其很高的復(fù)雜性,總線時鐘結(jié)構(gòu)成為芯片架構(gòu)的最主要

2009-12-19 15:25:48 17

17 PCA9564是一款采用CMOS工藝,支持并行總線與串行I2C總線通信轉(zhuǎn)換的接口器件,適用于微控制器/處理器使用并行總線擴展I2C總線接口。它支持并行總線與I2C總線雙向通信,在I2C總線上

2010-03-10 15:47:12 51

51 PCA9665是一款并行總線與串行I2C總線接口轉(zhuǎn)換的器件,適用于微控制器/處理器使用并行總線擴展I2C總線接口。它支持并行總線與I2C總線雙向通信,在I2C總線上,它可以設(shè)置為主機或從

2010-03-10 15:49:10 46

46 PCF8584是一款采用CMOS工藝制作的集成電路,微處理器/微控制器通過它可以將并行總線轉(zhuǎn)換成串行的I2C總線,它支持并行總線和串行I2C總線間的雙向通信。它既可以作為主機也可以作

2010-03-10 15:52:32 35

35 高速串行總線基本知識

并行總線之所以在高速傳輸上被串行總線取代的原因就在于:第一,系統(tǒng)時鐘的瓶頸;第二,總線間的串?dāng)_。要達到上Gbps的傳輸速率,對于并

2010-10-16 17:44:44 18

18 調(diào)試嵌入式系統(tǒng)設(shè)計中的低速串行總線(二)SPI背景知識串行外設(shè)接口總線(SPI)最初是摩托羅拉在20世紀(jì)80年代末為其68000 系列微控制器研制

2008-11-26 21:39:10 1045

1045

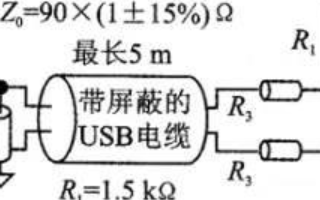

通用串行總線(USB)原理及接口設(shè)計

通用串行總線USB (Universal SerialBus)是Intel、Microsoft等大廠商為解決計算機外設(shè)種類的日

2009-04-11 18:41:45 2487

2487

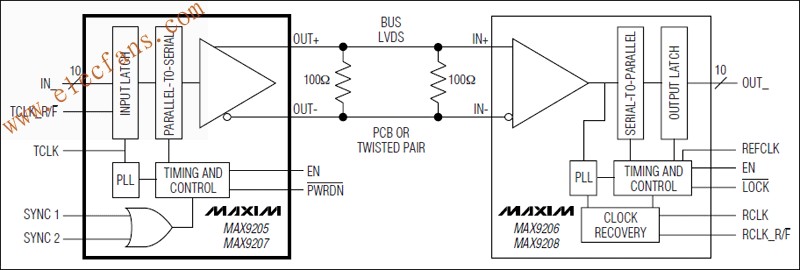

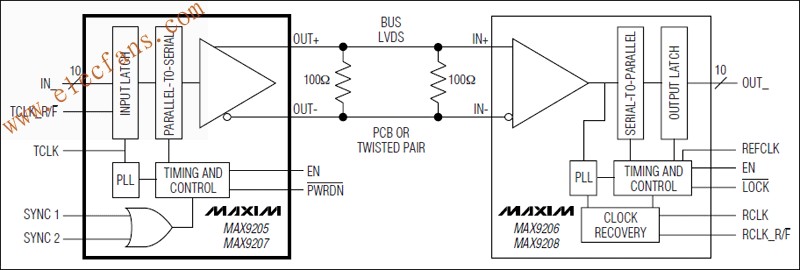

MAX9205/MAX9207串行器將10位寬度并行LVCMOS/LVTTL數(shù)據(jù)轉(zhuǎn)換為串行高速總線LVDS數(shù)據(jù)流。串行器與解串器配對使用,如MAX92

2010-12-21 09:57:06 1061

1061

隨著嵌入式技術(shù)的發(fā)展, 串行總線 技術(shù)也被越來越多的應(yīng)用于各個領(lǐng)域。為滿足用戶對特殊串行總線調(diào)試的需求,一些測試儀器廠商推出了具備自定義串行總線觸發(fā)和分析功能的示波

2011-10-06 14:10:31 2244

2244

串行總線的分析功能分為兩個部分,總線觸發(fā)和總線分析。DLM2000支持標(biāo)準(zhǔn)的CAN/LIN/I2C/SPI/UART總線觸發(fā)

2012-04-07 15:14:42 1430

1430

提出了利用12c總線擴展單片機的并行口的方法。對于不具有12C總線的單片機,可以利用其I/O口模擬來實現(xiàn)。

2012-04-13 15:11:17 8

8 基于FPGA的ARM并行總線研究與仿真

2017-01-24 16:54:24 19

19 基于FPGA和多DSP的多總線并行處理器設(shè)計

2017-10-19 13:40:31 4

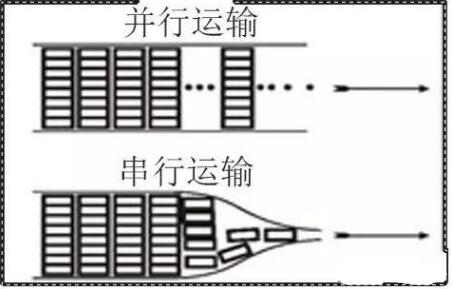

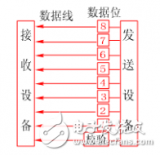

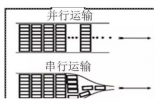

4 并行通信傳輸中有多個數(shù)據(jù)位,同時在兩個設(shè)備之間傳輸。發(fā)送設(shè)備將這些數(shù)據(jù)位通過 對應(yīng)的數(shù)據(jù)線傳送給接收設(shè)備,還可附加一位數(shù)據(jù)校驗位。串行數(shù)據(jù)傳輸時,數(shù)據(jù)是一位一位地在通信線上傳輸?shù)模扔删哂袔孜?b class="flag-6" style="color: red">總線的計算機內(nèi)的發(fā)送設(shè)備,將幾位并行數(shù)據(jù)經(jīng)并--串轉(zhuǎn)換硬件轉(zhuǎn)換成串行方式

2017-11-13 09:15:29 40722

40722

并行總線,就是并行接口與計算機設(shè)備之間傳遞數(shù)據(jù)的通道。采用 并行傳送方式在 微型計算機與 外部設(shè)備之間進行 數(shù)據(jù)傳送的接口叫并行接口。

2017-11-13 09:19:47 78731

78731 并行總線,就是并行接口與計算機設(shè)備之間傳遞數(shù)據(jù)的通道。采用并行傳送方式在 微型計算機與外部設(shè)備之間進行數(shù)據(jù)傳送的接口叫并行接口,它有2個主要特點;一是同時并行傳送的二進位數(shù)就是數(shù)據(jù)寬度;二是在計算機與外設(shè)之間采用應(yīng)答式的聯(lián)絡(luò)信號來協(xié)調(diào)雙方的數(shù)據(jù)傳送操作,這種聯(lián)絡(luò)信號又稱為握手信號。

2017-11-13 09:55:07 12563

12563

計算機通信方式可以分為并行通信和串行通信,相應(yīng)的通信總線被稱為并行總線和串行總線。并行通信速度快、實時性好,但由于占用的口線多,不適于小型化產(chǎn)品;而串行通信速率雖低,但在數(shù)據(jù)通信吞吐量不是很大的微處理電路中則顯得更加簡易、方便、靈活。

2017-11-13 17:26:33 25478

25478

I2C總線在物理連接上非常簡單,分別由SDA(串行數(shù)據(jù)線)和SCL(串行時鐘線)及上拉電阻組成。通信原理是通過對SCL和SDA線高低電平時序的控制,來產(chǎn)生I2C總線協(xié)議所需要的信號進行數(shù)據(jù)的傳遞。在總線空閑狀態(tài)時,這兩根線一般被上面所接的上拉電阻拉高,保持著高電平。

2017-12-06 10:48:01 3087

3087

另外,從廣義上說,計算機通信方式可以分為并行通信和串行通信,相應(yīng)的通信總線被稱為并行總線和串行總線。并行通信速度快、實時性好,但由于占用的口線多,不適于小型化產(chǎn)品;而串行通信速率雖低,但在數(shù)據(jù)通信吞吐量不是很大的微處理電路中則顯得更加簡易、方便、靈活。串行通信一般可分為異步模式和同步模式。

2018-06-05 16:08:00 3755

3755

通信及與外部世界通信。然而今天,嵌入式系統(tǒng)設(shè)計中使用的越來越多的構(gòu)件將用串行總線代替并行總線,這也給嵌入式系統(tǒng)設(shè)計人員帶來了重大挑戰(zhàn)。本文討論了嵌入式系統(tǒng)設(shè)計人員的常用挑戰(zhàn),及怎樣使用示波器中的功能來解決這些挑戰(zhàn)。 在并行結(jié)構(gòu)中,總線的每個

2018-01-25 15:33:36 1

1 并行總線波形捕獲與分析。

2018-06-25 15:44:00 3560

3560 本文檔的主要內(nèi)容詳細介紹的是PCB設(shè)計有哪些誤區(qū)PCB設(shè)計的十大誤區(qū)下部分主要內(nèi)容包括了:1.時序及等長設(shè)計概述,2.共同時鐘并行總線時序設(shè)計,3.源同步時鐘并行總線時序設(shè)計,4.高速串行總線時序設(shè)計,5.時序及等長設(shè)計總結(jié)

2019-01-07 08:00:00 0

0 做PCB設(shè)計的都知道,沒有一點高速方面的知識,你就不是一個有經(jīng)驗的PCB設(shè)計工程師。高速信號常見于各類的串行總線與并行總線,只有你知道是什么總線,你還得知道它跑多快,才能開始進行布線。

什么是串行總線,什么是并行總線?

2019-02-05 11:37:00 2171

2171

等長走線的目的就是為了盡可能的減少所有相關(guān)信號在 PCB 上的傳輸延遲的差異。至于 USB/SATA/PCIE 等串行信號,并沒有上述并行總線的時鐘概念,其時鐘是隱含在串行數(shù)據(jù)中的。數(shù)據(jù)發(fā)送方將時鐘

2019-04-26 15:27:25 10423

10423

常用的串行擴展總線有:I2C總線,SPI總線,單總線,Microwire/PLUS。

I2C串行總線概述I2C串行總線,是具備多主機系統(tǒng)所需的包括總線裁決和高低速器件同步功能的高性能串行總線。

2019-07-31 17:35:00 6

6 等串行總線接口只能實現(xiàn)FPGA 和ARM 之間的低速通信 ;當(dāng)傳輸?shù)臄?shù)據(jù)量較大.要求高速傳輸時,就需要用并行總線來進行兩者之間的高速數(shù)據(jù)傳輸.

2019-08-08 15:37:50 5863

5863

計算機之間、計算機與遠程終端、計算機與外部設(shè)備以及計算機與測量儀器儀表之間的通信。該類總線不是計算機系統(tǒng)已有的總線,而是利用電子工業(yè)或其他領(lǐng)域已有的總線標(biāo)準(zhǔn)。外部總線又分為并行總線和串行總線,并行總線主要有IEEE-488總線,串行總線主要有RS232C、RS422

2020-03-21 10:41:20 4032

4032

按照傳輸數(shù)據(jù)的方式劃分,可以分為串行總線和并行總線。串行總線中,二進制數(shù)據(jù)逐位通過一根數(shù)據(jù)線發(fā)送到目的器件;并行總線的數(shù)據(jù)線通常超過2根。常見的串行總線有SPI、I2C、USB及RS232等。

2020-08-25 14:13:14 5785

5785 在PCB設(shè)計中,等長走線主要是針對一些高速的并行總線來講的。 由于這類并行總線往往有多根數(shù)據(jù)信號基于同一個時鐘采樣,每個時鐘周期可能要采樣兩次(DDRSDRAM)甚至4次,而隨著芯片運行頻率的提高

2020-10-24 09:29:38 8605

8605 作為一名PCB設(shè)計工程師,具備一些高速方面的知識是非常有必要的,甚至說是必須的。就信號來說,高速信號通常見于各種并行總線與串行總線,只有知道了什么是總線,才能知道它跑多快,才能開始進行布線。

2020-10-21 14:14:21 4413

4413

CANopen是一個基于CAN(控制局域網(wǎng))串行總線系統(tǒng)和CAL(CAN應(yīng)用層)的高層協(xié)議。

2021-01-22 09:56:49 21917

21917

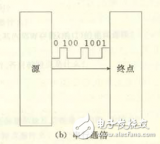

選擇“串行”還是“并行”呢? 在討論這個問題之前,我們先來了解下什么是串行總線,什么是并行總線? 對于串行總線,并行總線,從字面意義你就知道個大概了。串行就是數(shù)據(jù)是一位一位的發(fā)送,并行就是數(shù)據(jù)一組一組的發(fā)送。如下圖

2021-04-04 14:33:00 2405

2405

微處理器中常用的集成串行總線是通用異步接收器傳輸總線(UART)、串行通信接口(SCI)和通用串行總線(USB)等,這些總線在速度、物理接口要求和通信方法學(xué)上都有所不同。

2021-05-31 09:06:55 2478

2478

早些年的老式設(shè)備都采用并行傳輸,而現(xiàn)在的設(shè)備都采用串行傳輸。為什么并行傳輸會被串行傳輸所取代呢?

2021-06-11 15:19:49 16154

16154 串行總線技術(shù)(一)-串行總線結(jié)構(gòu)(以PCIe為例)串行總線的出現(xiàn)在早期的計算機系統(tǒng)中,多數(shù)外圍設(shè)備使用并行總線結(jié)構(gòu)。這些總線包括PCI和PATA(并行ATA)。當(dāng)通信速率較低時,并行總線結(jié)構(gòu)可以

2021-10-15 10:10:26 7445

7445 書接上回-《串行總線技術(shù)(一)-串行總線結(jié)構(gòu)(以PCIe為例)》《串行總線技術(shù)(二)-串行總線中的先進設(shè)計理念及SerDes/PMA介紹》,今天詳解SATA協(xié)議。 簡介SATA(Serial

2021-11-01 10:53:58 8354

8354 IIC總線協(xié)議及應(yīng)用I2C總線知識I2C總線物理拓撲結(jié)構(gòu)I2C總線特征I2C總線協(xié)議I2C總線操作IIC總線應(yīng)用案例I2C總線知識I2C總線物理拓撲結(jié)構(gòu)I2C 總線在物理連接上非常簡單,分別由SDA

2021-11-20 15:21:01 10

10 按照傳輸數(shù)據(jù)的方式劃分,可以分為串行總線和并行總線。串行總線中,二進制數(shù)據(jù)逐位通過一根數(shù)據(jù)線發(fā)送到目的器件;并行總線的數(shù)據(jù)線通常超過2根。常見的串行總線有SPI、I2C、USB及RS232等。

2022-12-22 14:08:59 700

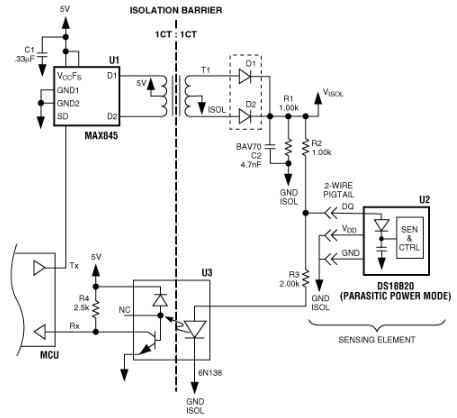

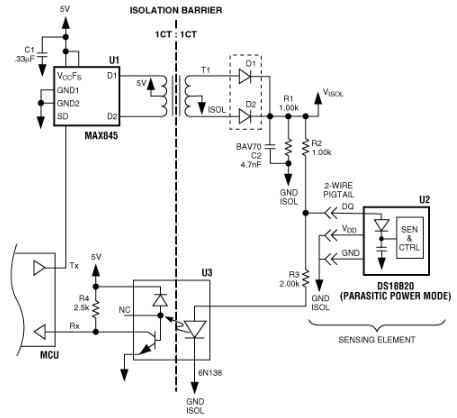

700 醫(yī)療和工業(yè)應(yīng)用通常需要 2500VAC 或更高的電氣隔離,以確保患者和設(shè)備操作員的安全。隔離柵不僅向傳感元件傳輸電源,還向該元件傳輸數(shù)據(jù)或從該元件傳輸數(shù)據(jù)。每個跨越屏障的數(shù)據(jù)信號都需要隔離,因此在這些應(yīng)用中,通常通過選擇串行總線而不是并行總線來節(jié)省成本。串行總線包括 SPI、I2C和達拉斯1-Wire總線。

2023-02-07 13:49:34 910

910

I2C串行總線協(xié)議是什么?I2C總線有哪些優(yōu)點? I2C(Inter-Integrated Circuit)是一種串行總線協(xié)議,由Philips(現(xiàn)為NXP Semiconductors公司

2023-09-12 11:18:17 728

728 從以太網(wǎng)到高速串行總線,pcb絕緣阻抗標(biāo)準(zhǔn)指南

2023-09-19 10:48:33 589

589 電子發(fā)燒友網(wǎng)站提供《基于FPGA的ARM并行總線設(shè)計原理.pdf》資料免費下載

2023-10-10 09:31:31 0

0 并行總線和串行總線的區(qū)別? 并行總線和串行總線是計算機系統(tǒng)中常見的兩種數(shù)據(jù)傳輸方式,它們有著不同的工作原理和應(yīng)用場景。在這篇文章中,我將詳細介紹并行總線和串行總線的區(qū)別,并探討它們各自的優(yōu)勢和劣勢

2023-12-07 16:45:27 1519

1519

電子發(fā)燒友App

電子發(fā)燒友App

評論