總線空閑狀態(tài) I2C總線總線的SDA和SCL兩條信號線同時處于高電平時,規(guī)定為總線的空閑狀態(tài)。此時各個器

2017-11-21 15:09:05 24156

24156

上一篇文章簡單講解了什么是AMBA總線,簡單來說,AMBA總線是一系列協(xié)議。定義了適用于不同場景的總線家族。今天我們就來將AMBA總線中最簡單的APB總線。

2024-01-02 11:37:04 773

773

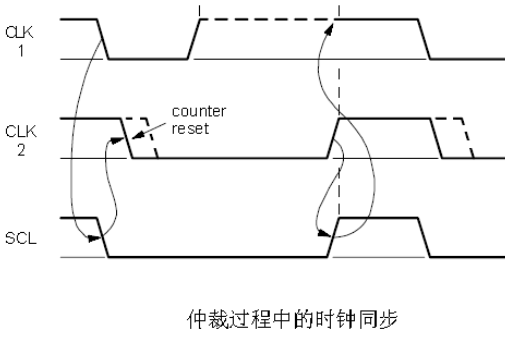

I2C總線在嵌入式系統(tǒng)中很常見,今天就來給大家講講I2C總線的時序。

2024-02-23 09:47:10 523

523

本帖最后由 mr.pengyongche 于 2013-4-30 02:59 編輯

16550兼容的UART,可以連接APB總線[url=www.0404.cc]

2012-08-10 18:10:18

APB (advanced peripheral bus) 外圍設備總線一、DMA介紹1、DMA傳輸主要特性具有12個獨立的可配置的通道(請求)。支持存儲器及存儲器間的傳輸,外設與存儲器、存儲器

2021-08-20 07:05:32

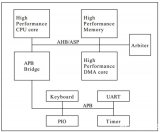

一、概括 首先,說點不靠譜的,APB和AHB總線,我個人感覺這個類似于個人PC系統(tǒng)里的北橋和南橋總線。 南橋總線上掛接的都是鼠標、鍵盤這些慢速的設備,北橋上掛接顯卡等高速設備。南橋頻率低,北橋頻率高

2021-08-20 06:18:24

一、概括首先,說點不靠譜的,APB和AHB總線,我個人感覺這個類似于個人PC系統(tǒng)里的北橋和南橋總線。南橋總線上掛接的都是鼠標、鍵盤這些慢速的設備,北橋上掛接顯卡等高速設備。南橋頻率低,北橋頻率高

2021-08-23 07:34:30

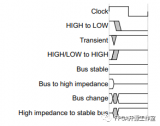

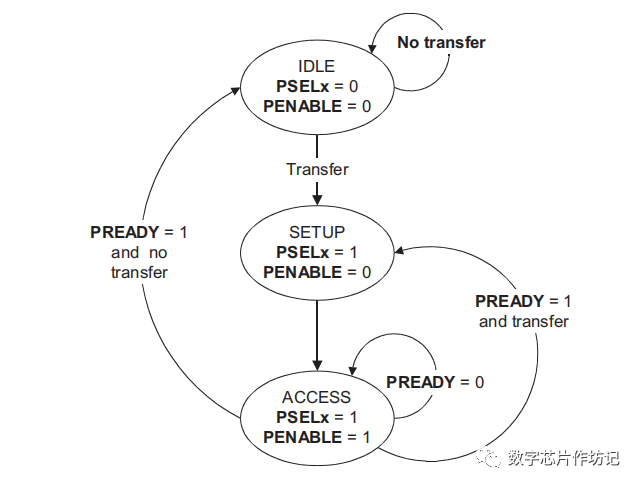

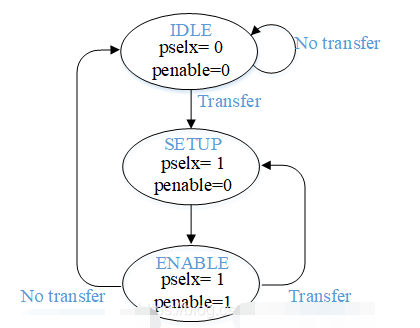

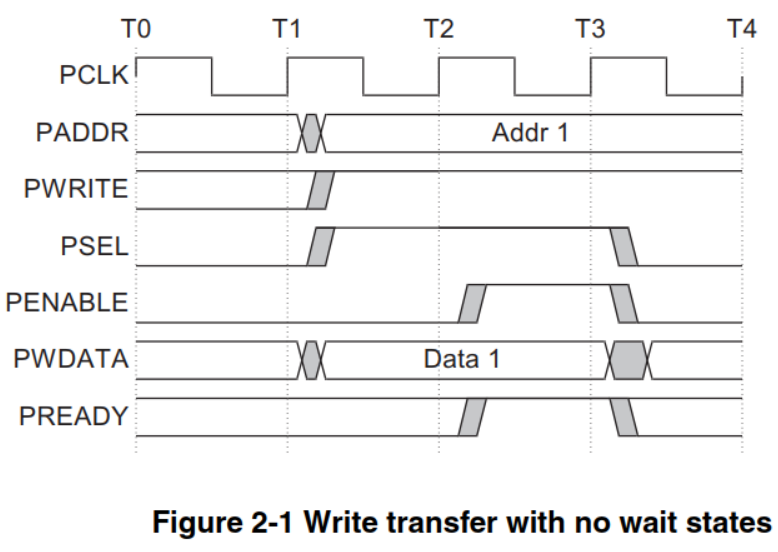

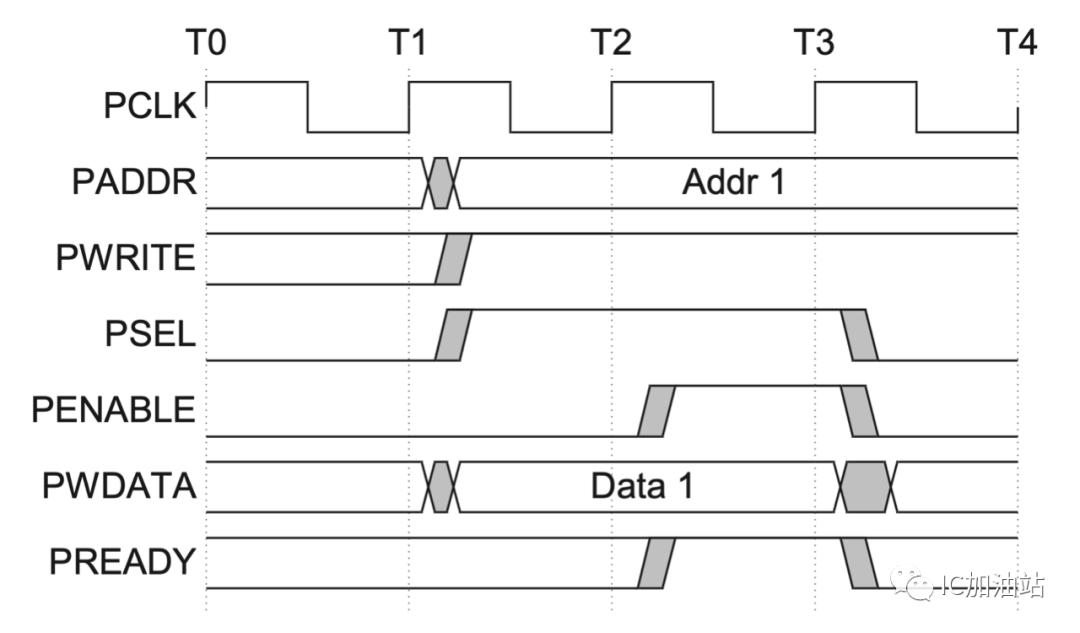

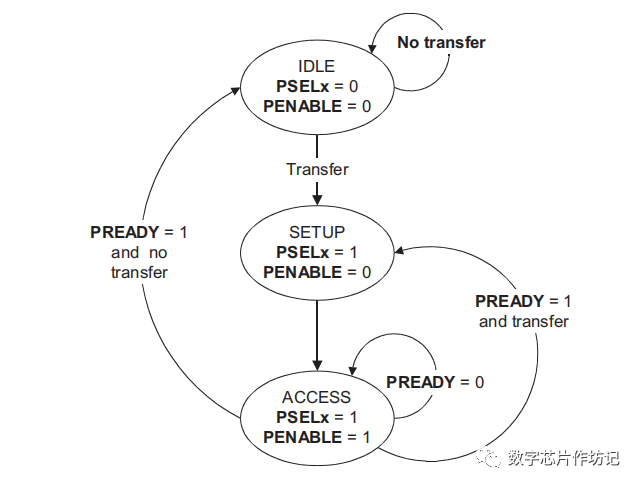

PREADY拉低,則讀傳輸會延長。下圖是AMBA APB的工作流程IDLE - 這是APB的默認狀態(tài)。SETUP- 當需要傳輸時,總線進入SETUP狀態(tài),其中相應的選擇信號PSELx被置位。 總線僅在

2022-04-07 10:18:24

信號傳輸總線技術分類按傳輸信息種類:總線可分為數(shù)據(jù)總線DB(DataBus),地址總線(AddressBUs),控制總線(ControlBus)按數(shù)據(jù)傳輸方式:并行總線(每個信號都有自己的信號

2022-02-16 07:53:28

1、AHB傳輸的時序圖分析正文1:AHB章節(jié)最后再復習一遍多主機的概念:總線是被總線上所有的部件所共享的一組通路(連線),對于支持多主機的總線,如果某一個主機想要與其他的部件進行通信(獲得

2022-06-09 17:45:33

HBUSREQ 信號為高一直到突發(fā)傳輸中的最后一次傳輸的地址傳輸相位發(fā)起之后。這將意味著如果倒數(shù)第二次傳輸是一個零等待狀態(tài),那么主設備可能會在未定義長度突發(fā)傳輸之后還被授予總線都多一次額外的傳輸。對于定長

2022-06-08 16:20:29

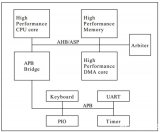

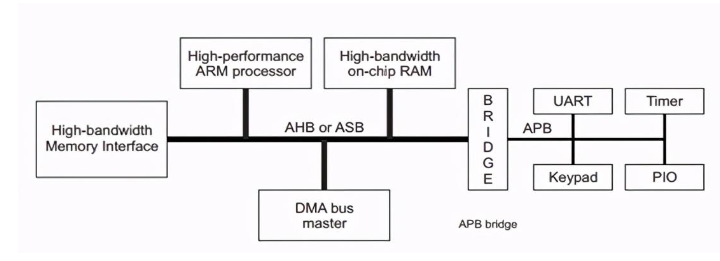

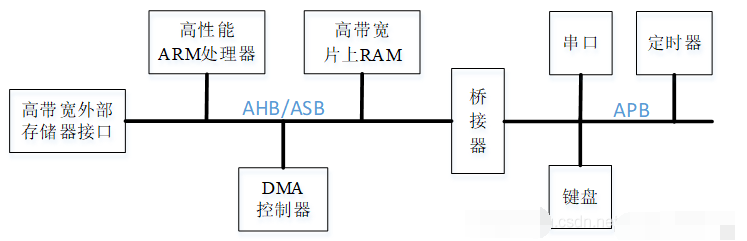

AMBA 2.0規(guī)范包括四個部分:AHB、ASB、APB和Test Methodology。AHB的相互連接采用了傳統(tǒng)的帶有主模塊和從模塊的共享總線,接口與互連功能分離,這對芯片上模塊之間的互連具有重要意義。AMBA已不僅是一種總線,更是一種帶有接口模塊的互連體系。

2019-10-17 08:05:22

1、AHB系統(tǒng)總線分為APB1(36MHz)和APB2(72MHz),其中2>1,意思是APB2接高速設備;2、Stm32f10x.h相當于reg52.h(里面有基本的位操作定義

2021-08-05 07:13:06

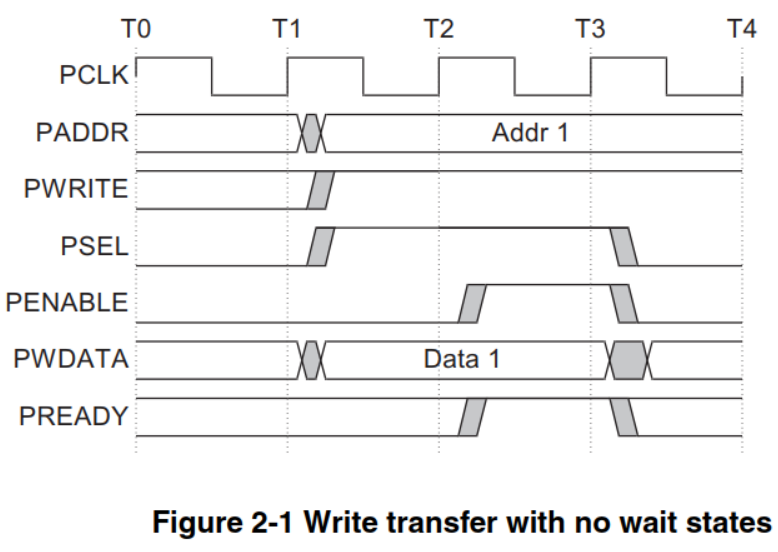

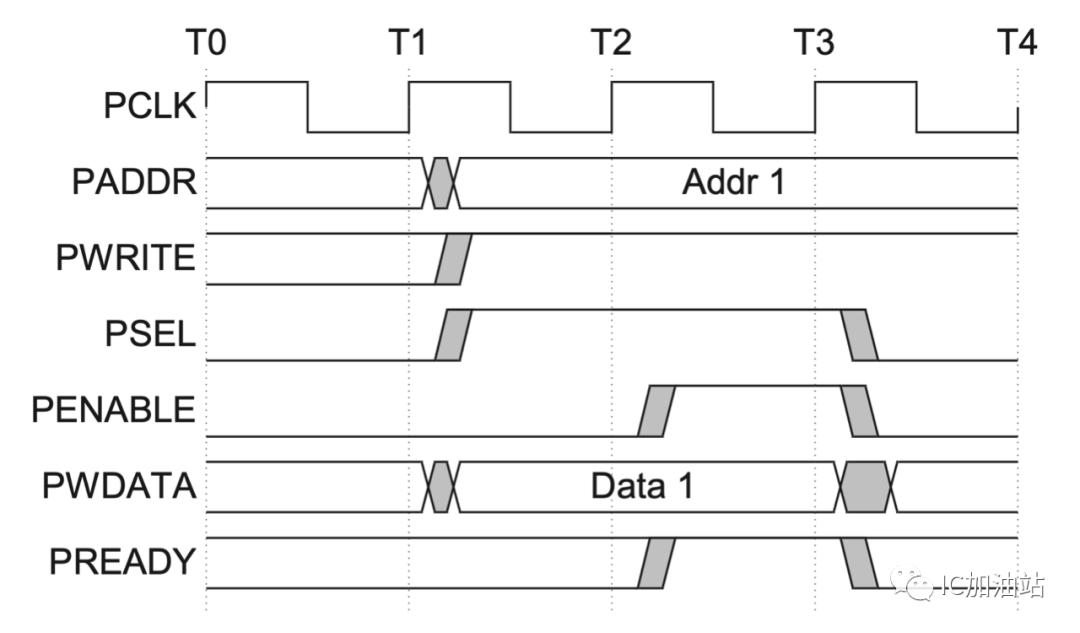

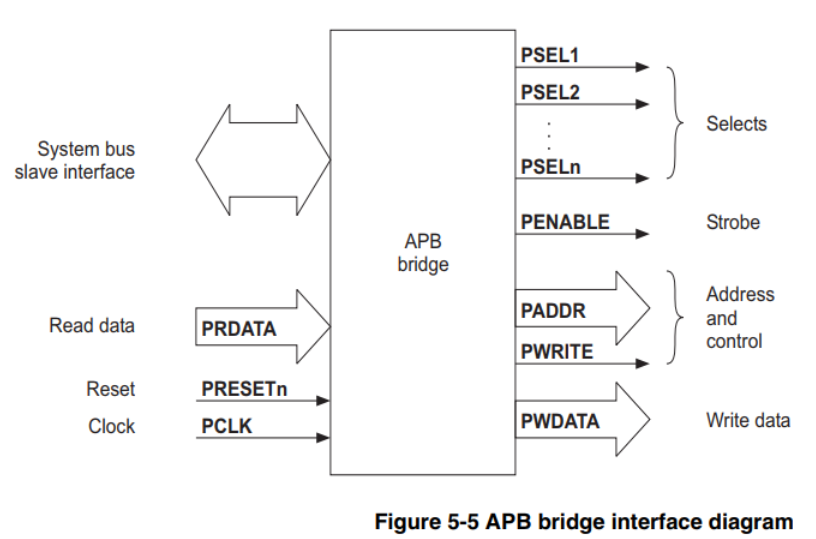

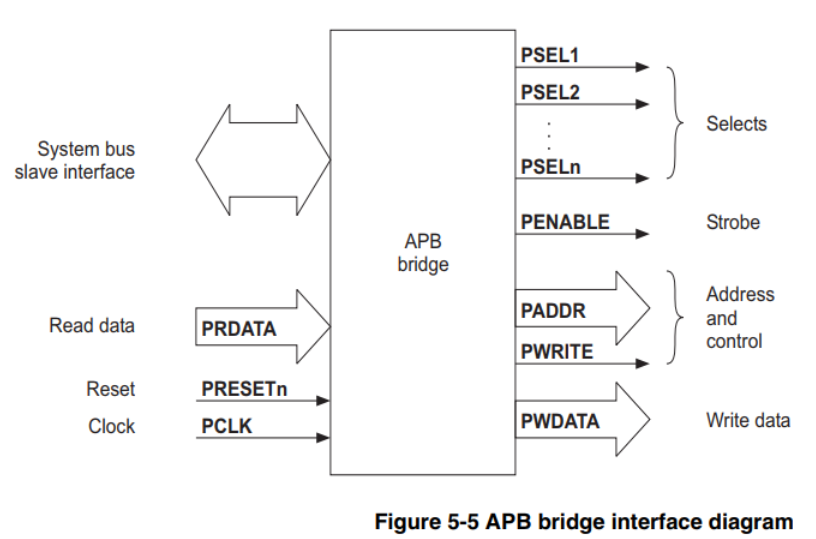

有效。 PADDR 地址總線。 PSELx 從設備選擇。 PENABLE APB傳輸選通。 PWRITE 高為寫傳輸,低為讀。 PRDATA 讀數(shù)據(jù)總線。 PWDATA 寫數(shù)據(jù)總線。 接口信號定義如下:

2022-04-07 10:03:19

STM32菜鳥學習手冊——1、AMBA、APB、AHB簡介芯片上總線標準種類繁多,而由ARM公司推出的AMBA片上總線受到了廣大IP開發(fā)商和SoC系統(tǒng)集成者的青睞,已成為一種流行的工業(yè)標準片上結(jié)構

2022-02-17 07:18:33

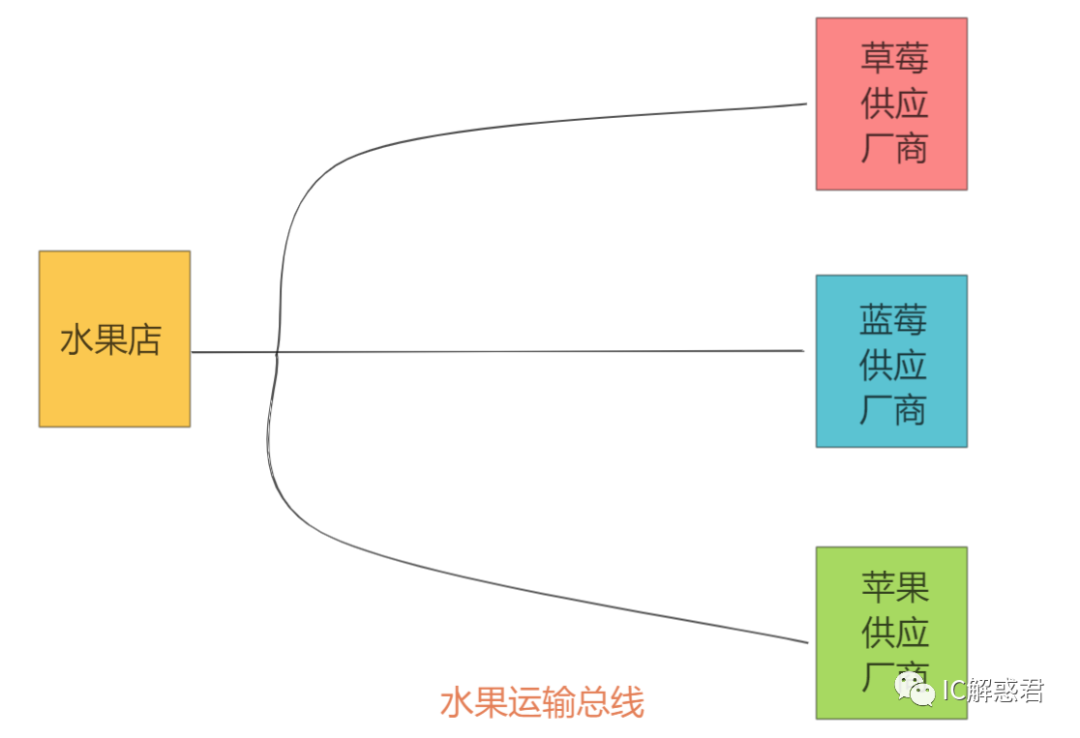

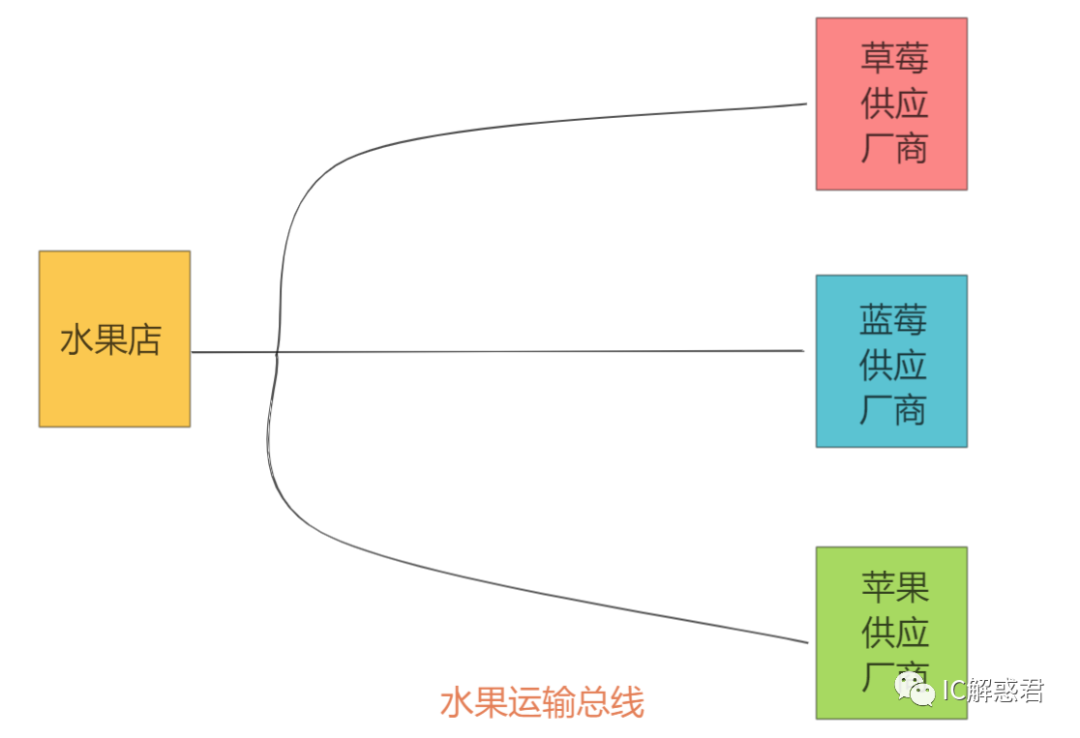

1、漫談AMBA總線-APB首先考慮一下以下的場景:概念1: 主機(Master)訂單的發(fā)起只能由水果店發(fā)起,所以水果店在這條水果運輸總線里面運輸水果占有主動地位。類比:在APB總線里面,數(shù)據(jù)的傳輸

2022-06-07 16:14:15

, ASB, APB);Qchannel文章目錄1 AMBA總線2 AHB2.1 一個典型的基于AHB的微控制器2.2 AHB總線互聯(lián)結(jié)構:中心選擇器連接master與slave2.3 AHB的特性3 APB4 AHB和APB的區(qū)別與聯(lián)系4 Q-channel1 AMBA總線內(nèi)容來源:維基百科詞條-Ad.

2022-02-09 07:46:07

通過足夠的空閑時間(“相位緩沖段”)來補償。 由于CAN協(xié)議使用非破壞性的位總線仲裁和顯性應答位,信號從發(fā)送器傳輸到接收器再返回到接收器必須在一個位時間內(nèi)完成。因此除了保留用于同步的時間外,還需要

2016-08-15 15:59:45

CS1237無法正常讀配置和寫配置問題。圖1讀配置時序圖,如附件所示。圖2單片機管腳未連接AD芯片,時序圖。通過對比兩個時序,發(fā)現(xiàn)數(shù)據(jù)總線被AD芯片強制拉低了。這種芯片使用時,需要主控芯片有推挽輸出模式強制拉高總線,弱上拉類型芯片該如何使用這個芯片??

2020-11-27 10:18:20

關于對DHT11單總線時序圖的理解最近上網(wǎng)買了一個單總線的DHT11溫濕度傳感器,看了一些代碼,這是自己的理解,并記錄。DHT11數(shù)字溫濕度傳感器資料DHT11數(shù)字溫濕度傳感器是一款含有已校準

2022-02-16 07:03:14

。啟動信號 在時鐘線SCL保持高電平期間,數(shù)據(jù)線SDA上的電平被拉低(即負跳變),定義為I2C總線總線的啟動信號,它標志著一次數(shù)據(jù)傳輸的開始。啟動信號是一種電平跳變時序信號,而不是一個電平信號。啟動信號

2018-06-14 15:00:51

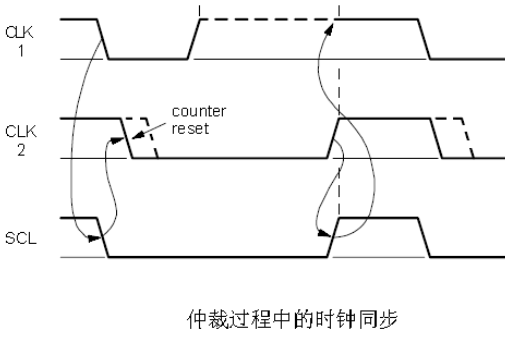

物理層的連接可以說是非常簡單,這也是它最大的優(yōu)勢,原理就是通過控制SDA和SCL線的高低電平時序,來產(chǎn)生I2C總線協(xié)議所需要的信號進行數(shù)據(jù)傳輸。在總線處于空閑狀態(tài)時SCL和SDA被上拉電阻拉高,保持高電平

2020-08-25 11:16:05

0x01:iic簡介I2C(Inter-Integrated Circuit)總線是由 PHILIPS 公司開發(fā)的兩線式==串行總線==,用于連接微控制器及其外圍設備。I2C 總線只有兩根雙向信號

2022-07-04 11:23:01

配合實現(xiàn),傳輸速率包含標注準(100kps)、快速(400kps)、高速(3.4Mbps)三大類。2. IIC總線時序啟動時序:當SCL為高電平時,SDA下降沿,表示啟動。...

2021-11-29 06:20:06

IIC時序理解IIC 的特征:兩條總線:串行數(shù)據(jù)總線(SDA)和串行時鐘總線(SCL)數(shù)據(jù)有效性規(guī)定:IIC總線在進行數(shù)據(jù)傳輸時,SCL在高電平區(qū)間,SDA上的電平必須保持穩(wěn)定SDA的數(shù)據(jù)的高或者

2022-01-07 06:05:52

時序圖7.0 ISA信號用法8.0 ISA連接器引腳9.0 PC/104總線連接引腳[hide][/hide]

2009-05-25 01:13:56

IN:復位信號。用來迫使所有PCI專用的寄存器、定序器和信號轉(zhuǎn)為初始狀態(tài)。2.地址和數(shù)據(jù)信號 AD[31::00]T/S:地址、數(shù)據(jù)復用的信號。PCI總線上地址和數(shù)據(jù)的傳輸,必需在FRAME#有效期間進行

2012-04-06 14:37:24

了可連到總線上的器件數(shù)量。3、SPI時序分析在SPI傳輸中,數(shù)據(jù)是同步進行發(fā)送和接收的。數(shù)據(jù)傳輸的時鐘基于來自主處理器的時鐘脈沖,摩托羅拉沒有定義任何通用SPI的時鐘規(guī)范。然而,最常用的時鐘設置

2011-10-18 10:27:05

的128*64的OLED顯示屏為例。下圖為OLED的外觀圖。二、SSD1306芯片的IIC時序圖這里我們需要看清楚START信號和STOP信號。關于時間,芯片的數(shù)據(jù)手冊也有說明。...

2022-02-18 07:09:46

/APB1橋后就可以訪問APB1各類外設,而TIM5就是掛在APB1總線上的外設之一。咨詢者的問題基本上靠看上面幾幅圖可以得到答案。這些圖很重要,很多信息用圖描述也很直觀明了。各技術手冊里的插圖往往大有

2021-05-16 06:00:00

以下是USB底層信號的一些定義及時序圖,雖然很簡潔,但能理解后,對后續(xù)的USB學習是很有幫助的,特推薦給大家!BTW,本月(4月20號周六)在深圳有一場很接地氣、很容易入門的USB線下、小型技術交流

2019-04-08 16:30:26

詳解-SPI接口在模式0下輸出第一位數(shù)據(jù)的時刻 SPI接口在模式0下輸出第一位數(shù)據(jù)的時刻 SPI接口有四種不同的數(shù)據(jù)傳輸時序,取決于CPOL和CPHL這兩位的組合。圖1中表現(xiàn)了這四種時序, 時序

2018-07-06 07:24:25

9-7 所示。? 同步段:在這段時間內(nèi),完成總線上各個節(jié)點的同步,需要一個跳變沿。? 傳播段:這個時間段是指網(wǎng)絡上傳輸的延遲時間,它是信號在總線上傳播時間、輸入比較器延遲和輸出驅(qū)動器延遲之和的兩倍

2018-12-17 11:13:33

是APB2總線(2)通用定時器timer2timer5,通用定時器timer12timer14以及基本定時器timer6,timer7的時鐘來源是APB1總線從STM32F4的內(nèi)部時鐘樹可知,當

2021-08-12 07:46:29

LCD1602的數(shù)據(jù)控制時鐘信號,利用該信號的上升沿實現(xiàn)對LCD1602的數(shù)據(jù)傳輸。7~14腳:8位并行數(shù)據(jù)口,使得對LCD1602的數(shù)據(jù)讀寫大為方便。現(xiàn)在來看LCD1602的操作時序:在此,我們可以先

2017-12-13 14:47:53

,即執(zhí)行一條指令所需的機器周期。三、時序單片機時序是指單片機執(zhí)行指令時應發(fā)出的控制信號的時間序列。這些控制信號在時間上的相互關系就是CPU的時序。它是一系列具有時間順序的脈沖信號。CPU發(fā)出的時序有兩類

2018-07-21 16:38:31

是INTEL總線,6800總線也就是MOTOROLA總線。從這兩個時序圖上,我們看到的區(qū)別恐怕主要是讀寫選通的區(qū)別。INTEL總線分別使用讀選通信號RD#和寫選通信號WR#兩個信號的低電平狀態(tài)來表示當前處于

2016-11-26 17:10:43

,然后開始傳輸。解碼器對放置在總線上的地址進行解碼,并選擇一個從機。從站將響應發(fā)回主站,然后進行數(shù)據(jù)傳輸。圖3.AHB信號與ASB信號的比較先進的外圍總線APB是用于低頻系統(tǒng)組件的簡化接口。修訂版2通過

2020-09-28 10:16:11

APB slave模塊只是對一些控制和狀態(tài)寄存器進行讀寫,是無等待傳輸,同時不生成傳輸錯誤信號。對不同的寄存器做了地址分配,其中status32寄存器只讀然后我們在Testbench里例化APB slave和一個APB master 模型,對該APB slave模塊進行驗證。

2022-04-07 10:10:03

十分嚴重注意的是,時序圖里各個引腳的電平變化,基于的時間軸是一致的。一定要嚴格按照時間軸的增長方向來精確地觀察時序圖。要讓器件嚴格的遵守時序圖的變化。在類似于18B20這樣的單總線器件對此要求尤為嚴格

2014-05-05 21:04:09

UART內(nèi)部可劃分為哪幾個模塊?這些模塊有什么功能?基于APB總線的UART接口軟核該如何去設計?

2021-06-18 08:20:15

訪問不支持突發(fā)傳輸,總線時序和情形(3)一致;而內(nèi)存訪問支持突發(fā)傳輸,情形(3)和(4)的時序均會出現(xiàn)。用戶應用可以通過Ready和Term信號不同的輸入組合來控制狀態(tài)機的狀態(tài)轉(zhuǎn)移,如表4所示。但是在

2019-05-29 05:00:02

實時信號處理的需要,用FPGA實現(xiàn)了多DSP信號處理模板局部總線和基于標準VME總線的計算機進行通信的接口設計。 2 VME總線的功能特點 VME總線系統(tǒng)的功能結(jié)構可以分為4類:數(shù)據(jù)傳輸總線(DTB

2019-04-15 07:00:07

問個問題,拿過來一個芯片datasheet,怎么由它的時序圖把程序?qū)懗鰜恚?我看過一些芯片的時序圖,懂是可以懂得,但再看程序,里面定義了很多函數(shù),向I2C總線結(jié)構的程序,還有開啟和關閉I2C,類似這種。。。能否只從時序圖直接寫出它的程序? 路過的朋友可以探討下并留下你的寶貴建議,謝謝。

2013-12-17 10:10:57

對Bank進行預充電,在此期間所有的Bank處于空閑狀態(tài)。預充電之后會有至少兩個自刷新,完成自刷新便可以對SDRAM進行模式寄存器配置。圖1 SDRAM初始化時序 SDRAM模式寄存器所控制的操作參數(shù):地址

2020-01-04 19:20:52

信號的上升沿實現(xiàn)對LCD1602的數(shù)據(jù)傳輸。7~14腳:8位并行數(shù)據(jù)口,使得對LCD1602的數(shù)據(jù)讀寫大為方便。LCD1602的操作時序這有兩個寫時序:① 若要寫指令字,設置LCD1602的工作方式

2019-01-01 22:29:38

想寫一個apb總線模型,時序也已經(jīng)完成,就是讀操作task這塊,給定義成輸入信號的prdata信號賦值時出錯,根本無法驅(qū)動該信號。寫了一個apb_bfm.v文件,外面沒有掛接任何設備。

2019-03-07 12:30:53

要用verilog寫一個APB總線,在這個上面掛載一個串口,現(xiàn)在有個疑問,APB總線時鐘比較快,而串口的發(fā)送速率比較慢,那么在APB總線完成一次執(zhí)行的話,兩個的速度要怎么匹配呢?例如:APB三個狀態(tài)

2019-01-22 23:57:10

我已經(jīng)了解到proteus中VSM Logic Analyser 可以同時分析多個端口的電平變化,但總線周期時間太短,即便只有一條指令,也包含許多總線周期,如何才能 記錄下總線周期內(nèi)各個端口的電平變化,得到時序圖?

2015-03-13 19:42:47

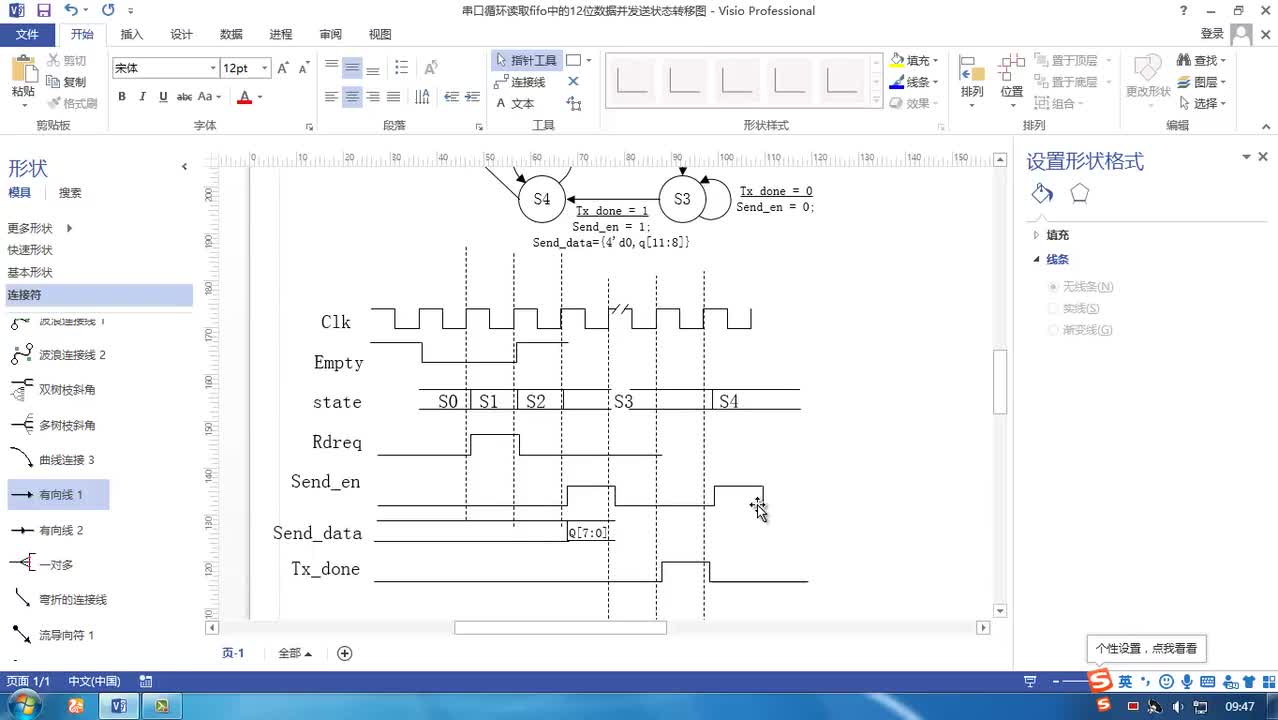

數(shù)據(jù),是不是肯定會出現(xiàn)fifo為空的情況,這時候需要等待一段時間,直到fifo給APB總線發(fā)送了可讀信號,APB總線才能夠讀取數(shù)據(jù)。那么問題是:APB執(zhí)行過程只有兩個周期,只要APB總線發(fā)生讀操作,fifo很快就會空了,那么fifo要如何工作,才能最大的優(yōu)化uart和APB總線之間的連接呢?

2019-02-12 00:43:19

高速電路信號完整性分析與設計—時序計算引入:在數(shù)字電路中,從一個芯片發(fā)信息A到另一個芯片變成信息B,那么這個數(shù)字系統(tǒng)失敗;如何保證信息不變?關鍵點,就是在傳輸過程的任意點都保持時序的正確性。時序概念

2009-09-12 10:28:42

ISA總線信號時序簡介:1.0 ISA概況2.0 ISA文獻2.1 ISA規(guī)范2.2 ISA書籍3.0 ISA結(jié)構形式4.0 PC/104結(jié)構形式5.0 ISA信號描述6.0 ISA時序圖7.0 ISA信號用法8.0 ISA連接器引腳

2009-05-21 11:06:54 242

242 PCI總線傳輸的終止方式探析:探討了PCI 總線傳輸的終止方式。PCI 總線的主設備和目標設備都可以終止PCI 傳輸。主設備和目標設備在終止一次傳輸的同時還以信號的電平組合告知主

2009-06-28 19:32:07 22

22 同步時序機狀態(tài)加全模擬是同步時序機反設計的關鍵步驟。因時序機狀態(tài)出現(xiàn)的頻率不同,模擬分析的時間不等,有的太長,難以滿足要求。本文在長期實踐基礎上提出了一種同步

2009-08-29 10:06:40 19

19 本文針對干涉成像光譜儀,詳細分析了干涉成像光譜信號特征及其時序關系,研究了干涉成像光譜數(shù)據(jù)傳輸系統(tǒng)的關鍵技術,提出了使用CPLD 技術,設計基于微機PCI 總線的干涉成像

2009-09-01 08:21:37 17

17 介紹一種通過光纖傳輸USB(通用串行總線)信號的電路。電路將USB(通用串行總線)信號D+、D一的三種狀態(tài)轉(zhuǎn)換為發(fā)射激光的三種強度全亮、半亮、暗,并且通過光纖傳輸到對方激光

2010-12-13 16:05:22 27

27

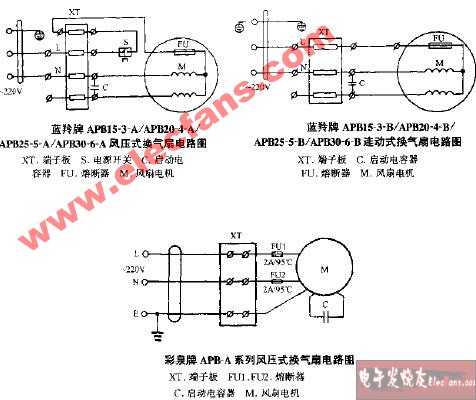

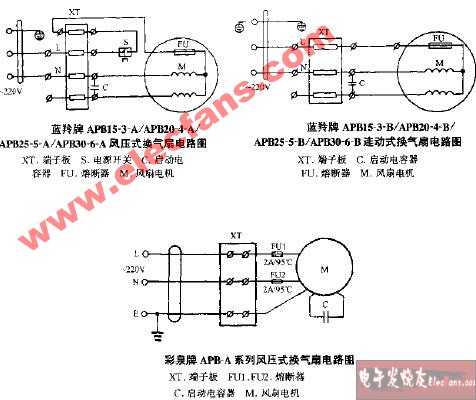

藍羚牌APB15-3-A APB20-4-A APB25-5-A APB30-6-A風壓式換氣扇電路圖

2009-02-27 21:22:22 1068

1068

藍羚牌APB15-3-B APB20-4-B APB25-5-B APB30-6-B連動式換氣扇電路圖

2009-02-27 21:22:54 1128

1128

探討了PCI 總線傳輸的終止方式。PCI 總線的主設備和目標設備都可以終止PCI 傳輸。主設備和目標設備在終止一次傳輸的同時還以信號的電平組合告知主設備其不同的終止狀態(tài)。主設備啟

2011-05-18 16:43:46 28

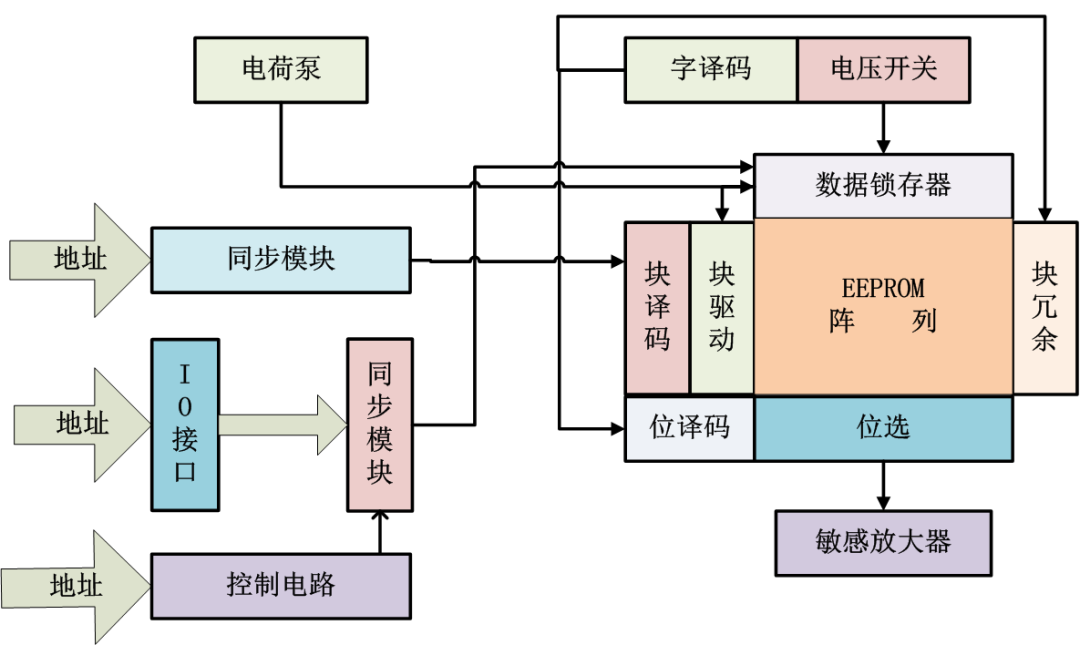

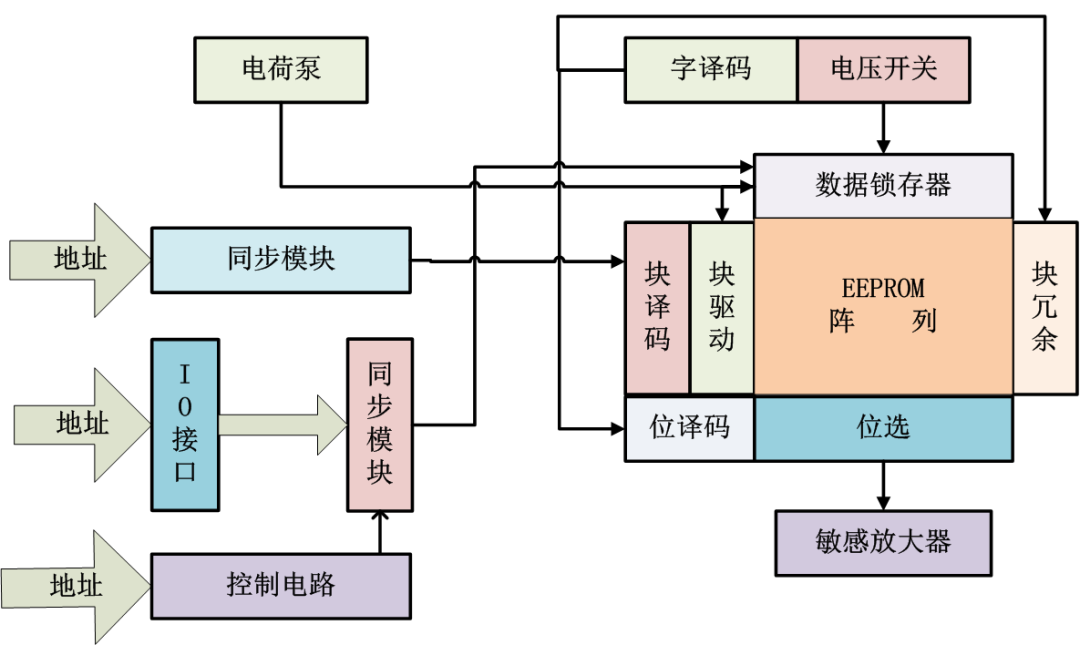

28 介紹了基于AMBA APB總線NandFlash控制器的設計,首先簡單介紹了NandFlash的一些特點,然后詳細介紹了NandFlash控制器的整體框架、具體功能及其內(nèi)部的數(shù)據(jù)通路。該控制器通過ModelSim進行了仿

2011-11-03 15:22:06 54

54 24C02中IIC總線的應答信號(ACK)時序圖分析,很好的單片機學習資料。

2016-03-21 17:30:06 93

93 I2C總線的結(jié)構、工作時序和模擬編程

2017-10-24 14:34:20 13

13 時序信號監(jiān)測設備主要用于飛行器火T品信號、時序指令等信號的監(jiān)測,是飛行器地面測試的重要組成部分。針對該設備對便攜性、可靠性要求較高的特點,采用基于PXI總線的測試技術的一體式設計,充分考慮各種故障

2017-11-07 10:10:07 13

13 介紹一種通過光纖傳輸USB(通用串行總線)信號的電路。電路將USB(通用串行總線)信號D+、D一的三種狀態(tài)轉(zhuǎn)換為發(fā)射激光的三種強度全亮、半亮、暗,并且通過光纖傳輸到對方激光接收器再經(jīng)相應電路恢復D+

2017-11-14 16:26:33 12

12 由主模塊、從模塊和基礎結(jié)構(Infrastructure)3部分組成,整個AHB總線上的傳輸都由主模塊發(fā)出,由從模塊負責回應。

2017-11-14 16:36:43 17155

17155

總線空閑狀態(tài):I2C總線總線的SDA和SCL兩條信號線同時處于高電平時,規(guī)定為總線的空閑狀態(tài)。此時各個器件的輸出級場效應管均處在截止狀態(tài),即釋放總線,由兩條信號線各自的上拉電阻把電平拉高。

2017-11-23 11:23:05 24558

24558

總線空閑狀態(tài) I2C總線總線的SDA和SCL兩條信號線同時處于高電平時,規(guī)定為總線的空閑狀態(tài)。此時各個器件的輸出級場效應管均處在截止狀態(tài),即釋放總線,由兩條信號線各自的上拉電阻把電平拉高。

2017-12-23 10:12:02 9395

9395

一個典型的基于AMBA 的微控制器同時集成AHB(或ASB )和APB 接口,如圖2 所示。ASB總線是舊版的系統(tǒng)的總線,而新版的AHB 總線增強了對性能、綜合及時序驗證的支持。APB 總線通常用作的局部的第二總線,作為AHB 或ASB 上的單個從屬模塊。

2018-08-10 09:45:10 6975

6975

如圖所示的電路為一能根據(jù)音頻信號的強弱控制八路時序輸出閃光狀態(tài)變化快慢的燈飾電路。

2019-12-22 10:15:58 2727

2727

由于CAN協(xié)議使用非破壞性的位總線仲裁和顯性應答位,信號從發(fā)送器傳輸到接收器再返回到接收器必須在一個位時間內(nèi)完成。

2020-03-21 11:23:39 2224

2224 總線就像一條公路,公路上的車好比總線上的電信號;公路的大小和車流量就決定了公路的車流量,故總線的位寬大小和傳輸頻率決定了一次傳輸中能夠提供的最大速度。常見的總線類型有:

2020-07-21 17:38:18 4526

4526 APB(AdvancedPeripheralBus)是AMBA(AdvancedMicrocontrollerBusArcheticture)總線體系的一部分。相較于AMBA總線體系中的其他總線,APB總線具有低功耗,低復雜度的特征。APB總線主要應用于對性能要求不太高的低帶寬外設接口。

2020-11-17 11:54:04 12017

12017

集成電路,設計一種基于可逆計數(shù)器的時序型總線硬件木馬。采用Xiix公司的ISE軟件在RTL層設計相應的RS232總線 Verilog代碼,并在常規(guī)和可逆時序型硬件木馬觸發(fā)閾值呈等差遞增的條件下進行 Modelsim仿真分析結(jié)果表明,在總線功能需求復雜和傳輸數(shù)

2021-03-19 17:19:26 34

34 電子發(fā)燒友網(wǎng)為你提供SPI總線協(xié)議介紹(接口定義,傳輸時序)資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-01 08:45:43 24

24 電子發(fā)燒友網(wǎng)為你提供STM32 APB1總線時鐘配置問題資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-19 08:51:53 7

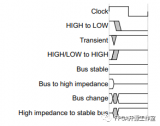

7 的,使用它連接到不需要 AXI 協(xié)議高性能的低帶寬外設。 APB 協(xié)議將信號轉(zhuǎn)換與時鐘的上升沿相關聯(lián),以簡化將 APB 外設集成到任何設計流程中的過程。每次傳輸至少需要兩個周期。APB 可能相連的接口: ? AMBA 高級高性能總線 (AHB) ? AMBA 高級高性能總線精簡版 (AHB-

2021-07-23 10:04:10 1911

1911

一、概括首先,說點不靠譜的,APB和AHB總線,我個人感覺這個類似于個人PC系統(tǒng)里的北橋和南橋總線。南橋總線上掛接的都是鼠標、鍵盤這些慢速的設備,北橋上掛接顯卡等高速設備。南橋頻率低,北橋頻率

2021-11-26 10:51:04 10

10 連接到總線都是SCL連到一起,SDA連到一起4、任何器件都可以拉低總線的電平IIC通信時序IIC通信時序可分成4個部分:1、開始信號:在SCL為高電平時,SDA產(chǎn)生一個下降沿2、數(shù)據(jù)傳輸:在SCL為低電平時,SDA可以變化;在SCL為高電平時,讀取SDA的狀態(tài)3、應答信號:先拉高SDA,然后拉

2021-12-04 16:06:09 12

12 的低帶寬外圍設備需要AXI協(xié)議的高性能。APB協(xié)議將信號轉(zhuǎn)換與時鐘上升沿相關聯(lián),以簡化將APB外圍設備集成到任何設計流程中。每次傳輸至少需要兩個周期。

2022-04-28 17:45:53 0

0 APB3是一個低功耗低成本接口。所有信號在時鐘上升沿傳輸,每次傳輸需要兩個時鐘周期。

2023-03-31 17:26:21 1397

1397

V1.0 ASB、APB是第一代AMBA協(xié)議的一部分。主要應用在低帶寬的外設上,如UART、 I2C,它的架構不像AHB總線是多主設備的架構,APB總線的唯一主設備是APB橋(與AXI或APB相連),因此不需要仲裁一些Request/grant信號。

2023-04-14 10:54:54 2764

2764 在APB總線里面,數(shù)據(jù)的傳輸只能由主機發(fā)起,其他部分響應主機操作。

2023-05-04 11:40:42 644

644

之前老李問過大家想看哪方面的知識,有不少同學提議老李寫寫總線,特別是AMBA的總線,所以老李決定從這期開始開始一個AMBA總線介紹的系列文章。AMBA總線主要包括三種最常見的協(xié)議APB, AHB

2023-05-04 14:53:12 1843

1843

實現(xiàn)一個在ARM中通過APB總線連接的UART模塊(Universal Asynchronous Receiver/Transmitter),包括設計與驗證兩部分。

2023-06-05 11:48:38 953

953

APB(Advanced Peripheral Bus),外圍總線的意思。該總線協(xié)議是ARM公司提出的AMBA總線結(jié)構之一,幾乎已成為一種標準的片上總線結(jié)構。

2023-06-05 15:10:39 1036

1036

高級外設總線 (APB) 是高級微控制器總線架構 (AMBA) 協(xié)議系列的一部分。它定義了一個低成本接口,該接口針對最低功耗和降低的接口復雜性進行了優(yōu)化。

2023-09-07 09:55:35 607

607

CAN總線是數(shù)字信號?還是模擬信號? CAN總線是一種數(shù)字通信協(xié)議,因此可以說是傳輸數(shù)字信號的。下面詳細介紹CAN總線是如何以數(shù)字信號進行數(shù)據(jù)傳輸的。 CAN(Controller Area

2023-11-22 18:18:25 1294

1294 AMBA APB總線可以用在低帶寬和不需要高性能的外設上(即低速且低頻率的外設);可以將APB視作AHB的二級總線;

·低功耗(APB總線信號端口比較簡單,復雜度低,低頻工作環(huán)境等因素都可以

2023-11-29 15:19:38 265

265

之前的兩篇文章給大家介紹了APB協(xié)議相關的知識點,并結(jié)合實際的代碼給大家講解了一下APB slave的設計。并說明了一下APB slave mux這個模塊。 上一篇文章提到:通常而言,APB

2024-01-13 10:09:05 215

215

IC設計的時候,都應該像這樣規(guī)劃好各個模塊的連接關系,確定好以后再寫代碼。該模塊是一個 基于APB協(xié)議完成寄存器配置或讀取的設計實例 。設計相對比較簡單,但不失為一個很好的學習資料。 上面APB相關的信號都介紹過,這里不再重復介紹,其中的ECOREVNUM的意思是ECO revisi

2024-01-13 10:15:41 248

248

APB(Advanced Peripheral Bus) 作為高級外設總線是AMBA協(xié)議之一,也是最基本的總線協(xié)議。按照ARM官方定義,APB是一種低成本的接口協(xié)議,可以實現(xiàn)低功耗以及精簡的接口設計,降低接口設計的復雜度。

2024-01-17 17:35:09 158

158

電路,并探討時序電路中可能存在的狀態(tài)循環(huán)。 首先,同步時序電路是指時序元件按照整個系統(tǒng)的時鐘信號進行同步操作的時序電路。常見的同步時序元件有鎖存器和觸發(fā)器。鎖存器可以將輸入信號“鎖定”,在時鐘上升沿或下降沿將輸入信

2024-02-06 11:22:30 291

291

電子發(fā)燒友App

電子發(fā)燒友App

評論