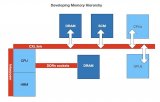

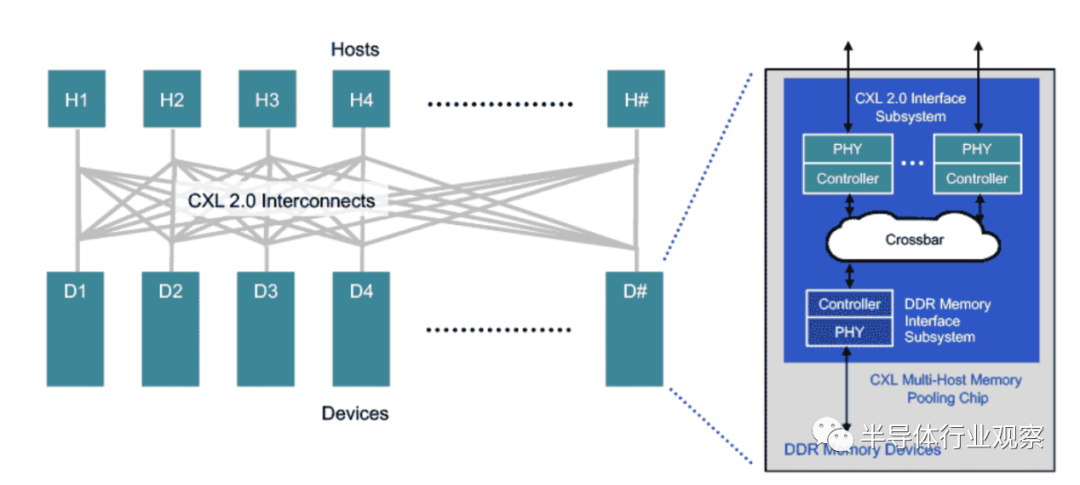

Infinity架構為例,AMD計劃將其CPU、GPU、FPGA與3D V-Cache都放在同一個框架內,并利用基于CXL 2.0的內存來完成分解,讓整個系統從計算、內存到存儲都能自由組合。 ? CXL聯盟董事成員 / CXL聯盟 ? 為了進一步推廣并維護這一標準,CXL聯盟誕生了。從2019年到現在,該聯

2022-06-30 08:03:00 3639

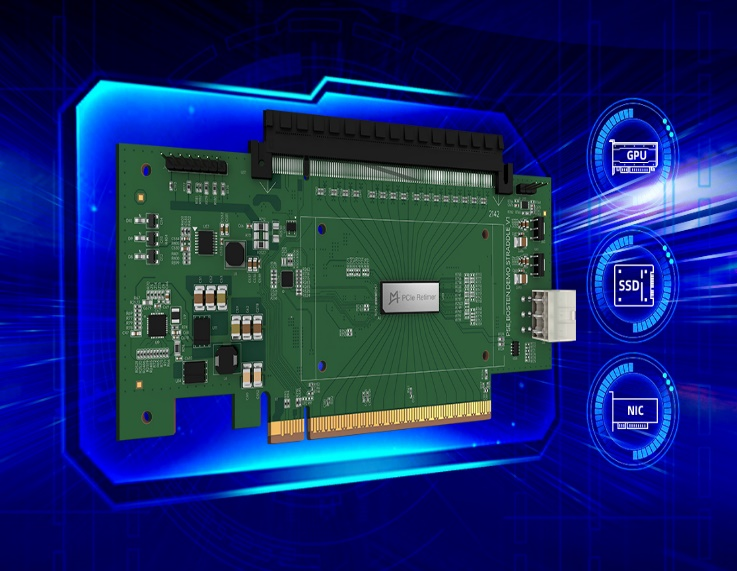

3639 上海,?2023年1月6日 —— 瀾起科技 今天宣布,其PCIe 5.0/CXL?2.0?Retimer芯片成功實現量產。 該芯片是瀾起科技現有PCIe 4.0 Retimer產品的關鍵升級,可為

2023-01-06 09:48:24 1095

1095

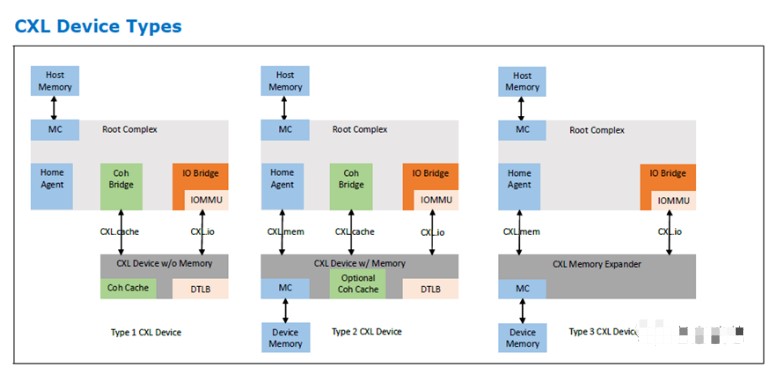

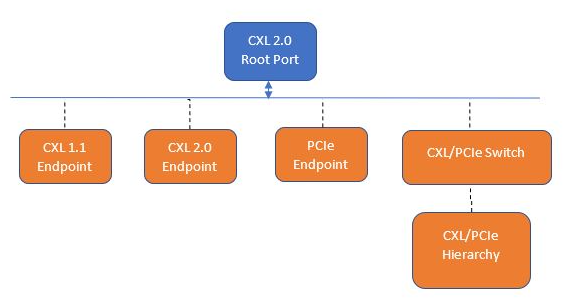

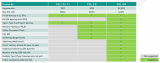

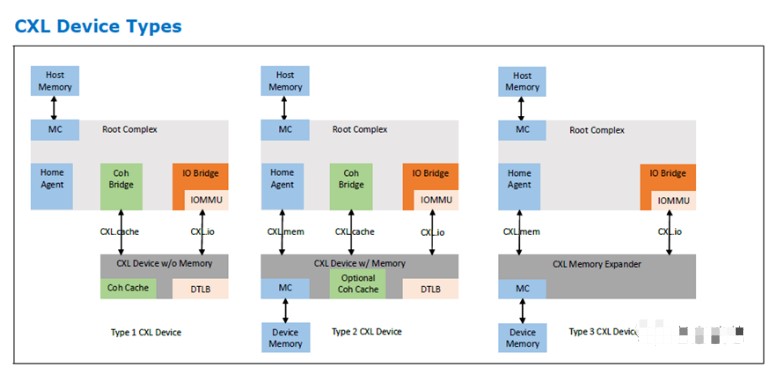

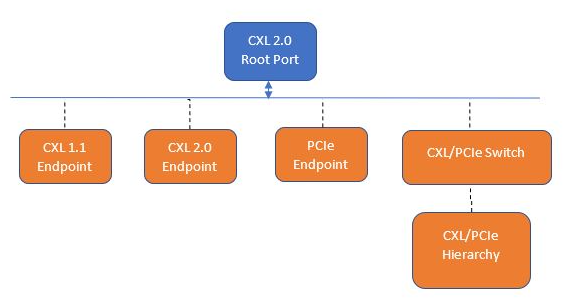

CXL設備擴展限制只允許每個VH(Virtual Hierarchy)啟用一個Type 1或Type 2設備。

2022-09-14 09:10:25 5608

5608

鑒于KAIST的HPC根源,將DirectCXL原型放在一起的研究人員專注于使用遠程直接內存訪問(RDMA)協議將CXL內存池與跨系統直接內存訪問進行比較。

2022-09-23 10:50:26 1101

1101 隨著線程數的增加,在每個方案上運行DLRM推理都是線性的,并且斜率不同。DDR5-R1和CXL存儲器的總體趨勢相似,這與第4.3.2節中的觀察結果一致

2023-04-12 14:07:51 281

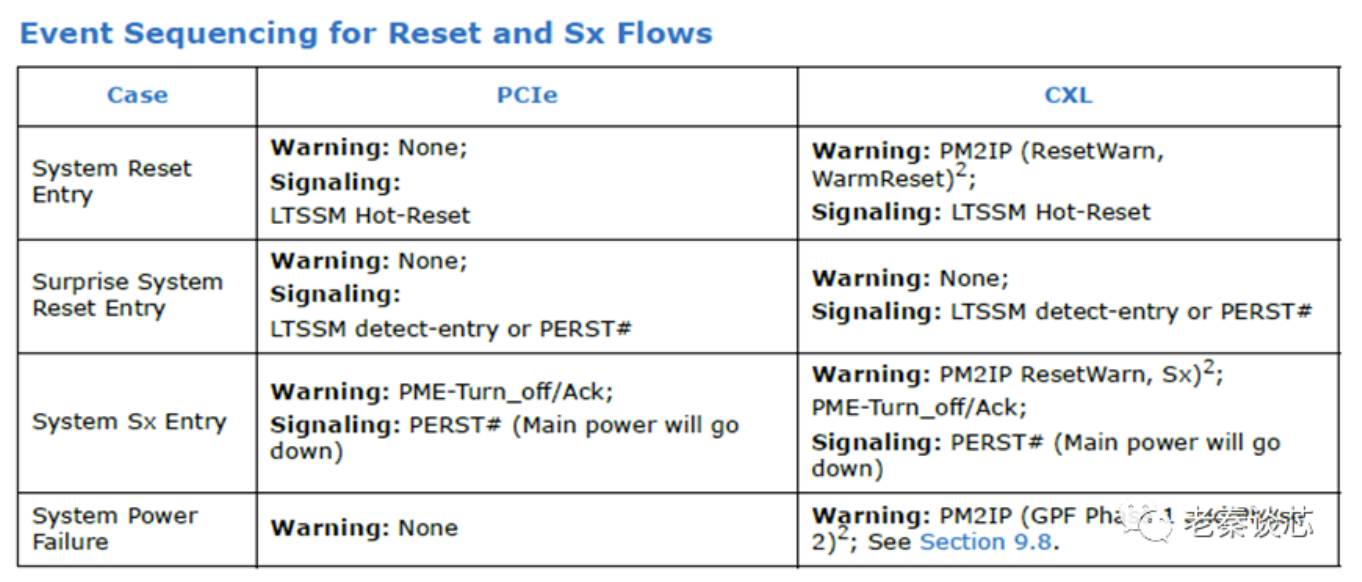

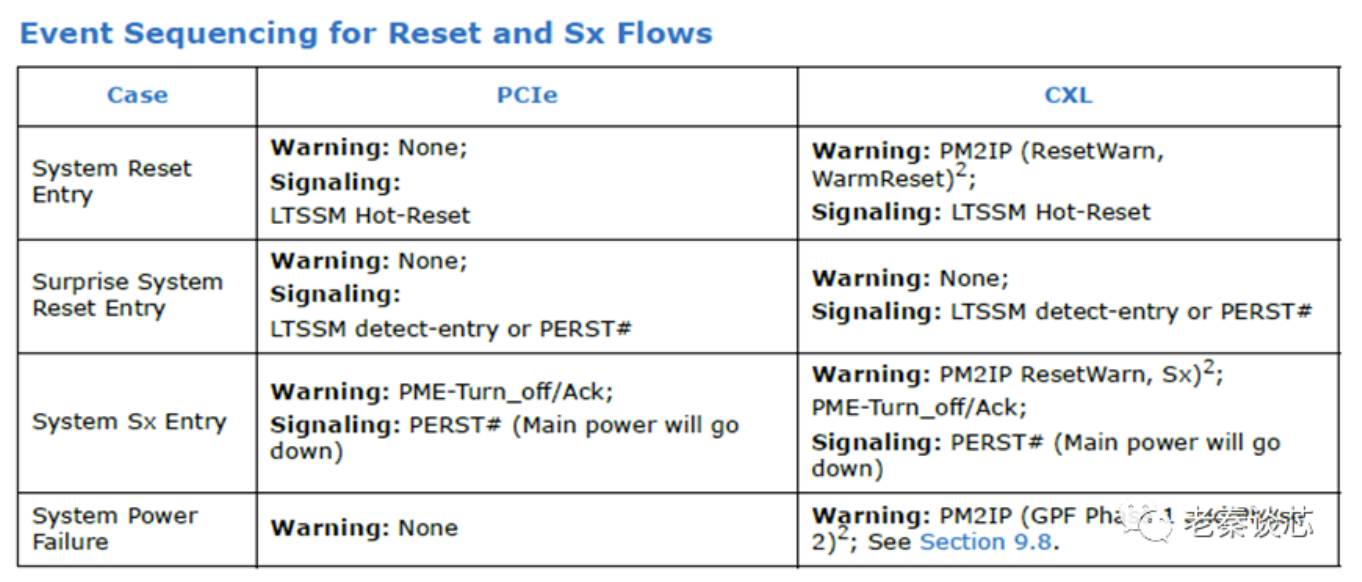

281 這三種復位被歸納為傳統(Conventional)復位。Function級復位和CXL復位不是傳統復位。

2023-09-22 14:37:19 1867

1867

Compute Express Link(CXL)作為一種先進的互連技術,在當今高性能計算領域引起了廣泛關注

2023-11-29 15:26:33 801

801

本文提出了一種基于RDMA和CXL的新型低延遲、高可擴展性的內存解耦合系統Rcmp。其顯著特點是通過CXL提高了基于RDMA系統的性能,并利用RDMA克服了CXL的距離限制。

2024-02-29 10:05:40 333

333

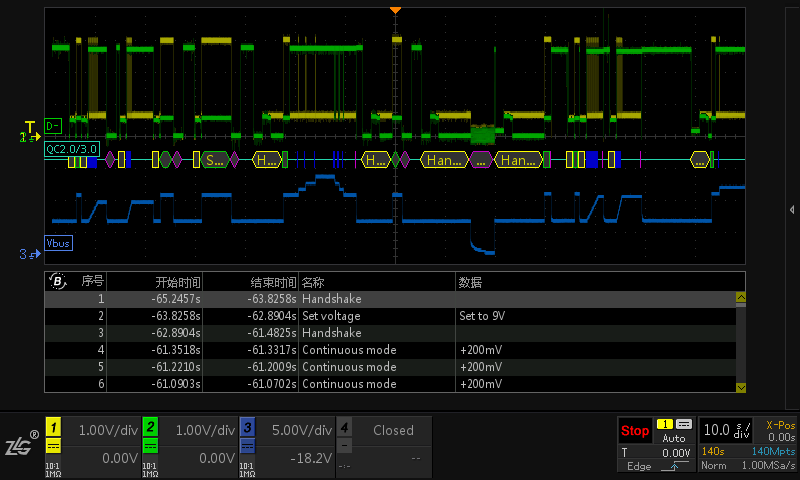

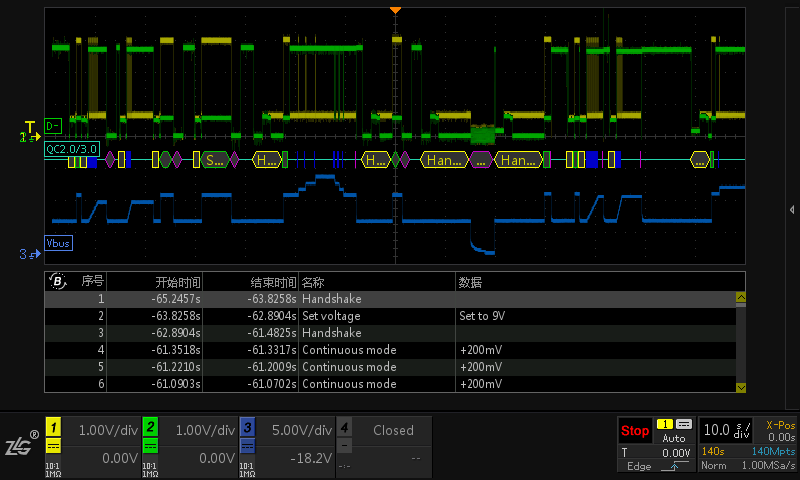

。 一、簡介 QC2.0/3.0是高通在近兩年制定的手機快充協議,相比聯發科和OPPO的快充協議,高通QC快速充電技術在智能手機領域的占有率最高。QC2.0現在趨于普及,針對智能手機定制的ClassA標準支持5V、9V和12V輸入電壓。QC3.0則在QC2.0的基礎上,支持200mv步進的漸變調節電壓。目前已

2017-10-01 10:01:00 14557

14557

互聯標準之戰,CXL 正在走向勝利 ? 在上世紀總線大戰之下,各大廠商為了自己的開放標準紛紛全力出擊,最終只留下PCIe統治著服務器市場。而在高性能計算對延遲、帶寬要求越來越高的情況下,互聯技術同樣

2021-11-13 09:15:42 4999

4999 電子發燒友網報道(文/周凱揚)要說去年內存市場最大的動靜是DDR5內存的面世,那么今年的大新聞無疑是一眾CXL內存的新品出現了。CXL這種新的互聯技術標準給內存市場,尤其是數據中心內存市場帶來了更大

2022-11-02 02:08:00 1494

1494 CXL1008P - CMOS-CCD Signal Processor for Skew Compensation - Sony Corporation

2022-11-04 17:22:44

CXL1009P - CMOS-CCD SIGNAL PROCESSOR FOR TBC - Sony Corporation

2022-11-04 17:22:44

CXL1502M - CMOS-CCD Signal Processor - Sony Corporation

2022-11-04 17:22:44

CXL1504M - CMOS-CCD 1H Delay Line for NTSC - Sony Corporation

2022-11-04 17:22:44

CXL1505M - CMOS-CCD Signal Processor - Sony Corporation

2022-11-04 17:22:44

CXL1506 - CMOS-CCD 1H/2H Delay Line for PAL - Sony Corporation

2022-11-04 17:22:44

CXL1506N - CMOS-CCD 1H/2H Delay Line for PAL - Sony Corporation

2022-11-04 17:22:44

CXL1517 - CMOS-CCD Signal Processor - Sony Corporation

2022-11-04 17:22:44

CXL1517N - CMOS-CCD Signal Processor - Sony Corporation

2022-11-04 17:22:44

CXL1518M - CMOS-CCD Signal Processor - Sony Corporation

2022-11-04 17:22:44

CXL1518N - CMOS-CCD Signal Processor - Sony Corporation

2022-11-04 17:22:44

CXL5003 - CMOS-CCD 1H Delay Line for PAL - Sony Corporation

2022-11-04 17:22:44

CXL5003M - CMOS-CCD 1H Delay Line for PAL - Sony Corporation

2022-11-04 17:22:44

CXL5003P - CMOS-CCD 1H Delay Line for PAL - Sony Corporation

2022-11-04 17:22:44

CXL5005M - CMOS-CCD 1H Delay Line for NTSC with PLL - Sony Corporation

2022-11-04 17:22:44

CXL5504P - CMOS-CCD 1H Delay Line for NTSC - Sony Corporation

2022-11-04 17:22:44

CXL5505M - CMOS-CCD 1H Delay Line for PAL - Sony Corporation

2022-11-04 17:22:44

CXL5505P - CMOS-CCD 1H Delay Line for PAL - Sony Corporation

2022-11-04 17:22:44

CXL5507P - CMOS-CCD 1H Delay Line for NTSC - Sony Corporation

2022-11-04 17:22:44

CXL5508M - CMOS-CCD 1H Delay Line for PAL - Sony Corporation

2022-11-04 17:22:44

CXL5512P - CMOS-CCD 1H Delay Line for NTSC - Sony Corporation

2022-11-04 17:22:44

CXL5513M - CMOS-CCD 1H Delay Line for NTSC - Sony Corporation

2022-11-04 17:22:44

CXL5514P - CMOS-CCD 1H Delay Line for PAL - Sony Corporation

2022-11-04 17:22:44

;高達300KHz的可編程設定頻率驅動外部高壓MOSFET;外部取樣電阻設置負載電流從10mA到1A;它也可以提供低頻灰度PWM調光功能,建議設計200Hz-1KHz。CXL9910是一個低成本的可降壓

2017-08-01 11:43:00

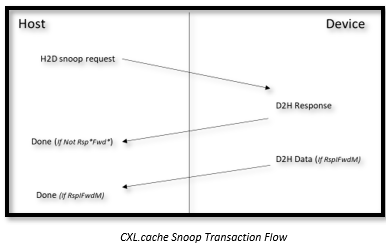

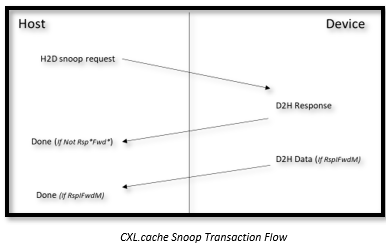

1、CXL事務層學習 CXL.cache協議將設備和主機之間的交互定義為多個請求,每個請求至少有一條相關的響應消息,有時還有數據傳輸。該接口在每個方向上由三個通道組成:請求(Request)、響應

2022-10-18 14:19:02

。3.1.7 可延遲寫CXL規范中定義的可延遲寫入僅在CXL 1.1模式下運行時適用。在CXL 2.0模式下操作時,請參閱PCIe規范以了解此功能。原作者:老秦談芯

2022-10-08 15:21:40

3.3.1 介紹CXL內存協議被稱作CXL.mem。CXL.mem定義了CPU和內存之間的傳輸接口。該協議可用于多個不同的內存連接選項,包括當內存控制器位于主機CPU中時,或當內存控制器位于加速器

2022-11-01 15:08:12

有16.6新功能中文版介紹嗎PCB打樣找華強 http://www.hqpcb.com 樣板2天出貨

2012-11-08 17:28:32

集群的外觀:在上圖右側(在本文文末的功能圖像中更詳細地顯示了四個內存板),它們具有FPGA創建PCI-Express鏈接并運行CXL.memory協議,用于在內存服務器和通過PCI-Express鏈接

2022-11-15 11:14:59

CXL.mem和CXL.io。無論哪種類型,CXL.io都是不可缺少的,因為設備的發現,枚舉,配置等都是由CXL.io來負責。 傳統的非一致I/O設備主要依賴于標準的生產者-消費者訂單

2022-09-14 14:24:52

.cache共用的鏈路層4.2.1 介紹CXL.mem和CXL.cache共用同一個鏈路層,下圖中的黃色區域。4.2.2 高層次CXL.cache/CXL.mem Flit概述CXL.cache/CXL

2023-02-21 14:27:46

現在已經有幾十家的會員。目前CXL協議共有個版本,分別是1.0,1.1,2.0和剛剛發布的3.0,協議規范可以在官網上下載。關于CXL,協議里面是這樣說的“CXL is a low-latency

2022-09-09 15:03:06

文章目錄文章目錄文章目錄一、串口協議和RS-232標準1.串口通訊2.RS-2323.RS232電平與TTL電平的區別(1).TTL電平標準(2)具體區別二、USB/TTL轉232"模塊

2022-01-25 08:06:54

文章目錄一、串口協議和RS-232標準(一)、TTL電平標準(二)、RS232標準二、搭建STM32開發環境1.安裝jdk2.安裝STM32CubeMX一、串口協議和RS-232標準串口通信指串口按

2022-02-15 07:38:47

何謂快充QC2.0/3.0協議?QC2.0/3.0協議的工作原理是什么?

2021-11-04 07:00:54

處理器大廠英特爾(Intel)宣布聯合多家廠商,一起推出了針對資料中心、高效能計算、AI 等領域的全新的互聯協議 Compute EXpress Link(CXL),并將正式發布 CXL 1.0 規范。

2019-03-13 17:03:11 2790

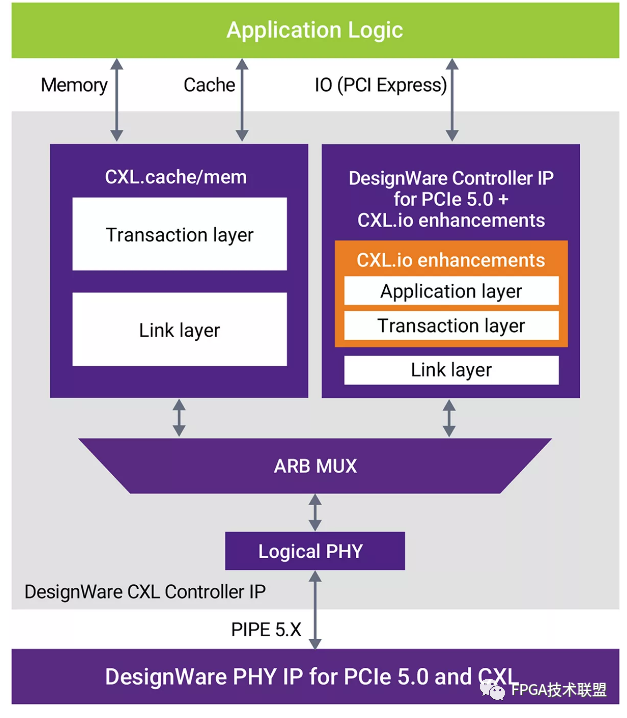

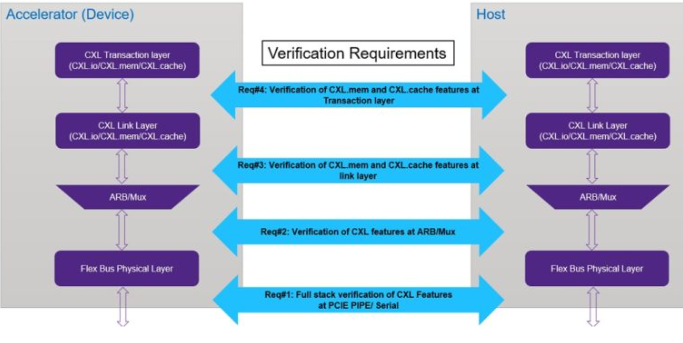

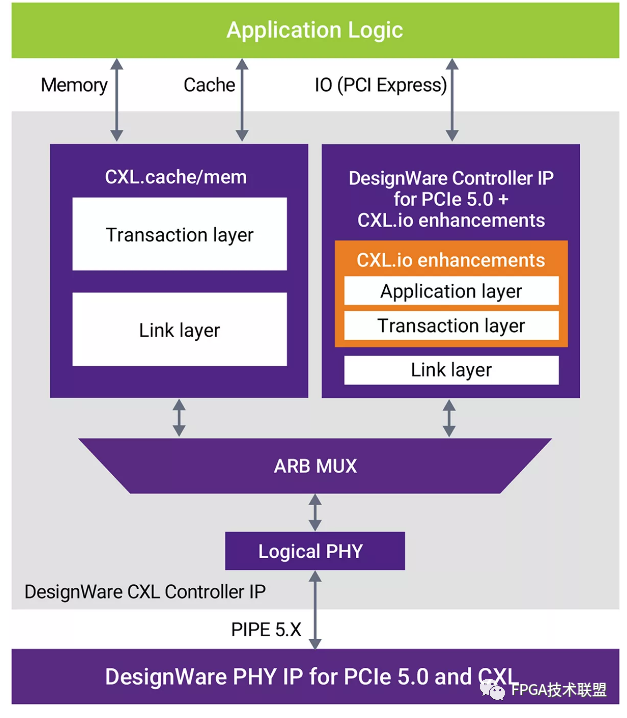

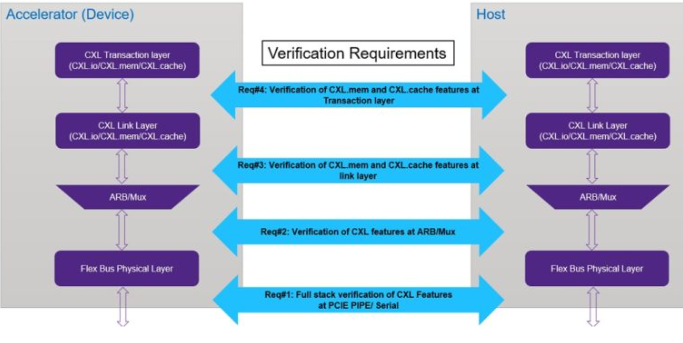

2790 寬度為 512 位,支持所有必需的 CXL 協議和設備類型,以滿足具體應用要求 ● 該業內首款 CXL IP 整體解決方案包含可配置的控制器、采用 FinFET 工藝的 32GT/s PHY 以及驗證

2020-10-27 16:40:28 1477

1477 ,Microchip Technology Inc.(美國微芯科技公司)宣布推出低延遲 PCI Express(PCIe) 5.0 和 Compute Express Link (CXL )1.1/2.0

2020-12-17 17:16:20 1901

1901 新思科技(Synopsys)宣布推出業界首個支持Compute Express Link (CXL) 2.0的驗證IP(VIP),以實現數據密集型片上系統(SoC)的性能突破。CXL是新一代開放標準

2020-12-26 11:04:10 2456

2456 新思科技驗證技術團隊研發副總裁 Vikas Gautam 表示:“新思科技內存一致性驗證 IP 產品包括 CXL 2.0、CXL 1.1 和 CCIX,可支持具有高數據吞吐量要求的新應用程序。我們

2021-02-15 09:18:00 1667

1667 最近有幾個熱點事件發生了,好像都跟CXL有關,小編前年也關注到這一點了,可以看下這篇文章“CXL高速互連技術成員數已從9名增加到33名” 美光退出3D Xpoint,移至CXL 首先第一件事大家

2021-04-01 15:48:09 1773

1773

的大戰。CXL、CAPI(OpenCAPI)、CCIX、Gen-Z、AMD的Infinity Fabric與英偉達的NV Link等技術百花齊放,既有開放標準,也有專用標準。 這其中不少開放標準其實也都有對應的廠商在背后支持推動,比如CXL由英特爾主導,CCIX由賽靈思主導,OpenCAPI由IB

2021-11-13 09:24:16 1774

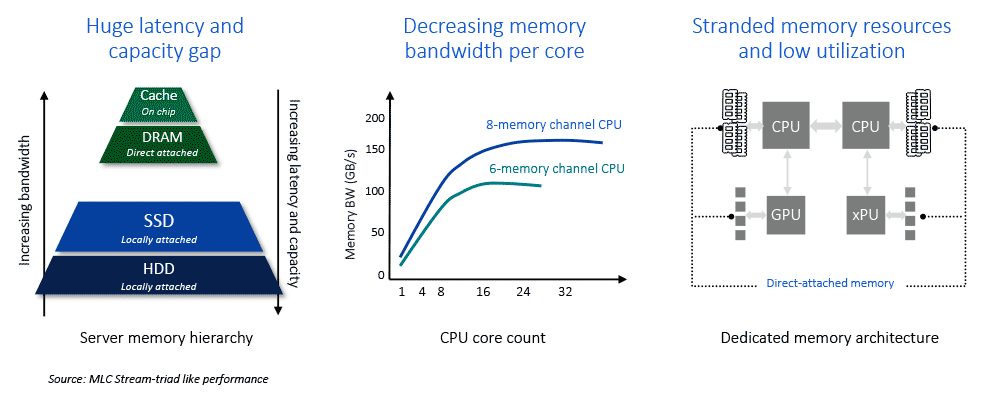

1774 Leo CXL? Memory Accelerator 技術引領新一代服務器分層內存,解決了數據中心和云端的內存容量和帶寬瓶頸。

2021-11-23 14:39:12 1662

1662 運行。這不是特定于某個供應商的實現,而是一個廣泛的行業標準。CXL的主要優勢是它允許不同終端上的內存直接支持Load/Store,這就是我們接下來要介紹的內容。

2022-03-23 15:26:03 3919

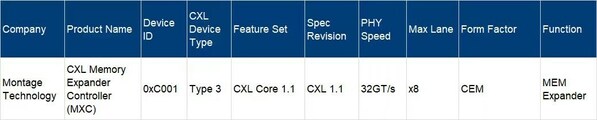

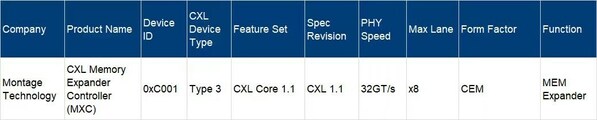

3919 MXC芯片是一款CXL DRAM內存控制器,屬于CXL協議所定義的第三種設備類型。該芯片支持JEDEC DDR4和DDR5標準,同時也符合CXL 2.0規范,支持PCIe 5.0的速率。

2022-05-06 10:46:43 2174

2174 自2021年5月推出三星首款配備現場可編程門陣列(FPGA)控制器的CXL DRAM原型機以來,三星一直與數據中心、企業服務器和芯片組公司密切合作,以開發更好的、可定制的CXL產品。

2022-05-10 10:15:12 1724

1724 這是一個雄心勃勃但得到廣泛支持的路線圖,在短短三年內使,CXL 便成為事實上的先進設備互連標準,這就導致競爭對手標準 Gen-Z、CCIX 以及截至昨天的 OpenCAPI 都退出了競爭。

2022-08-04 09:39:48 897

897 作為一種開放式互連新標準,CXL面向 CPU 和專用加速器的密集型工作負載,這些負載都需要在主機和設備之間實現高效穩定的存儲器訪問。

2022-08-09 12:36:38 2732

2732 中國上海,2022 年 8 月 10 日 —— 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)今日宣布推出業界首個針對 Compute Express Link(CXL)3.0 標準

2022-08-10 10:14:50 1781

1781 正因如此,不同計算節點之間的高效資源共享,特別是緩存一致性等問題被搬上臺面,一連串的開放互聯標準開始興起,譬如CXL、Gen-Z、OMI。但隨著2022年閃存峰會上CXL 3.0的推出,這一切競爭似乎都被畫上了句號。

2022-08-15 09:26:58 1412

1412 CXL是CXL聯盟開發的一項開放式互聯新標準,基于PCIe物理層的高速、低延遲CPU到設備互連技術。CXL可在主機CPU和互聯設備(例如加速器和存儲器擴展設備)之間提供高效連接。

2022-08-23 09:18:44 934

934 (CXL?)內存模塊XMM CXL內存模塊。SMART Modular的這款新型 DDR5 XMM CXL 模塊通過CXL接口增加緩存一致性內存,可提升服務器和數據中心的運算性能,更能超越現今大多數服務器只有 8信道或12信道的限制,進一步擴展大數據處理能力。

2022-09-01 15:38:06 992

992 CXL 3.0 中最重要的變化是內存共享和設備到設備的通信。主機 CPU 和設備現在可以在相同的數據集上協同工作,而無需不必要地打亂和復制數據。

2022-09-05 15:29:52 932

932 CXL是英特爾推出的標準。在2019年,英特爾推出了CXL。CXL是高度中央處理器到設備和CPU到內存鏈接的開放標準。其推出的目的在于簡化加速器和內存擴展的互連和可擴展性。

2022-09-05 16:46:06 322

322 為什么這一點很重要?因為,這讓CXL主機和CXL設備能夠運行和處理共享的數據,并能確保在同一存儲器位置讀取相同副本的數據。歸屬代理不允許同時更改數據,所以每次(主機或掛載的設備)發起更改時,歸屬代理都會確保所有數據副本保持一致。

2022-09-06 10:03:32 1226

1226 CXL是基于PCIe 5.0實現的連接技術,復用了很多PCIe協議的東西,這一點上與CCIX比較像,但又不完全一樣。說起CCIX和CXL,難免要相互對比。

2022-09-06 10:05:57 5256

5256 CXL.io為IO設備提供非一致性的load/strore接口。事務類型、事務數據包格式、信用流量控制、虛擬通道管理、事務順序的規則等遵循PCIe協議。CXL.io的事務層如下圖中的黃色部分所示。

2022-10-10 16:02:29 2108

2108 通常,所有CXL.cache通道都必須彼此獨立工作。然而,有一個特例,為了保證正確性,必須維護通道之間的順序。主機需要等待設備觀察到H2D響應上發送的全局排序(GlobalOrdering,GO)消息,然后再發送相同地址的后續監聽。

2022-10-17 10:46:52 2788

2788 電子發燒友網報道(文/周凱揚)要說去年內存市場最大的動靜是DDR5內存的面世,那么今年的大新聞無疑是一眾CXL內存的新品出現了。CXL這種新的互聯技術標準給內存市場,尤其是數據中心內存市場帶來了更大

2022-11-02 07:20:06 909

909 內存QoS遙測是內存設備的一種機制,用于在CXL.mem請求的每個響應消息中指示其當前負載級別(DevLoad)。這使主機能夠根據負載級別來衡量對部分設備、單個設備或設備組的CXL.mem請求的速率,從而優化這些內存設備的性能,同時限制結構擁塞。

2022-11-02 09:45:50 1813

1813 瀾起科技今天宣布,其PCIe 5.0/CXL 2.0 Retimer芯片成功實現量產。該芯片是瀾起科技現有PCIe 4.0 Retimer產品的關鍵升級,可為業界提供穩定可靠的高帶寬、低延遲PCIe 5.0/ CXL 2.0互連解決方案。

2023-01-06 15:07:53 972

972 CXL 在大型數據中心內越來越受歡迎,作為提高不同計算元素(如內存和加速器)利用率的一種方式,同時最大限度地減少對額外服務器機架的需求。

2023-02-01 09:12:33 496

496 CXL是一個全新的得到業界認同的互聯技術標準,其正帶著服務器架構迎來革命性的轉變。

2023-02-02 09:55:35 739

739 CXL全稱為Compute Express Link,作為一種全新的開放式互聯技術標準,其能夠讓CPU與GPU、FPGA或其他加速器之間實現高速高效的互聯,從而滿足高性能異構計算的要求,并且其維護CPU內存空間和連接設備內存之間的一致性。總體而言,其優勢高度概括在極高兼容性和內存一致性兩方面上。

2023-02-11 11:01:20 1339

1339 CXL全稱為Compute Express Link,作為一種全新的開放式互聯技術標準,其能夠讓CPU與GPU、FPGA或其他加速器之間實現高速高效的互聯,從而滿足高性能異構計算的要求,并且其維護CPU內存空間和連接設備內存之間的一致性。總體而言,其優勢高度概括在極高兼容性和內存一致性兩方面上

2023-02-21 15:06:54 1453

1453

CXL和PCIe之間的區別可能不太明顯。在信號級別上,這兩者確實是相同的,但兩者的協議不同。CXL選擇比PCIe更快的協議,盡管CXL.io支持標準的PCIe I/O設備。

2023-04-11 11:14:02 2141

2141 基于先進CXL 2.0的128GB CXL DRAM將于今年量產,加速下一代存儲器解決方案的商用化

2023-05-15 17:02:10 179

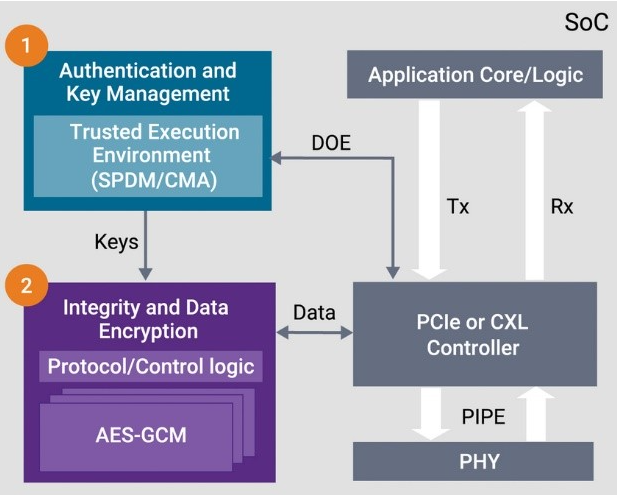

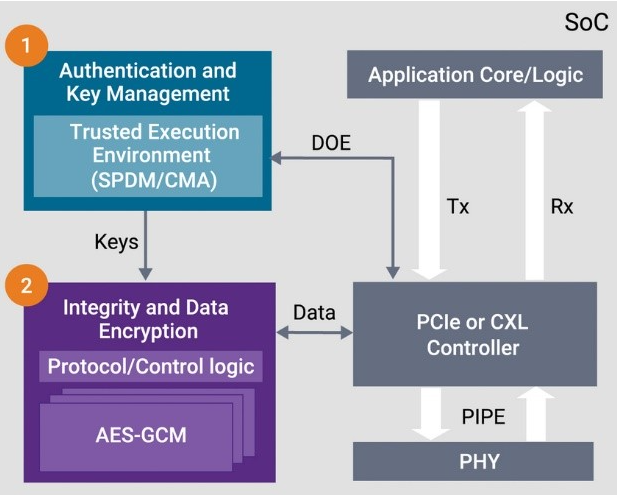

179 CXL 2.0規范為 CXL.io 和CXL.cache/CXL.mem協議引入了IDE原理圖。CXL.io 途徑使用 PCIe 規范定義的 IDE,而 CXL.cache/CXL.mem 相關更新在 CXL 2.0 規范中引入。在本博客中,我們將概述安全設置的外觀以及 CXL 采用的安全策略。

2023-05-25 16:41:12 837

837

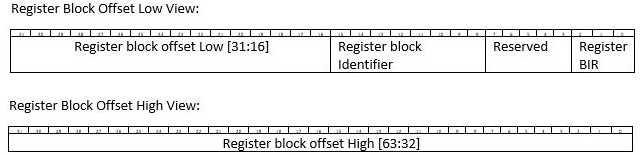

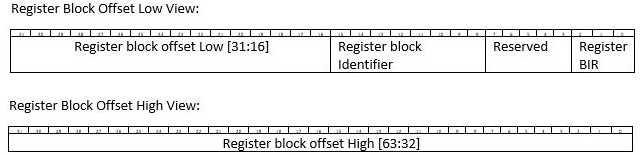

規范將內存映射寄存器鏈接在設備的 BAR(基址范圍)中。在本博客中,我們將重點介紹如何訪問 CXL 2.0 規范內存映射寄存器。

2023-05-25 16:56:20 1130

1130

CXL 2.0 規范在 PCIe 配置空間映射寄存器中定義了多個新的 PCIe 指定供應商特定擴展功能 (DVSEC)。以下是 CXL 2.0 設備的一些強制性 DVSEC。

2023-05-25 17:22:06 915

915

CXL 在主機 CPU 和設備(如硬件加速器)之間具有相干內存訪問功能,通過利用 PCIe 架構的高級功能,滿足下一代設計中處理數據和計算密集型工作負載的要求。

2023-05-26 10:12:30 1320

1320

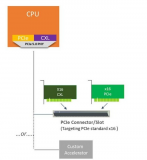

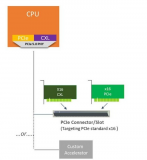

CXL 是一種在主機(通常是 CPU)和設備(通常是附加了內存的加速器)之間實現高帶寬、低延遲鏈接的技術。CXL 堆棧專為低延遲而設計,使用 PCIe 電氣和附加卡的標準 PCIe 外形規格。CXL 使用靈活的處理器端口,可以自動協商到標準 PCIe 事務協議或備用 CXL 事務協議。

2023-05-26 10:33:11 3266

3266

服務器系統提供增強支持。CZ120模塊使用Compute Express Link??(CXL?)標準,并完全支持CXL 2.0 Type 3標準。美光CZ120通過獨特的雙通道

2023-08-11 10:15:25 310

310 。 ? ?? CXL,全稱為Compute Express Link,是一種全新的高速互連協議,旨在提升人工智能、大數據等內存密集型工作負載的數據傳輸和處理性能。通過CXL聯盟的合規測試,是檢驗CXL生態系統內各產品部件包括CPU、CXL設備、加速器等是否合乎CXL規范的關鍵,也是CXL生態系統內部實現互操

2023-08-18 09:14:38 703

703 Integrators List)。瀾起科技是全球首家進入CXL合規供應商清單的MXC芯片廠家。 CXL?,全稱為Compute Express Link?,是一種全新的高速互連協議,旨在提升人工智能、大數據等內存

2023-08-22 05:11:58 436

436

更快的數據傳輸速度:CXL技術可以實現高達25GB/s的數據傳輸速度,比目前常用的PCIe 4.0技術還要快。這意味著在數據中心等高性能應用場景下,可以更快地進行數據處理和傳輸。

更低的延遲

2023-09-27 09:26:03 1794

1794

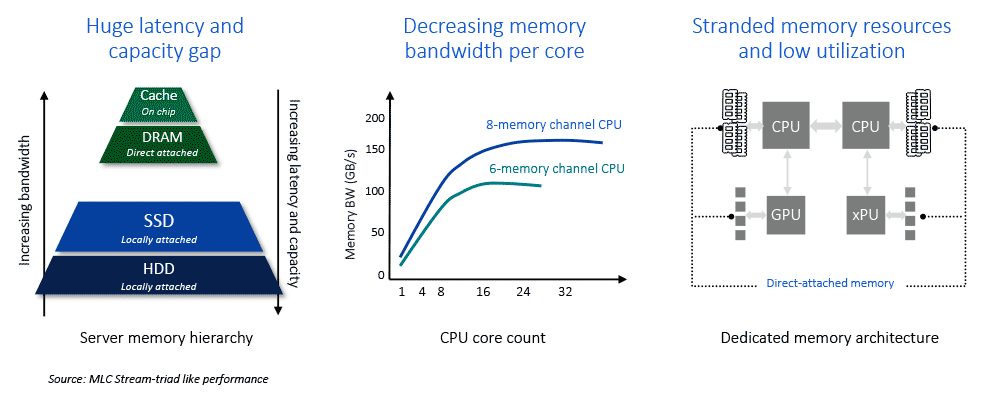

CXL的目標:解決CPU和設備、設備和設備之間的內存鴻溝。服務器有巨大的內存池和數量龐大的基于PCIe運算加速器,每個上面都有很大的內存。內存的分割已經造成巨大的浪費、不便和性能下降。CXL就是為解決這個問題而誕生。

2023-10-30 14:30:31 3130

3130

CXL.io 和CXL.cache 是CXL 協定中的兩個子協定,它們的功能和用途有所不同,主要是為了引入非對稱的概念;CXL.io 類似于PCIe 的事件(event),主要用于初始化、鏈接、設備發現、列舉以及寄存器(register) 的存取,從某種程度上說,它可以看作是PCIe事件的一個變種。

2023-11-22 15:43:58 464

464

解碼CXL存儲器擴展設備(上)

2023-12-04 15:33:54 175

175

導語: CXL是一種開放式全新互聯技術標準,可在主機處理器與加速器、內存緩沖區、智能I/O設備等設備之間提供高帶寬、低延遲連接,從而滿足高性能異構計算的要求,并且其維護CPU/GPU內存空間和連接

2023-12-27 10:35:01 286

286

CXL憑借其統一的接口標準,通過PCIe接口連接各類處理器如CPU、GPU及內存設備,有效解決了當前系統在速度、延遲和可擴展性上所面臨的瓶頸。

2023-12-27 10:45:45 270

270 近日,國內知名存儲器制造企業佰維科技股份有限公司(以下簡稱“佰維”)欣然宣告,其在DRAM技術領域取得了重要突破——成功研發并量產了符合CXL 2.0規范的CXL DRAM內存擴展模塊。這不僅對于我國信息技術創新有著重大意義,更是對于全球存儲器市場產生了積極影響。

2023-12-27 11:41:00 228

228 導語: CXL是一種開放式全新互聯技術標準,可在主機處理器與加速器、內存緩沖區、智能I/O設備等設備之間提供高帶寬、低延遲連接,從而滿足高性能異構計算的要求,并且其維護CPU/GPU內存空間和連接

2023-12-27 15:17:31 99

99

三星電子與開源軟件巨頭紅帽(RedHat)聯手,完成了在實際用戶環境中的CXL(ComputeExpressLink)內存操作;此舉系業內首次,將進一步擴大其 CXL 生態系統。

2023-12-27 15:56:20 352

352 三星電子發布公告稱,已與 Red Hat 合作,在真實用戶環境中成功驗證了 CXL (Compute Express Link) 內存操作;此舉系業內首次,將進一步擴大其 CXL 生態系統。

2023-12-28 09:35:27 230

230 CXL的目標:解決CPU和設備、設備和設備之間的內存鴻溝。服務器有巨大的內存池和數量龐大的基于PCIe運算加速器,每個上面都有很大的內存。內存的分割已經造成巨大的浪費、不便和性能下降。CXL就是為解決這個問題而誕生。

2024-01-11 16:53:38 413

413

據三星展示的圖片顯示,此模組可以通過CXL接口在閃存部分及CPU之間進行I/O塊傳輸,也可以運用DRAM緩存和CXL接口達到64字節的內存I/O傳輸。

2024-03-21 14:31:05 202

202

電子發燒友App

電子發燒友App

評論