為什么要科普PCIe

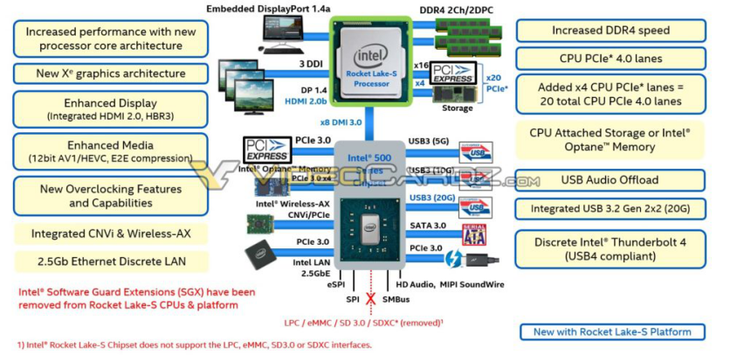

PCIe總線是服務(wù)器系統(tǒng)里最重要的總線,經(jīng)過(guò)PCIe信號(hào)的互聯(lián),CPU得以與各種外設(shè)部件進(jìn)行通信。如果我么比喻每個(gè)bit的數(shù)據(jù)是一輛小車,PCIe總線是車道,每條Lane是一條雙向車道,PCIe版本規(guī)定了速度上限,由此就很好理解了,不考慮編碼損耗的情況下,車道越多,允許的車速越快,通過(guò)的數(shù)據(jù)自然也就越多,PCIe 7.0 Base Specification目前剛剛發(fā)布Draft 0.3版本,提供512GB/s的速度,PCI-SIG公布PCIe7.0規(guī)范的0.3版本,預(yù)計(jì)要到2028年才會(huì)正式發(fā)布;與此同時(shí),隨著Intel支持PCIe 5.0的Ice Lake Xeon-SP CPU即將在今年底發(fā)布,再加上支持PCIe 5.0的AMD EPYC CPU和一眾ARM CPU的逐漸出貨,PCIe 5.0即將在2023年成為市場(chǎng)上的主流,其對(duì)應(yīng)的Cable廠商做好準(zhǔn)備,了解學(xué)習(xí)回顧下PCI-E的發(fā)展歷程.

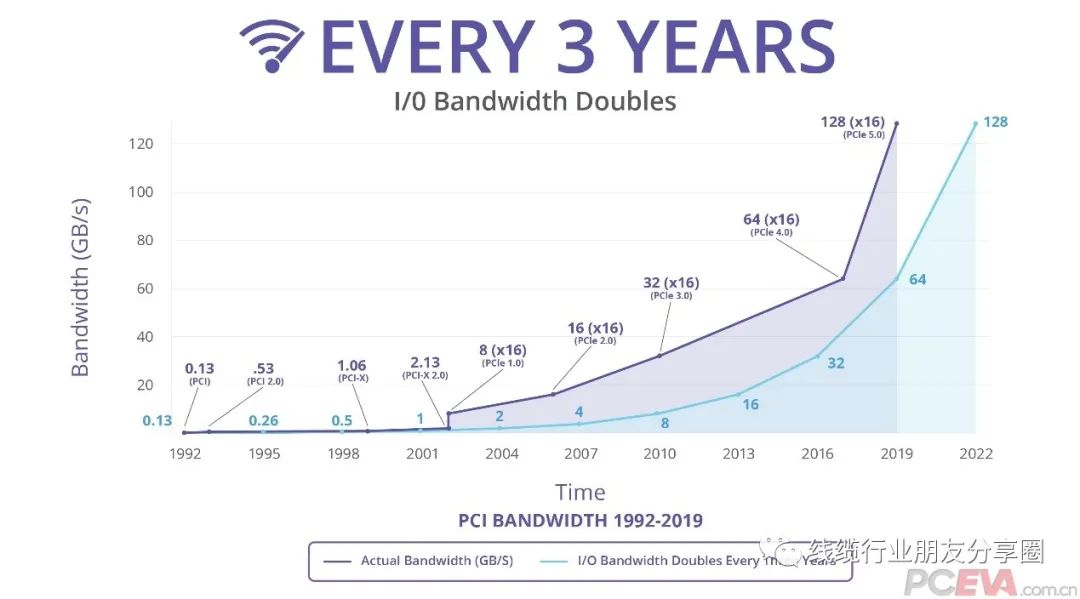

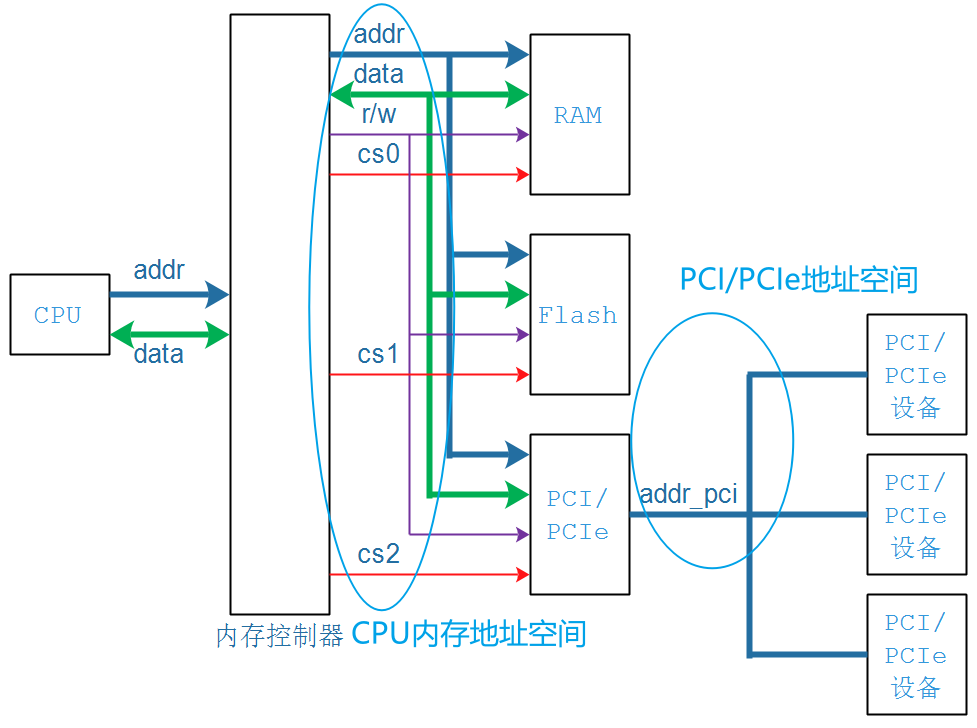

常用的PCI總線帶寬為133MB/S,于1992年誕生。接著因?yàn)樵诜?wù)器領(lǐng)域傳輸要求于是Intel把總線位數(shù)提高到64,這樣又出現(xiàn)了2種PCI總線,分別為64bit/33Mhz和64bit/66Mhz,帶寬分別為266Mbps和533Mbps。稍后在顯卡領(lǐng)域,Intel單獨(dú)開(kāi)發(fā)出了AGP,32bit,66Mhz,這樣帶寬為266Mbps,再加上后來(lái)AGP2.0的2X和4X標(biāo)準(zhǔn),最高4X的帶寬高達(dá)1Gbps,但是確切的說(shuō)AGP不是真正的總線,因?yàn)锳GP只能連接一個(gè)設(shè)備-顯卡。

同時(shí)服務(wù)器領(lǐng)域,幾家廠商聯(lián)合制定了PCI-X,64bit133Mhz版本的PCI,帶寬就為1Gbps,后來(lái)PCI-X 2.0,3.0又分別提升頻率,經(jīng)歷過(guò)266Mhz,533Mhz,甚至1GMhz,這個(gè)帶寬可以說(shuō)是非常足夠的了,不過(guò)這個(gè)時(shí)候PCI-X也面臨一些問(wèn)題:一方面是頻率提高造成的并行信號(hào)串?dāng)_,另一方面是共享式總線造成的資源爭(zhēng)用,總之也就是說(shuō)雖然規(guī)格上去了,但實(shí)際效果可能跑不了這些指標(biāo)。

于是,在2001年的英特爾春季IDF大會(huì)上,英特爾正式公布旨在取代PCI總線的第三代I/O技術(shù),該規(guī)范由Intel 支持的AWG(Arapahoe Working Group)負(fù)責(zé)制定,并稱之為第三代I/O總線技術(shù)(3rd Generation I/O,也就是3GIO),很明顯英特爾的意思是它代表著下一代I/O接口標(biāo)準(zhǔn)。交由 PCI-SIG(PCI特殊興趣組織)認(rèn)證發(fā)布后才改名為“PCI-Express”。這個(gè)新標(biāo)準(zhǔn)將全面取代當(dāng)時(shí)的PCI和AGP,最終實(shí)現(xiàn)總線標(biāo)準(zhǔn)的統(tǒng)一。它的主要優(yōu)勢(shì)就是數(shù)據(jù)傳輸速率高,目前最高可達(dá)到10GB/s以上,而且還有相當(dāng)大的發(fā)展?jié)摿ΑCI Express也有多種規(guī)格,從PCI Express 1X到PCI Express 16X,能滿足現(xiàn)在和將來(lái)一定時(shí)間內(nèi)出現(xiàn)的低速設(shè)備和高速設(shè)備的需求。

PCI Express(以下簡(jiǎn)稱PCI-E)采用了目前業(yè)內(nèi)流行的點(diǎn)對(duì)點(diǎn)串行連接,比起PCI以及更早期的計(jì)算機(jī)總線的共享并行架構(gòu),每個(gè)設(shè)備都有自己的專用連 接,不需要向整個(gè)總線請(qǐng)求帶寬,而且可以把數(shù)據(jù)傳輸率提高到一個(gè)很高的頻率,達(dá)到PCI所不能提供的高帶寬。相對(duì)于傳統(tǒng)PCI總線在單一時(shí)間周期內(nèi)只能實(shí) 現(xiàn)單向傳輸,PCI-E的雙單工連接能提供更高的傳輸速率和質(zhì)量,它們之間的差異跟半雙工和全雙工類似。

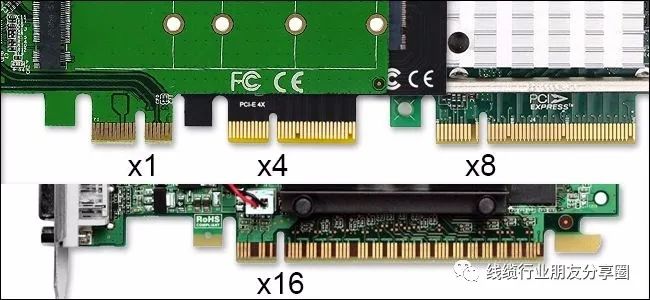

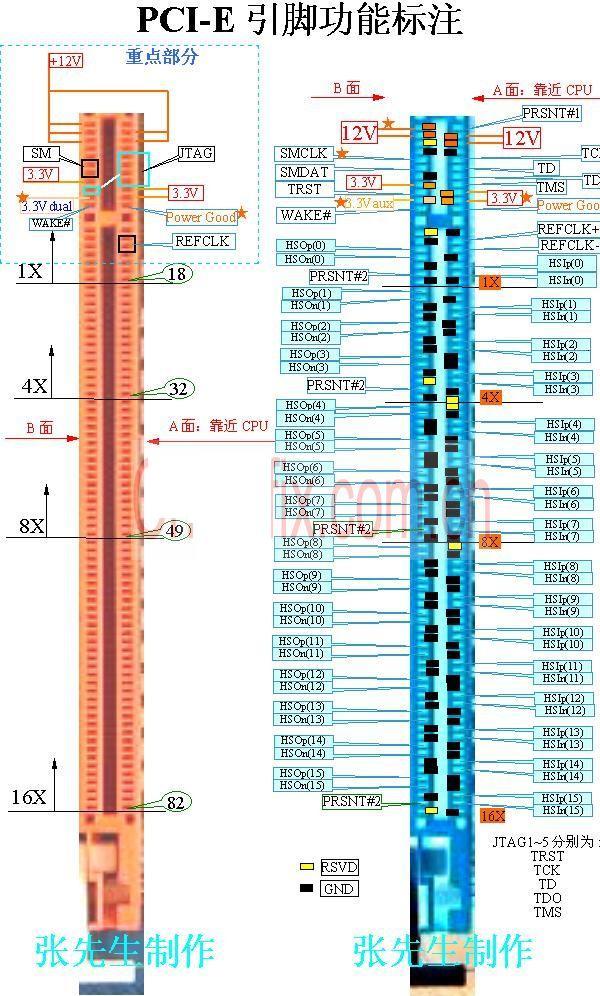

PCI-E的接口根據(jù)總線位寬不同而有所差異,包括X1、X4、X8以及X16,而X2模式將用于內(nèi)部接口而非插槽模式。PCI-E規(guī)格從1條 通道連接到32條通道連接,有非常強(qiáng)的伸縮性,以滿足不同系統(tǒng)設(shè)備對(duì)數(shù)據(jù)傳輸帶寬不同的需求。此外,較短的PCI-E卡可以插入較長(zhǎng)的PCI-E插槽中使 用,PCI-E接口還能夠支持熱拔插,這也是個(gè)不小的飛躍。PCI-E X1的250MB/秒傳輸速度已經(jīng)可以滿足主流聲效芯片、網(wǎng)卡芯片和存儲(chǔ)設(shè) 備對(duì)數(shù)據(jù)傳輸帶寬的需求,但是遠(yuǎn)遠(yuǎn)無(wú)法滿足圖形芯片對(duì)數(shù)據(jù)傳輸帶寬的需求。因此,用于取代AGP接口的PCI-E接口位寬為X16,能夠提供8GB/s的帶寬,遠(yuǎn)遠(yuǎn)超過(guò)AGP 8X的2.1GB/s的帶寬。

常見(jiàn)的PCIE卡槽

盡管PCI-E技術(shù)規(guī)格允許實(shí)現(xiàn)X1(250MB/秒),X2,X4,X8,X12,X16和X32通道規(guī)格,但是依目前形式來(lái)看,PCI-E X1和PCI-E X16已成為PCI-E主流規(guī)格,同時(shí)很多芯片組廠商在南橋芯片當(dāng)中添加對(duì)PCI-E X1的支持,在北橋芯片當(dāng)中添加對(duì)PCI-E X16的支持。除去提供極高數(shù)據(jù)傳輸帶寬之外,PCI-E因?yàn)椴捎么袛?shù)據(jù)包方式傳遞數(shù)據(jù),所以PCI-E接口每個(gè)針腳可以獲得比傳統(tǒng)I/O標(biāo)準(zhǔn)更多的帶 寬,這樣就可以降低PCI-E設(shè)備生產(chǎn)成本和體積。另外,PCI-E也支持高階電源管理,支持熱插拔,支持?jǐn)?shù)據(jù)同步傳輸,為優(yōu)先傳輸數(shù)據(jù)進(jìn)行帶寬優(yōu)化。

各個(gè)版本的PCI-E的規(guī)范如下

PCI-E 1.0規(guī)范:

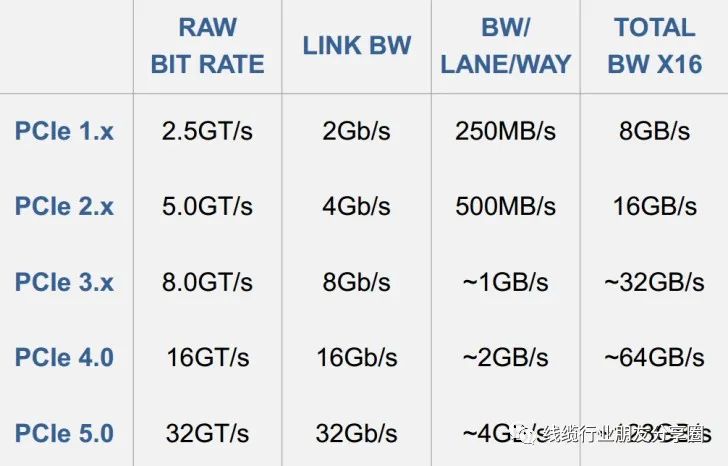

PCI-E 1X(1.0標(biāo)準(zhǔn))采用單向2.5G的波特率進(jìn)行傳輸,由于每一字節(jié)為10位(1位起始位,8位數(shù)據(jù)位,1位結(jié)束位),所以傳輸速率為2.5G/10=250MB/S(250兆字節(jié)每秒),由此可以計(jì)算出來(lái)PCI-E 16X的單向傳輸速率為250MB/S*16=4GB/S,雙向傳輸速率為8GB/S。

PCI-E 2.0規(guī)范:

PCI-E 1X(2.0標(biāo)準(zhǔn))采用單向5G的波特率進(jìn)行傳輸,由于每一字節(jié)為10位(1位起始位,8位數(shù)據(jù)位,1位結(jié)束位),所以單向傳輸速率為5G/10=500MB/S(500兆字節(jié)每秒),由此可以計(jì)算出來(lái)PCI-E 16X(2.0標(biāo)準(zhǔn))的單向傳輸速率為500MB/S*16=8GB/S,雙向傳輸速率為16GB/S,PCI-E 32X(2.0標(biāo)準(zhǔn))的船速速率為32GB/S。

PCI-E 3.0規(guī)范:

PCI-E 1X(3.0標(biāo)準(zhǔn))采用單向10G的波特率進(jìn)行傳輸,由于每一字節(jié)為10位(1位起始位,8位數(shù)據(jù)位,1位結(jié)束位),所以單向傳輸速率為10G/10=1000MB /S(1000兆字節(jié)每秒),由此可以計(jì)算出來(lái)PCI-E 16X(3.0標(biāo)準(zhǔn))的單向傳輸速率為1000MB/S*16=16GB/S,雙向傳輸速率為32GB/S,PCI-E 32X(3.0標(biāo)準(zhǔn))的雙向傳輸速率高達(dá)64GB/S。

PCI-E 4.0規(guī)范:

PCI-E 4.0總線的速率是在PCI-E 3.0的基礎(chǔ)上再翻一倍,單通道單向傳輸為16Gb/s,因此16通道雙向傳輸?shù)乃俾试诶碚撋峡梢赃_(dá)到512Gb/s即64GB/s,另外PCI-E 4.0標(biāo)準(zhǔn)還會(huì)對(duì)PCI-E接口的存儲(chǔ)設(shè)備例如PCI-E固態(tài)硬盤(pán)和PCI-E RAID卡等進(jìn)行優(yōu)化,盡可能發(fā)揮PCI-E總線的低延遲優(yōu)勢(shì)。另外PCI-SIG組織還透露,新的PCI-E標(biāo)準(zhǔn)將包含有外接式PCI-E的規(guī)范,他們將這個(gè)規(guī)范稱之為PCI-E OCuLink,簡(jiǎn)單來(lái)說(shuō)就是類似于英特爾主推的ThunderBolt接口。據(jù)稱,PCI-E OCuLink基于PCI-E 3.0開(kāi)發(fā),將采用銅纜作為連接介質(zhì),可提供最低8Gb/s(PCI-E 3.0 x1)、最高32Gb/s(PCI-E 3.0 x4)的連接速率。

PCI-E 5.0規(guī)范:

在PCIe 5.0將信號(hào)速率提升到32GT/s的時(shí)候,以太網(wǎng)設(shè)備的信號(hào)速率已經(jīng)達(dá)到56Gbps,并正在向112Gbps邁進(jìn)。從速率上來(lái)看,現(xiàn)有的測(cè)量設(shè)備應(yīng)該能夠完全滿足PCIe 5.0信號(hào)的測(cè)試需求。但實(shí)際上PCIe 5.0是NRZ信號(hào),56Gbps以太網(wǎng)信號(hào)是PAM4信號(hào),PCIe 5.0信號(hào)的基頻點(diǎn)反倒更高(16GHz vs 14GHz)

PCI-E 6.0規(guī)范:?PCIe 6.0 規(guī)范,達(dá)到 64 GT/s。近二十年來(lái),PCI Express 技術(shù)一直是事實(shí)上的首選互連。PCIe 6.0 規(guī)范將 PCIe 5.0 規(guī)范 (32 GT/s) 的帶寬和功率效率提高了一倍,同時(shí)提供低延遲和減少的帶寬開(kāi)銷。

?

?

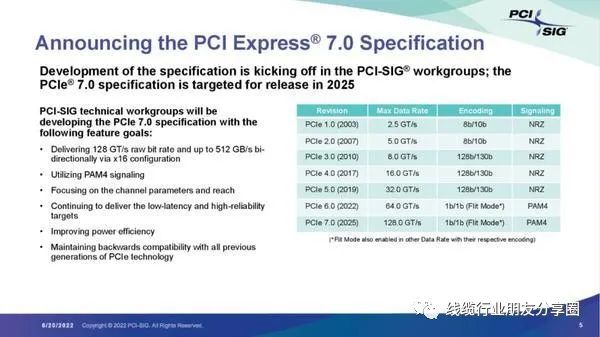

PCI-E 7.0規(guī)范:

最新一代 PCIe 7.0帶寬翻了一番,在一條通道 (x1) 上單向?qū)崿F(xiàn) 128GT / s 或 128Gbps 總吞吐量。綜上所述,在 PCIe x16 插槽上,與獨(dú)立顯卡一樣,雙向總理論吞吐量為 512GB / s。同時(shí),通常與 x4 PCIe 插槽配對(duì)的 NVMe SSD 可提供高達(dá) 64GB / s 的單向速度。最終規(guī)格將于 2025 年發(fā)布.

?

?

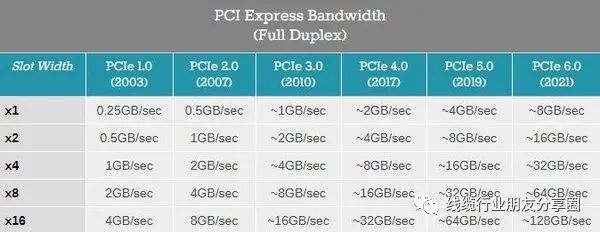

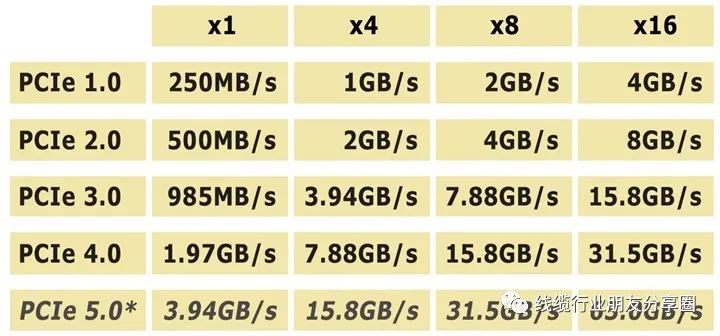

以下是目前發(fā)布的各標(biāo)準(zhǔn)及不同的位寬下速度的對(duì)比:

下表中詳細(xì)展示了PCIe各版本各規(guī)格的單向帶寬/速率。

大家可能都注意到,新版本帶寬翻倍是PCIe的優(yōu)良傳統(tǒng),需要PCIE5.0版本的協(xié)會(huì)技術(shù)規(guī)格,找客服CABLE009索取即可。

PCIe 5.0/6.0 布線將于 2023 年末推出

New style

雖然 PCIe 7.0 正在開(kāi)發(fā)中,但 PCIe 6.0 的第一個(gè)硬件仍在開(kāi)發(fā)中,甚至 PCIe 5.0 設(shè)備也只有不到一年的時(shí)間。因此,在開(kāi)發(fā)核心規(guī)范的同時(shí),PCI-SIG 還在完成規(guī)范的一些輔助領(lǐng)域,特別是布線。預(yù)計(jì)將于今年第四季度發(fā)布。規(guī)格將涵蓋 PCIe 5.0 和 PCIe 6.0(因?yàn)樾盘?hào)頻率不變,PCIe 5.0的目的是簡(jiǎn)單地提高到PCIe 4.0標(biāo)準(zhǔn)的速度,而沒(méi)有任何其他重要的新功能。例如,PCIe 5.0不支持PAM 4信號(hào),只包括使PCIe標(biāo)準(zhǔn)能夠在盡可能短的時(shí)間內(nèi)支持32 GT/s所需的新功能),包括內(nèi)部和外部電纜的規(guī)格。內(nèi)部布線將把設(shè)備連接到系統(tǒng)內(nèi)的其他部分——包括設(shè)備和主板/背板——而外部布線將用于系統(tǒng)到系統(tǒng)的連接。在信號(hào)技術(shù)和絕對(duì)信號(hào)速率方面,PCI Express 落后以太網(wǎng)一代左右。這意味著以太網(wǎng)工作組已經(jīng)解決了高速銅信號(hào)的大部分初始開(kāi)發(fā)問(wèn)題。因此,盡管仍需努力使這些技術(shù)適用于 PCIe,但基本技術(shù)已經(jīng)得到驗(yàn)證,這有助于稍微簡(jiǎn)化 PCIe 標(biāo)準(zhǔn)和布線的開(kāi)發(fā)。

編輯:黃飛

?

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論