在開始了解高速接口的時候,必然會涉及到SerDes。

serdes的知識點實際上非常多,并且很多文章論述的側重點不一樣,有的測重整體,有的著眼細節,我則綜合提取,以幫助跟我一樣的初學者能夠初步建立對SerDes清晰的認識。

1. 簡介

SerDes是Serializer/Deserializer的縮寫,即串行器和解串器,顧名思義是一種將并行數據轉換成串行數據發送,將接收的串行數據轉換成并行數據的”器件“。對于FPGA工程師來說“串并轉換”再熟悉過不過了,只不過SerDes是一種需要數模硬件實現的,用于高速傳輸的“高級”串并轉換器件。至于接口從最初從串口到并口,再回歸到串口的歷史發展,可以閱讀相關的文獻,借此可以了解一下系統同步、源同步的技術瓶頸。目前,商用基于SerDes架構的通信協議最高可實現單通道56Gbps(好像已經可達112Gbps)的速率,在未來高帶寬、低成本的應用領域會越來越廣泛。

SerDes主要具有以下優點:

減少布線沖突(串行,并且無單獨的時鐘線,時鐘嵌入在數據流中,從而也解決了限制數據傳輸速率的信號時鐘偏移問題);

抗噪聲、抗干擾能力強(差分傳輸);

降低開關噪聲;

擴展能力強;

更低的功耗和封裝成本;

題外話:看了文獻之后,才知道PCIE、JESD204B都是基于SerDes的協議,用OSI網絡分層模型來類比的話,SerDes更接近于物理層,并強調了電氣屬性,而PCIE和JESD204B相當于涵蓋數據鏈路層、網絡層和傳輸層,所以SerDes通常又被稱之為物理層(PHY)器件。實際上和很多人沒分清RS232和URAT之間的關系一樣。

2. 整體架構

SerDes有四種架構:

1)并行時鐘SerDes;

2)嵌入式時鐘SerDes;

3)8b/10b編碼SerDes;

4)位交錯SerDes。(注:至于這4種所謂的架構有什么區別,實現有什么特點,我還沒找到專門的文獻來說明)。

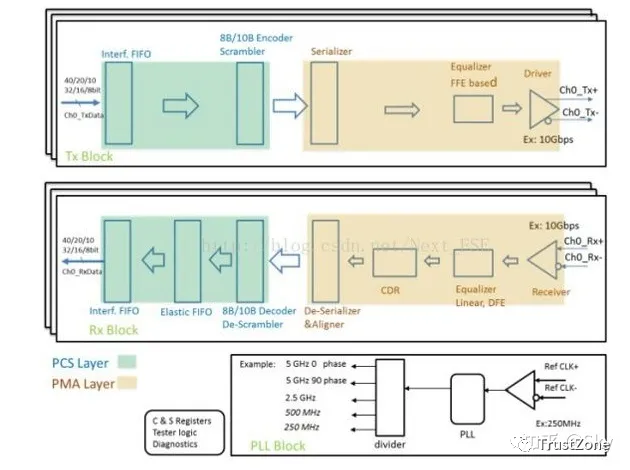

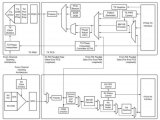

常見的SerDes架構是一種基于8b/10b編碼并且時鐘嵌入進數據流中的架構(是不是就是上面2、3的組合?),主要由物理介質相關子層( PMD)、物理媒介附加子層(PMA)和物理編碼子層( PCS )所組成。如下圖所示:

底色為淺綠色的子模塊為PCS層,負責數據流的編碼/解碼,是標準的可綜合CMOS數字邏輯,可以硬邏輯實現,也可以使用FPGA軟邏輯實現。

底色為淺褐色子模塊是PMA層,是數模混合CML/CMOS電路,負責負責串化/解串化,是理解SerDes區別于并行接口的關鍵。

PMD是負責串行信號傳輸的電氣塊(未畫出)。

PLL模塊(PLL Block)負責產生SerDes各個模塊所需要的時鐘信號,并管理這些時鐘之間的相位關系。

一個SerDes通常還要具調試能力,例如偽隨機碼流產生和比對,各種環回測試,控制狀態寄存器以及訪問接口,LOS檢測,眼圖測試等,所以還需要相應的功能測試模塊。

整個流程可以簡述為:

發送(TX) FPGA軟邏輯(fabric)送過來的并行信號,通過接口FIFO(Interface FIFO),送給8b/10b編碼器(8b/10b encoder)或擾碼器(scambler),以避免數據含有過長連“0”或者連“1”,之后送給串行器(Serializer)進行并->串轉換。串行數據經過均衡器(equalizer)調理,由驅動器(driver)發送出去。

接收(RX) 外部串行信號由線性均衡器(Linear Equalizer)或DFE (Decision Feedback Equalizer,判決反饋均衡)結構均衡器調理,去除一部分確定性抖動(Deterministic jitter)。CDR從數據中恢復出采樣時鐘,經解串器變為對齊的并行信號。8b/10b解碼器(8b/10b decoder)或解擾器(de-scambler)完成解碼或者解擾。如果是異步時鐘系統(plesio-synchronous system),在用戶FIFO之前還應該有彈性FIFO來補償頻差。

注:我發現系統性的把SerDes細節講清楚的文獻并不多,并且有些SerDes接口芯片并不完全是上面這種架構,在實際過程中,各個廠家可能會根據性能做不同的算法優化,具體的模塊可能用到不同的技術,所以不要片面的理解上述架構是Serdes的唯一架構。

3. 發送端模塊說明

3.1 8b/10b編碼器

8b/10b編碼是由IBM于1983年發明的,旨在解決系統互聯以及GB以太網傳輸的問題。是指將8b的數據通過某種編碼規則擴展成10b,保證數據流中的“0”和“1”數量基本一致,通過降低效率來增加傳輸的數據恢復的可靠性。8b/10b 主要具有以下優點:

保證直流(DC)平衡(重點)

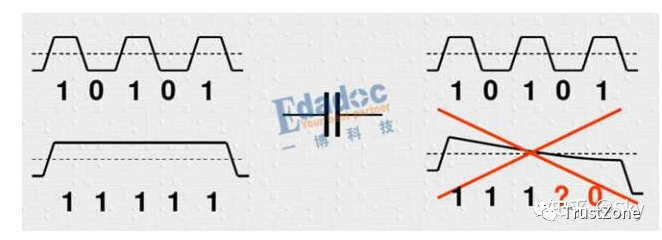

直流平衡是什么意思呢?如上圖所示,由于我們的串行鏈路中會有交流耦合電容,信號頻率越高,阻抗越低,反之頻率越低,阻抗越高。因此上面的情況,當碼型是高頻的時候,基本上可以不損耗的傳輸過去,但是當碼型為連續“0”或者“1”的情況時,電容的損耗就很大,導致幅度不斷降低,帶來的嚴重后果是無法識別到底是“1”還是“0”。因此編碼就是為了盡量把低頻的碼型優化成較高頻的碼型,從而保證低損耗的傳輸過去。

8b/10b編碼方式總輸出位數是10個位,其中“0”與“1”出現的次數總共也僅在三種場合存在,分別為“5個位0與5個位1”、“4個位0與6個位1”、“6個位0與4個位1”。有一個8b/10b編碼的技術專用語“不均等性(Disparity)”,其涵義就是指10個位中位0與位1出現次數的差。換句話說,8b/10b編碼的“Disparity”就僅有“+2”(4個位0與6個位1)、“+0”(5個位0與5個位1)以及“-2”(6個位0與4個位1)三種狀況。

有利于提取時鐘 時鐘恢復是依賴于“電平跳變沿“(后面會介紹),所以平衡”0“和”1“,可以簡化了時鐘恢復,降低了接收機成本。

方便錯誤檢查 8B/10B編碼采用冗余方式,將8位的數據和一些特殊字符按照特定的規則編碼成10位的數據,根據這些規則,能檢測出傳輸過程中單個和多個比特誤碼。

有關8b/10b編碼的編碼算法可以進一步查閱相關文獻。在SerDes中長常用編碼方式除了8b/10b編碼外,還有64b/66b編碼等;

3.2 擾碼

擾碼是一種將數據重新排列或者進行編碼以使其隨機化的方法,但是必須能夠解擾恢復。我們希望打亂長的連“0”和長的連“1”序列,將數據隨機化。擾碼產生是通過循環移位寄存器來實現的,而擾碼生成多項式決定循環移位寄存器的結構。那么對信號加干擾有什么好處?

解決EMI問題 當數據重復傳輸時,能量就會集中在某一頻率上,產生EMI噪聲;數據經過加擾后,能把集中的能量分散開,幾乎變成白噪聲。

有利于提取時鐘

同時又擴展了基帶信號頻譜,起到加密的效果

總結到這里,看網友有提問,也提醒了我。問題是:在SerDes中先進行8b/10b編碼之后再進行擾碼,感覺兩個的作用類似,只是擾碼進一步增加“0”和“1”的隨機性,還有沒有其他更重要的作用?先加擾再編碼有沒有問題?初學者總有很多疑問。

3.3 串行器/解串器

串行器Serializer把并行信號轉化為串行信號。Deserializer把串行信號轉化為并行信號。一般地,并行信號為8 /10bit或者16/20bit寬度,串行信號為1bit寬度(也可以分階段串行化,如8bit->4bit->2bit->equalizer->1bit以降低equalizer的工作頻率)。

Serializer/Deserializer的實現采用雙沿(DDR)的工作方式,利用面積換速度的策略,降低了電路中高頻率電路的比例,從而降低了電路的噪聲。

接收方向除了Deserializer之外,一般帶有還有對齊功能邏輯(Aligner)。相對SerDes發送端,SerDes接收端起始工作的時刻是任意的,接收器正確接收的第一個 bit可能是發送數據的任意bit位置。因此需要對齊邏輯來判斷從什么bit位置開始(哪里開始算是第一個數據),以組成正確的并行數據。對齊邏輯通過在串行數據流中搜索特征碼字(Alignment Code)來決定串并轉換的起始位置,這就需要用到了8b/10b的控制字符集,也就是我們常說的“K”字符,常見的什么K28.5、K28.0、K28.3、K28.4等,在JESD204B中他們又稱/K/、/R/、/A/、/Q/字符。

3.4 前向反饋均衡(feed-forward equalization/equalizer)

SerDes信號從發送芯片到達接收芯片所經過的路徑稱為信道(channel),包括芯片封裝、pcb走線、過孔、電纜、連接器等元件。從頻域看,信道可以簡化為一個低通濾波器(LPF)模型,如果SerDes的速率大于信道的截止頻率,就會一定程度上損傷信號(高頻被濾掉了,數字信號邊沿會變得平滑)。均衡器的作用就是補償信道對信號的損傷。

發送端的均衡器采用FFE(Feed forward equalizers)結構,從頻域上看,FFE是一個高通濾波器(容易理解,信道損傷是一個低通濾波器,會抑制高頻,那么均衡就補償高頻)。從時域上看,又叫加重器(emphasis)。加重分為去加重(de-emphasis)和預加重(pre-emphasis)。De-emphasis 降低差分信號的擺幅(swing)。Pre-emphasis增加差分信號的擺幅。由于目前芯片都需要追求降低功耗,所以大部分使用de-emphasis的方式,加重越強,信號的平均幅度會越小。

4. 接收端模塊說明

4.2 接收均衡器

4.2.1 線形均衡器(Linear Equalizer)

接收端均衡器的目標和發送均衡器是一致的。對于低速(<5Gbps)SerDes,通常采用連續時間域、線性均衡器實現如尖峰放大器(peaking amplifier), 均衡器對高頻分量的增益大于對低頻分量的增益。

4.2.2 裁決反饋均衡器(Decision Feedback Equalizer-DFE)

對于高速(>5Gbps)SerDes,由于信號的抖動(如ISI相關的確定性抖動)可能會超過或接近一個符號間隔(UI,Unit Interval),單單使用線性均衡器不再適用。線性均衡器對噪聲和信號一起放大,并沒有改善SNR或者說BER。對于高速SerDes,采用一種稱作DFE的非線性均衡器。DFE通過跟蹤過去多個UI的數據(history bits)來預測當前bit的采樣門限,從而預測碼間干擾。DFE只對信號放大,不對噪聲放大,可以有效改善SNR。

不論是發送端還是接收端的均衡器,本質上都是高通濾波器,因為數字信號采樣都希望邊沿越抖越好,邊沿變緩之后就會產生碼間干擾。

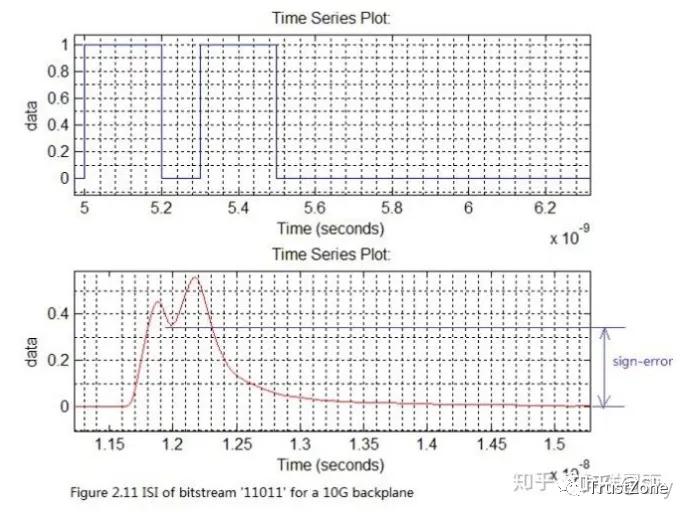

如下圖所示,系統傳輸一個“11011”的碼流,如果沒有均衡器,信號受到信道損傷,信號展寬,出現碼間干擾,導致中間的“0”,無法被檢測到。

DFE設計的關鍵是確定DFE系數,如果DFE的系數接近信道的脈沖相應,就可以到的比較理想的結果。但是信道是一個時變的媒介,比如溫度電壓工藝的慢變化等因素會改變信道的特性。因此DFE的系數需要自適應算法,自動撲獲和跟隨信道的變化。這也是實際應用中DFE功能開啟的時候,做環境試驗的結果很多時候會出問題,因為DFE在信道特性變化的時候,自適應的速度沒有跟上。DFE系數自適應算法非常學術,每個廠商的算法都是保密的,不對外公布。

4.3 時鐘數據恢復(CDR)

最開始接觸SerDes的是,說“沒有單獨的時鐘線,時鐘嵌入在數據流中的”,腦海里第一反應就是在數據中插入一定規則的編碼代表時鐘的高電平或者低電平,回頭一想,那時鐘頻率不就遠低于數據的采集頻率了嗎?實際上,所謂的“時鐘嵌在數據中”的意思,是時鐘嵌在數據的跳變沿里。不難理解,極端情況下,假設一串數據流是"1"和"0"交替發送,那這不就是一個時鐘了嗎。

CDR( Clock and Data Recovery)即時鐘和數據的恢復,是SerDes設計中非常重要的環節。CDR常用的技術有基于數字鎖相環(PLL)和基于相位插值器兩種。當數據經過時,CDR就會捕獲數據邊沿跳變的頻率,如果數據長時間沒有跳變,CDR就無法得到精確的訓練,CDR采樣時刻就會漂移,可能采到比真實數據更多的“0”或“1”。這就是為什么我們在發送的時候采用8b/10b編碼或擾碼來避免重復出現“0”或“1”,原因之一也在此。所以CDR有一個指標叫做最長連“0”或連“1”長度容忍(Max Run Length或者Consecutive Identical Digits)能力。

恢復了時鐘之后,需要恢復數據。第一步首先要將恢復出來的時鐘與數據的邊緣進行對齊,然后再將數據給讀出來。在硬件原理上,使用PLL電路以及觸發器即可。

以上是總結的有關SerDes的基礎知識,希望能幫助像我一樣的初學者建立初步的認識。SerDes每一個模式深入下去都有很多硬件、信號完整性(包括眼圖的評價機制)的知識,想做到非常清晰的認識有一定的難度。目前,對于FPGA工程師來說,SerDes作為phy芯片或者集成在IP核中,先掌握應用,需要的時候再深入

審核編輯:黃飛

?

電子發燒友App

電子發燒友App

評論