游戲愛好者或者硬件愛好者肯定都對顯卡有一定的了解,顯卡一般插在主板上的擴展槽上面,顯卡和CPU交互的方式就是通過PCIE協議,現在常見的擴展槽就是PCIE槽,很多人了解PCIE但也有很多人只是聽過不知道具體的功能含義,今天我們就來淺談下PCIE。 ?

PCIE的發展史

PCIExpress(PCIe)的發展歷史可以追溯到PCI(Peripheral Component Interconnect)的起源。PCI是Intel于1991年提出的一種計算機總線標準,主要用于計算機連接其外圍設備,如硬盤控制器、聲卡、顯卡和網卡等。這些設備都使用PCI插槽來連接到計算機的主板上。隨著Intel Pentium處理器的誕生,PCI總線得以迅速發展。

第一個英特爾奔騰處理器 最初的PCI總線工作在33MHz頻率之下,傳輸帶寬達到132MB/s,這基本上滿足了當時處理器的發展需要。然而,隨著對更高性能的要求,PCI總線技術也在不斷發展。后來提出了將PCI總線的頻率提升到66MHz,使得傳輸帶寬能達到264MB/s。

然而,PCI總線速率的瓶頸逐漸顯現,特別是在服務器和工作站中,高速磁盤和網絡適配器對更高帶寬的需求日益迫切。為了滿足這種需求,PCI技術開始往更高速率的方向發展,形成了PCI-X新總線標準。PCI-X最大支持到64bit/533M,但在其第二代之后,仍存在一定的局限性。

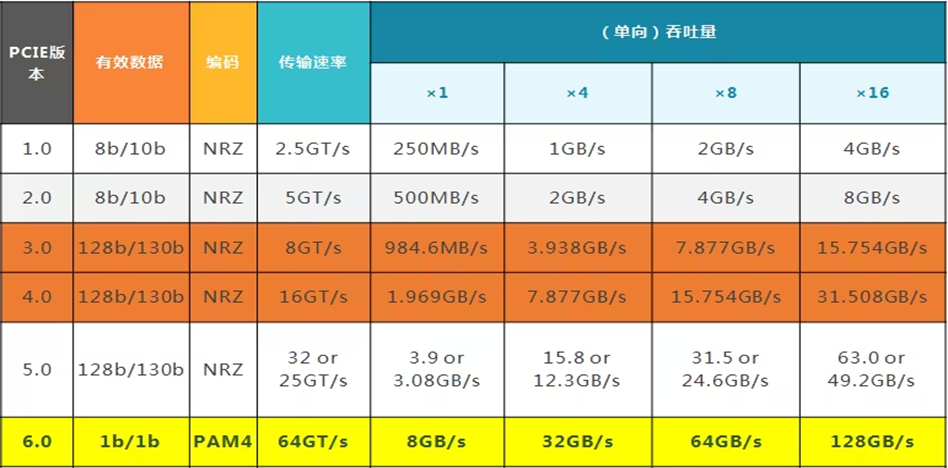

隨后,PCIe作為PCI的串行總線版本被推出。從2003年開始,PCIe標準不斷得到更新和升級。PCIe 1.0在2003年推出,支持更高的數據傳輸速率。隨后,PCIe 2.0在2007年推出,進一步提升了傳輸速率。然而,之后幾年PCIe的發展相對緩慢,直到2010年PCIe 3.0的推出,它支持更高的速率,最高可以達到8GT/s。

2017年,PCIe 4.0標準發布,進一步提升了PCI Express總線的帶寬,最高可以達到16GT/s。緊接著,2019年PCIe5.0標準發布,成為當時最新的PCI Express標準,最高可以達到32GT/s的傳輸速率。

2021年,PCI-SIG 組織發布PCIe 6.0 是最新一代的 PCI Express 接口標準,速率達到64GT/s。

而在最近的2024年,PCI-SIG組織已經公布了PCIe 7.0標準。根據這一標準,PCIe 7.0將在一條通道(x1)上單向實現128GT/s或128Gbps速率。新的規范預計在2025年正式推行。在x16雙向傳輸模式下,PCIe 7.0的速率高達512GB/s,這對于云端應用、大數據中心等領域來說,無疑是一個巨大的飛躍。

總的來說,PCIe的發展歷史體現了計算機技術的不斷進步和發展,從最初的并行總線到現在的串行總線,從較低的傳輸速率到如今的極高傳輸速率,滿足了不斷增長的數據處理和傳輸需求。

PCIE歷代速率一覽表

PCIE的使用場景

? PCIe(Peripheral Component Interconnect Express)因其高帶寬、低延遲和靈活性等特點,在眾多計算和數據密集型場景中廣泛應用。以下列舉了一些典型的PCIe使用場景:

圖形處理單元(GPU顯卡):

1、游戲和圖形渲染:PCIe插槽用于連接高性能顯卡,為桌面和工作站提供高質量的游戲畫面渲染和三維建模能力。

GPU加速卡通過PCIe接口與主機相連,用于大規模并行計算,加速機器學習模型的訓練過程。

高速存儲:

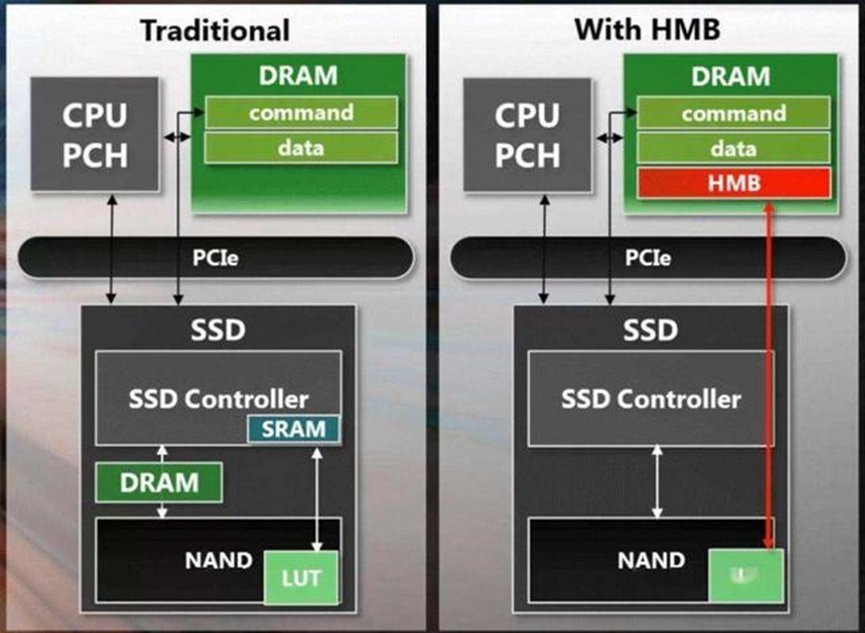

1、NVMe SSD:

PCIe SSD(非易失性內存express)可以利用PCIe通道直接與CPU通信,提供極高的讀寫速度,用于大型數據庫、高性能計算集群以及對存儲速度要求極高的應用程序。

網絡接口卡(NIC):

高速網絡適配器通過CIe接口接入服務器或工作站,實現萬兆或更高速度的以太網連接,滿足數據中心內部或互聯網之間的高速數據傳輸需求。

加速卡與協處理器:

FPGA加速卡、智能網卡、加密/解密加速卡等通過PCIe連接到系統,提供特定領域的加速計算,如金融交易、密碼破解、大數據分析等。

高級的多通道音頻和視頻輸入輸出設備通常使用PCIe接口,以實現高清視頻流的實時處理和傳輸。

科研儀器與工業控制:

在實驗室環境和工業自動化領域,高端測量設備和控制器可通過PCIe接口與計算機整合,實現高效的數據采集和處理。

總之,PCIe在任何需要高速、低延遲數據交換的場合都有廣泛的應用,尤其是那些需要大量并發數據處理、高速存取或高吞吐量網絡連接的場景。隨著PCIe規范的持續演進,其帶寬和性能不斷提升,進一步拓寬了其在現代計算架構中的應用范圍。

PCIE的架構

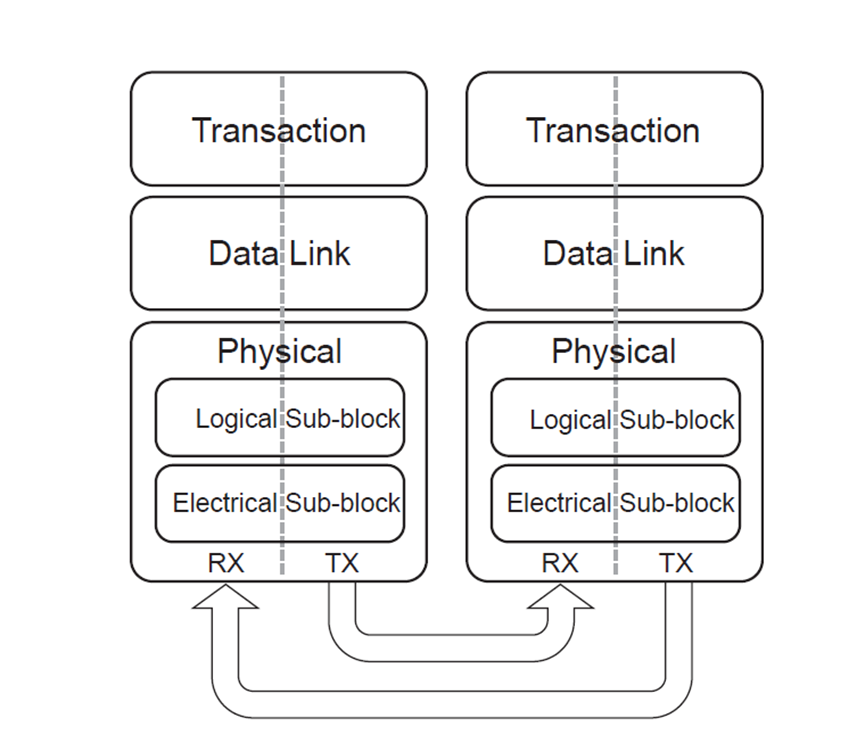

PCIE的結構是一種分層的設計,旨在確保模塊化和靈活性,同時提供強大的性能。以下是PCIe結構的詳細說明:

1. 物理層(PhysicalLayer)

物理層是PCIe架構的底層,負責處理實際的信號傳輸。物理層的詳細描述包括以下幾個核心部分:

(1)物理邏輯子層(PhysicalLayer Logic Sublayer, PLSL)

PLSL負責對接數據鏈路層的數據,并將其轉換為物理層可以處理的格式。這一層處理數據包的序列化和反序列化、信號的編碼與解碼,以及數據的打包和解包。

(2)物理編碼子層(PhysicalCoding Sublayer, PCS)

PCS負責對數據進行編碼,以適應物理介質的傳輸特性,如在PCIe中使用8b/10b編碼或更高級別的128b/130b編碼來保證足夠的DC平衡和時鐘恢復能力。

(3)物理介質附屬子層(PhysicalMedium Attachment Sublayer, PMAS)

這一層關注信號在物理媒介上的傳輸,包括信號的預加重、均衡、去加重等處理,以優化信號質量和克服傳輸距離所帶來的損耗。

(4)物理介質相關子層(PhysicalMedium Dependent Sublayer, PMDS)

PMDS定義了具體的物理接口規范,如電氣特征、電纜類型、連接器標準、信號品質參數等,確保不同制造商生產的組件能夠相互兼容。

(5)物理層信號和時序

PCIe物理層采用差分信號傳輸,降低電磁干擾并提高信號完整性,通過正負信號對來表示二進制數據,從而在高速傳輸時仍能保持良好的信號質量。

(6)鏈路訓練與狀態機(LinkTraining and Status State Machine, LTSSM

LTSSM是一個重要的組成部分,它負責初始化和管理PCIe鏈路的狀態,包括速率協商、位鎖定、符號鎖定、電氣均衡設置以及鏈路激活和退出的過程。

(7)物理層包(PhysicalLayer Packet, PLP)

物理層還生成和處理一些特殊類型的包,如用于鏈路訓練和管理的命令集(OrderedSets),這些不是常規的數據包,而是用于維護和優化鏈路性能的信號序列。

(8)電氣子層

包括了發射和接收電路,負責生成和識別信號,并確保信號在物理線路上傳輸時符合規范的要求,包括但不限于信號幅度、邊沿速度、噪聲容限和信號衰減等問題。

2. 數據鏈路層(DataLink Layer)

數據鏈路層位于物理層之上,負責處理數據包的封裝、解碼和錯誤檢測。主要包括以下方面:

(1)幀化與去幀化

數據鏈路層將事務層傳遞下來的TLPs(TransactionLayer Packets)幀化,以便在物理層上進行傳輸。同時,接收端的數據鏈路層將接收到的幀解碼成原始的TLPs,然后傳遞給事務層。

(2)錯誤檢測與校正

數據鏈路層通過CRC(循環冗余檢查)等算法對TLPs進行錯誤檢測。如果檢測到錯誤,數據鏈路層會根據協議規定采取相應的錯誤處理措施,比如請求重發。

(3)流量控制

數據鏈路層使用Credit-based流控機制來防止發送方的數據淹沒接收方。每發送一個TLP,接收方就會消耗一個Credit,而發送方只有在擁有足夠Credit的情況下才能發送下一個TLP。

(4)鏈路狀態管理

數據鏈路層負責監控和管理鏈路的狀態,包括鏈路的訓練、配置和維護等。此外,數據鏈路層還負責鏈路的恢復和重新訓練過程。

(5)鏈路功耗管理

PCIe支持多種低功耗狀態,數據鏈路層參與管理這些狀態,以降低系統的能耗。例如,當沒有數據傳輸時,鏈路可以被置于低功耗狀態。

(6)鏈路層報文(LLPs, Link Layer Packets)

數據鏈路層定義了自己的報文格式,用于執行特定的控制和狀態管理任務。LLPs通常包括用于鏈路初始化、訓練、狀態報告和錯誤處理的報文。

(7)DLLP(DataLink Layer Packet)

DLLP是一種特殊的鏈路層報文,用于在設備和控制器之間傳送流量控制信息和其他控制消息。DLLP的開銷很小,通常只包含8字節,因此對性能的影響非常有限。

3. 事務層(TransactionLayer)

事務層是PCIe結構中的第三層,它負責處理事務級的操作,如讀取、寫入和I/O操作。幾個主要功能:

(1)TLP(TransactionLayer Packet)處理

事務層的主要職責是創建、處理和解析TLPs。TLPs是封裝了PCIe事務數據的包,它們包含了必要的頭部信息,如命令類型、地址、長度和其他控制信息。

(2)命令與響應處理

事務層支持各種類型的數據傳輸命令,包括讀(Read)、寫(Write)、配置讀(Config Read)、配置寫(Config Write)等。對于每種操作,事務層都會生成相應的TLPs,并在數據傳輸完成后生成相應的完成狀態TLPs。

(3)虛擬通道(VC,Virtual Channel)管理

為了提高帶寬利用率和響應時間,事務層提供了多通道(通常是兩個)的并發數據傳輸能力。每個虛擬通道都有自己的Credit池和優先級,使得不同的流量可以獨立地被管理和調度。

(4)地址翻譯

事務層負責將軟件層面的內存地址轉換為PCIe地址空間,包括事務層格雷碼地址。這使得TLPs能夠在PCIe網絡上正確路由。

(5)數據緩沖與分段

為了適應物理層的數據傳輸要求,事務層會對較大的數據塊進行分段處理,并將其存儲在緩沖區中。這樣可以確保數據的連續性和完整性。

(6)流控制

事務層通過與數據鏈路層交互來實施流控制機制。這保證了發送方不會因為發送速度過快而導致接收方緩沖區溢出。

(7)事務排序

事務層負責保證數據按照正確的順序進行傳輸,特別是在存在多個并發事務時,以確保數據的正確性和一致性。

(8)錯誤處理

事務層能夠檢測和處理一些傳輸錯誤,例如地址錯誤、大小錯誤或者無效的操作等。對于無法糾正的錯誤,事務層會向上游發送錯誤報告

4. 設備層和應用層

在事務層之上,是設備層和應用層。這些層次提供了對PCIe設備的抽象和接口,使得上層軟件能夠方便地與PCIe設備進行交互。設備層定義了PCIe設備的特定屬性和功能,而應用層則提供了對這些功能的訪問和使用。

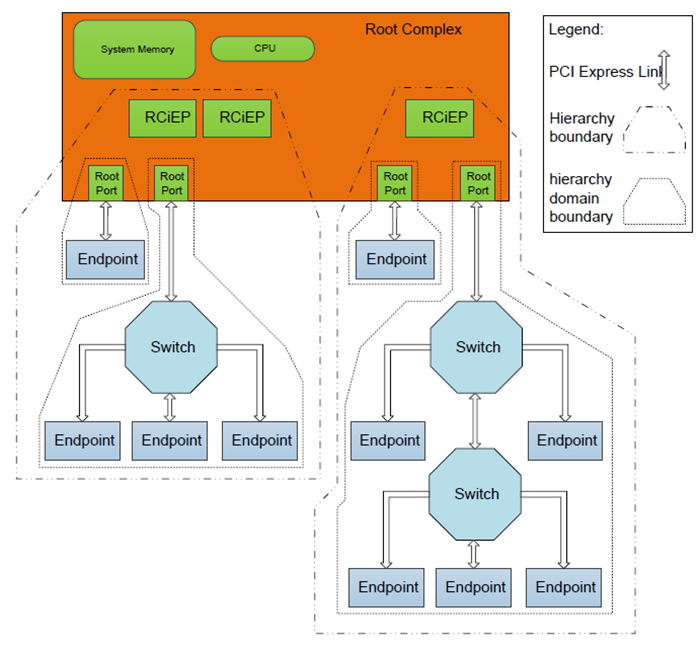

? 5. 端點(Endpoints)和根聯合體(Root Complex)

在PCIe系統中,端點(Endpoints)是實際的數據源或數據目的地,它們可以是各種PCIe設備,如顯卡、網卡等。根聯合體(Root Complex)則是連接CPU和內存的子系統,它作為PCIe系統的主機,負責管理PCIe總線上的設備,并協調它們之間的數據傳輸。

在復雜的PCIe系統中,交換機和橋接器用于擴展總線的范圍,連接更多的設備。交換機用于在多個PCIe設備之間提供數據通道,而橋接器則用于連接不同類型的總線,實現不同總線之間的通信。

總體來說,PCIe的結構設計充分考慮了模塊化和靈活性,使得不同層次的組件可以獨立演進和擴展。這種設計確保了PCIe能夠滿足不斷變化的應用需求,并提供持續的性能提升。

PCIE未來發展趨勢

PCIE未來的發展趨勢主要集中在以下幾個方面:

1、更高的傳輸速率:隨著數據中心和高性能計算需求的增加,PCIe標準的傳輸速率將繼續提升。例如,PCIe 5.0標準相比于PCIe 4.0,帶寬翻倍,而正在開發中的PCIe 6.0和PCIe 7.0將進一步大幅提高速率。

2、更低的延遲:為了滿足實時計算和網絡通信的需求,PCIe的未來發展將致力于減少傳輸延遲,提高數據處理效率。

3、能效優化:隨著綠色計算和可持續發展的重視,PCIe技術的能效比將成為重要指標。未來的發展將著重于降低能耗,特別是在空閑或低負載狀態下。

4、增強的虛擬通道功能:虛擬通道技術允許PCIe設備在多個通道上同時進行數據傳輸,提高帶寬利用率。未來的PCIe版本可能會進一步增強VC的功能,提供更多的通道以及更復雜的調度策略。

5、更好的兼容性與互操作性:隨著不同代數的PCIe設備并存,確保新舊設備間的兼容性和互操作性將是PCIe發展的關鍵。

6、集成安全特性:為了應對日益增長的安全威脅,PCIe未來可能會集成更多的安全特性,如硬件加密和認證機制,以保護數據傳輸過程中的安全性。

7、擴展應用場景:PCIe不僅應用于傳統的計算機和服務器領域,還將拓展至更多新興領域,如汽車電子、物聯網設備等,以滿足這些領域的特定需求。

綜上所述,PCIe的未來發展將圍繞提升性能、降低功耗、增強安全性以及擴大應用范圍等方面展開。隨著技術的不斷進步,PCIe將繼續作為連接各種硬件組件的關鍵橋梁,支撐著現代計算和通訊技術的發展。

審核編輯:黃飛

?

電子發燒友App

電子發燒友App

評論