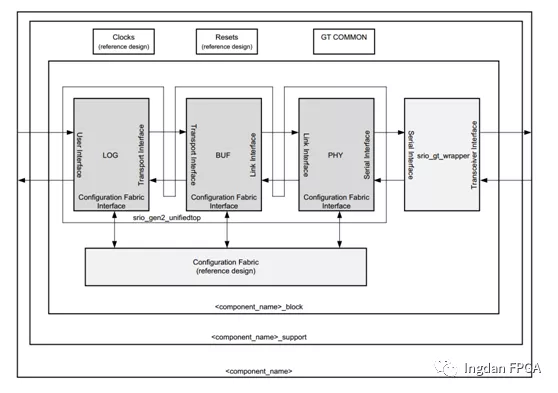

本文介紹一個(gè)FPGA常用模塊:SRIO(Serial RapidIO)。SRIO協(xié)議是一種高速串行通信協(xié)議,在我參與的項(xiàng)目中主要是用于FPGA和DSP之間的高速通信。有關(guān)SRIO協(xié)議的詳細(xì)介紹網(wǎng)上有很多,本文主要簡(jiǎn)單介紹一下SRIO IP核的使用和本工程的源代碼結(jié)構(gòu)。

2023-12-12 09:19:08 855

855

名為XMM8060,兩款5G基帶芯片將用于2019年上半年問(wèn)市的5G智能手機(jī)。 在5G標(biāo)準(zhǔn)凍結(jié)后,華為率先在巴塞羅那世界移動(dòng)通信大會(huì)(MWC)發(fā)布首款5G商用芯片--巴龍5G01(Balong 5G01),成為全球第三家發(fā)布5G商用基帶芯片廠.

2018-02-27 07:06:46 2642

2642 6657的SRIO設(shè)計(jì)要注意哪些?

2016-10-10 23:18:10

Keystone_SRIO_Init(&srio_cfg);之后,接收即終止了,之后也沒(méi)辦法繼續(xù)接收FPGA傳輸?shù)臄?shù)據(jù)。而此時(shí)DSP可以正常向FPGA傳輸數(shù)據(jù)。

??????? 不知道是不是因?yàn)闆](méi)有添加

2018-06-21 13:16:48

; FPGA

? ? ? ? 1、STK中的external line loopback工作方式好像滿足我的需求,但似乎前提是連接雙方必須在SRIO協(xié)議基礎(chǔ)上建立物理層的連接才可以進(jìn)行測(cè)試。由于FPGA端

2018-06-21 06:25:29

各位大佬,你們好。我現(xiàn)在使用TI官方的6678 bootloader源碼,改造后實(shí)現(xiàn)以下功能:1.通過(guò)以太網(wǎng)加載程序;2.能夠boot成功;3.以太網(wǎng)功能正常。但是我遇到一個(gè)比較棘手的問(wèn)題,就是當(dāng)

2021-09-23 09:16:48

各位專家好!請(qǐng)問(wèn):我現(xiàn)在想通過(guò)6678的SRIO接收來(lái)自FPGA的數(shù)據(jù),DSP作為從屬。用的是論壇給的KI_STK_V1.1的SRIO例程,在test between 2 DSPs的程序段里修改

2019-01-11 07:33:39

IP CORE SRIO 2.1 ENDPOINT ECP3

2023-03-30 12:02:57

SITE LICENSE SRIO 2.1 ECP3

2023-03-30 12:03:00

各位好!

? ? ? ?參考Ti給的例程,發(fā)現(xiàn)SRIO中斷是直接配置寄存器,然后再SRIO_vector.asm文件中完成中斷服務(wù)函數(shù)入口的映射,而主機(jī)PC和DSP的交互是通過(guò)利用CSL庫(kù)函數(shù)來(lái)完成中斷配置,我想問(wèn)一下:兩種中斷配置方式能同時(shí)寫在同一個(gè)函數(shù)里面嗎?

謝謝!

2018-06-21 08:43:37

的,uicompletioncode是LSU_STAT中的。這句程序是函數(shù)Keystone_SRIO_wait_LSU_completion的。謝謝。。。

2018-06-21 06:46:55

C6678和C6455使用SRIO通信,1x4p模式,3.125G,其中C6678使用TI的PDK中SRIO LLD

發(fā)現(xiàn)C6455發(fā)送過(guò)快時(shí)候C6678的接收緩存不夠,觸發(fā)StarvationQ

2018-06-21 09:01:47

專家好: 調(diào)試接口時(shí)經(jīng)常會(huì)出現(xiàn)重新load程序的情況,發(fā)現(xiàn)如果SRIO雙方已經(jīng)進(jìn)行數(shù)據(jù)通信,重新加載程序進(jìn)行SRIO初始化后,srio鏈路不通了,需要重新斷電重連,這樣調(diào)試起來(lái)比較浪費(fèi)時(shí)間,請(qǐng)問(wèn)有什么好的方法,可以節(jié)省調(diào)試時(shí)間

2019-01-07 11:15:23

現(xiàn)在,我在ISE13.1軟件中使用srio_v5_6 Ip內(nèi)核。我使用CORE生成器為X6VLX240T-1156-1設(shè)備生成一個(gè)srio_v5_6 IP內(nèi)核。然后我用ISE13.1軟件打開

2018-10-08 11:10:47

1.我使用的是c6670的例子工程SRIO_LoopbackDioIsrexampleproject,在evm板子上跑了一下,從運(yùn)行完畢打印出來(lái)的log中發(fā)現(xiàn)只有核0執(zhí)行了dio,而核1沒(méi)有運(yùn)行

2018-06-21 14:01:07

請(qǐng)教SRIO通信問(wèn)題,6672和FPGA的SRIO通信,2個(gè)lane連接,現(xiàn)象如下:

?(1)兩端都配置成2x,3.125G,F(xiàn)PGA顯示port initial成功,link initial失敗。

(2)把6672配置成2個(gè)1x,F(xiàn)PGA顯示初始化成功,但無(wú)法進(jìn)行數(shù)據(jù)通信。

請(qǐng)教是什么問(wèn)題,謝謝。

2018-06-21 13:52:27

請(qǐng)問(wèn),6678SRIO自帶的loopback例程怎么把內(nèi)循環(huán)改為外循環(huán)?除了要把loopback模式設(shè)為normal模式外還要怎么改?

2018-06-21 17:47:11

1、SRIO門鈴中斷的相關(guān)寄存器DOORBELL[0-3]_ICSR/ICCR/ICRR,其中的0-3是不是與port對(duì)應(yīng)?

2、通過(guò)ICRR配置doorbell到INTDST的映射時(shí),發(fā)現(xiàn)

2018-06-21 02:35:54

徑:D:\ti\pdk_C6678_1_1_2_5\packages\ti\csl\docs\doxygen\html\csl__srio_aux_8h.html查看相關(guān)函數(shù)定義和功能鏈接速率配置

2020-09-23 11:08:36

徑:D:\ti\pdk_C6678_1_1_2_5\packages\ti\csl\docs\doxygen\html\csl__srio_aux_8h.html查看相關(guān)函數(shù)定義和功能鏈接速率配置

2020-09-08 10:36:41

我們有一塊帶有 MPC8640D PowerPC 架構(gòu)處理器的定制板。一個(gè) sRIO 開關(guān)連接到這個(gè)處理器。在加載我們的自定義 Linux 映像時(shí),我們無(wú)法初始化 sRIO,并且出現(xiàn)分段錯(cuò)誤。 附上日志文件供您參考。請(qǐng)找到突出顯示的 sRIO init 失敗部分請(qǐng)幫我解決這個(gè)問(wèn)題

2023-04-18 07:00:39

保存在資料盤中的Demo\\DSP\\XQ_SRIO_x4LANE_5Gbps文件夾下。1.1.2功能簡(jiǎn)介實(shí)現(xiàn)DSP與ZYNQ之間SRIO接口傳輸功能。DSP與ZYNQ之間SRIO通道寬度為4,每個(gè)

2023-02-21 14:51:50

在資料盤中的Demo\DSP\XQ_SRIO_x4LANE_5Gbps文件夾下。1.1.2 功能簡(jiǎn)介實(shí)現(xiàn)DSP與ZYNQ之間SRIO接口傳輸功能。DSP與ZYNQ之間SRIO通道寬度為4,每個(gè)SRIO

2023-02-02 21:43:20

我想把c6455 srio配置為1P4X的模式,是不是這種模式下只使用一個(gè)port,那么我在設(shè)置寄存器SERDES_CFGRXn_CNTL和SERDES_CFGTXn_CNTL的時(shí)候,只使能

2019-01-21 15:42:20

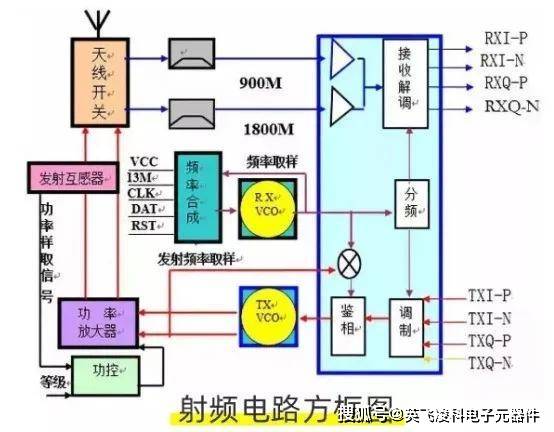

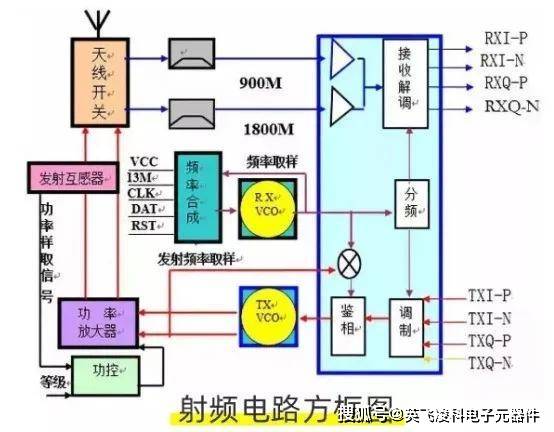

的系帶信號(hào),或?qū)邮盏降南祹盘?hào)進(jìn)行解碼.發(fā)射時(shí),將音頻信號(hào)編譯成基帶碼,發(fā)射基帶碼;接收時(shí),將收到的基帶碼進(jìn)行解碼,轉(zhuǎn)換為音頻信號(hào),即電話通話功能.同時(shí)也負(fù)責(zé)地址信息(手機(jī)號(hào),網(wǎng)站地址),文字信息(短信,網(wǎng)站文字),圖片信息的編解...

2021-07-28 06:42:24

您好,我對(duì)“基帶”的定義有一些疑問(wèn)。我現(xiàn)在通過(guò)從設(shè)計(jì)指南中選擇設(shè)計(jì),在ADS2011中使用負(fù)載牽引仿真。在一個(gè)音調(diào)和兩個(gè)音源/負(fù)載牽引仿真中,參數(shù)“Z_Src_Baseband”或

2019-08-06 14:46:43

物理層標(biāo)準(zhǔn)IEEE 802.11a為實(shí)例,研究如何在FPGA上實(shí)現(xiàn)一個(gè)OFDM通信系統(tǒng)的基帶收發(fā)機(jī)。《基于XILINX FPGA的OFDM通信系統(tǒng)基帶設(shè)計(jì)》在系統(tǒng)地給出了收發(fā)機(jī)模塊劃分的基礎(chǔ)上,對(duì)每個(gè)

2012-11-02 11:09:37

電路功能與優(yōu)勢(shì)該電路是靈活的頻率捷變中頻至基帶接收機(jī)。中頻和基帶上的可變?cè)鲆?b class="flag-6" style="color: red">用于調(diào)整信號(hào)電平。 ADRF6510 基帶ADC驅(qū)動(dòng)器還包括可編程低通濾波器,可消除通道外阻塞和噪聲。 此濾波器的帶寬

2019-07-05 07:27:55

Spartan6 SRIO,clk pad是浮動(dòng)的,有沒(méi)有辦法使用SRIO

2019-08-01 08:59:05

挑戰(zhàn)。這些收發(fā)器可為模擬RF信號(hào)鏈提供數(shù)字接口,允許輕松集成到ASIC或FPGA,進(jìn)行基帶處理。基帶處理器(BBP)允許在終端應(yīng)用和收發(fā)器設(shè)備之間的數(shù)字域中處理用戶數(shù)據(jù)。

2019-09-19 06:20:59

你好,我想請(qǐng)教一個(gè)問(wèn)題,就是我用6474 SRIO,每次發(fā)送完一個(gè)4Kbyte包后,我需要SRIO響應(yīng)一個(gè)中斷。而不是像例程這樣:/* Wait for the completion

2018-06-21 14:20:09

您好!

? ? ? 兩塊6678DSP通過(guò)SRIO建立連接,對(duì)于SRIO來(lái)說(shuō):

? ? ?1.這兩塊DSP的地址是怎樣映射的?

? ? ? 2.映射是怎樣建立的?

? ? ?3. 雙方的設(shè)備ID有沒(méi)有參與到映射中來(lái)?

? ? ?4.選擇的輸出端口號(hào)決定了什么?

2018-06-21 09:37:38

目前在調(diào)試多片6678與fpga通過(guò)cps1848交換芯片通信,使用的是論壇中keystone_srio例程調(diào)試過(guò)程中有幾個(gè)問(wèn)題。1.dap向dpga發(fā)數(shù)時(shí)而成功時(shí)而失敗,失敗時(shí)查看error

2019-06-04 11:03:34

現(xiàn)在使用的是官方提供的:K1_STK_v1.1下SRIO驅(qū)動(dòng),用于測(cè)試SRIO通信。對(duì)原代碼SRIO_Loopback_Mode loopback_mode= SRIO_NO_LOOPBACK;流程

2018-08-03 06:19:00

你好!我現(xiàn)在嘗試實(shí)現(xiàn)FPGA通過(guò)SRIO接口向DSP TMS320C6670發(fā)送數(shù)據(jù),代碼基于CCS5.0下的SRIO_Loopbacktestproject,但發(fā)現(xiàn)在sriodevice_init

2018-08-06 06:38:43

基于IQ解調(diào)器,具有中頻和基帶可變?cè)鲆嬉约翱删幊?b class="flag-6" style="color: red">基帶濾波功能的中頻至基帶接收機(jī)。

2021-05-24 07:00:30

建立標(biāo)準(zhǔn)模板的目的是什么呢?單片機(jī)標(biāo)準(zhǔn)模板建立的操作步驟有哪些?

2022-01-21 07:50:42

如何建立一個(gè)基于STM32標(biāo)準(zhǔn)庫(kù)的工程模板?

2021-11-26 06:28:02

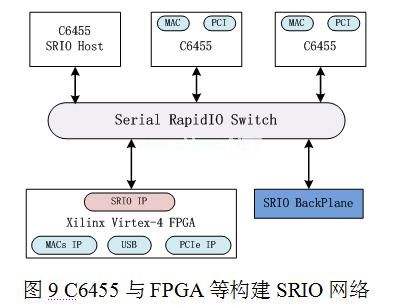

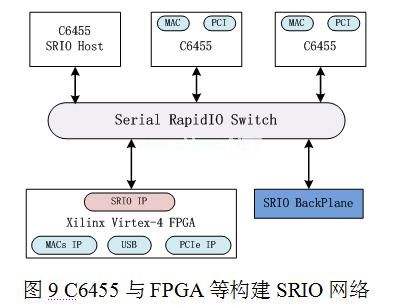

C6455特性是什么?SRIO標(biāo)準(zhǔn)有哪些?如何去實(shí)現(xiàn)C6455間的SRIO通信?

2021-06-02 07:12:34

您好,我最近在看C6474的SRIO。

目前手頭只有TI官方的C6474的SRIO的資料《TMS320C6474 DSP?Serial RapidIO (SRIO)?User's Guide》。但是發(fā)現(xiàn)該文檔讀不懂。

請(qǐng)問(wèn)學(xué)習(xí)SRIO有哪些好的資料?有視頻資料或者中文資料嗎?非常感謝您的指導(dǎo)

2018-06-21 02:35:00

集成了音頻功率放大器。 此外,展訊通信MAX3232EUE+T還為三星GALAXY S III、GALAXY Note和GALAXY Note II提供基帶芯片,支持TD-SCDMA 3G標(biāo)準(zhǔn)。以上

2012-11-09 15:43:30

嗨,我正在使用帶有AWGN注入的Agilent N5182A MXG信號(hào)發(fā)生器,由matlab通過(guò)lan連接控制。我想使用C / N噪聲模式。因?yàn)槲沂褂枚鄠€(gè)基帶發(fā)生器同步功能,我無(wú)法使用觸發(fā)類型為

2019-03-22 07:31:28

本文將從幾種無(wú)線通信系統(tǒng)對(duì)終端基帶芯片的需求開始討論,介紹一種由簡(jiǎn)約納電子公司設(shè)計(jì)完成的適用于2G/3G/4G的軟件無(wú)線終端基帶芯片平臺(tái)。

2021-04-19 08:07:18

您好!我在看論壇下載的K2_STK_DSP_v1.1.zip中的SRIO部分的代碼,其中 SRIO_Interrupts.c中的函數(shù) interrupt void SRIO

2018-08-03 06:27:02

本帖最后由 一只耳朵怪 于 2018-6-19 15:13 編輯

最近發(fā)現(xiàn)論壇上好多SRIO的帖子,剛好應(yīng)客戶需求我總結(jié)了一些SRIO的東西,在這里也分享出來(lái),作為拋磚引玉吧。首先坦白來(lái)說(shuō)我

2018-06-19 04:30:00

本帖最后由 一只耳朵怪 于 2018-6-19 15:39 編輯

因?yàn)轫?xiàng)目需求,一片C6670需要連接到兩片F(xiàn)PGA,但是又覺得沒(méi)必要使用SRIO SWITCH。所以我的問(wèn)題是:C6670

2018-06-19 00:53:24

?SRIO_2DSP_Test()中的Keystone_SRIO_match_ACK_ID()是用來(lái)檢測(cè)相應(yīng)port的鏈路是否建立成功,函數(shù)參數(shù)DSP1_SRIO

2018-06-19 00:53:06

你好我對(duì)DSP和SRIO之間的通信感興趣。有人知道virtex-6 FPGA是否有srio引腳,以及如何配置?

2020-06-14 14:22:51

本帖最后由 一只耳朵怪 于 2018-6-19 15:35 編輯

不管用CCS 提供的PDK例子,還是論壇上提供的SRIO例子,得出的結(jié)果相同:SRIO external loopback

2018-06-19 06:26:42

本帖最后由 一只耳朵怪 于 2018-6-20 11:00 編輯

在K1_STK_v1.1開發(fā)包的srio工程內(nèi)函數(shù)SRIO_PktDM_init內(nèi)對(duì)srio內(nèi)的PKTDMA

2018-06-20 05:21:38

本帖最后由 一只耳朵怪 于 2018-6-19 10:45 編輯

我用的硬件是TMDSEVM6678LE評(píng)估版,CCS5.2,pdk_C6678_1_1_2_5。我想將測(cè)試SRIO內(nèi)環(huán)的工程

2018-06-19 04:22:50

Hi,Ti guys,我在使用自己板上的c6678,利用論壇上keystone_srio程序調(diào)試dsp和fpga端的通信。同事從fpga(v6,srio核)看來(lái)收發(fā)地址都是34衛(wèi)的,但我調(diào)DSP互聯(lián)

2018-12-28 11:08:14

可編程基帶濾波器用于軟件定義的 UHF RFID 閱讀器

2019-08-01 12:35:31

基于TMS320C6455的高速SRIO接口設(shè)計(jì)

引 言

數(shù)字信號(hào)處理技術(shù)已廣泛應(yīng)用于通信、雷達(dá)、聲納、遙感、圖形圖像處理和語(yǔ)音處理等領(lǐng)

2010-02-24 16:58:35 1641

1641

基帶傳輸,基帶傳輸是什么意思

數(shù)字信號(hào)可以直接采用基帶傳輸,所謂基帶就是指基本頻帶。基帶傳輸就是在線路中直接傳送數(shù)字信號(hào)的電脈沖,這是

2010-03-18 14:36:00 10901

10901 基帶網(wǎng) | ~窄帶網(wǎng)),基帶網(wǎng)(窄帶網(wǎng))是什么意思

網(wǎng)絡(luò)從信息傳輸帶寬或傳輸介質(zhì)來(lái)分:基帶網(wǎng)、寬帶網(wǎng)。

2010-03-20 13:58:19 1300

1300 基帶網(wǎng)絡(luò),基帶網(wǎng)絡(luò)是什么意思

計(jì)算機(jī)網(wǎng)絡(luò)按照信號(hào)頻帶占用的方式可分為基帶網(wǎng)和寬帶網(wǎng)。

未經(jīng)調(diào)制的原

2010-03-20 14:02:21 3798

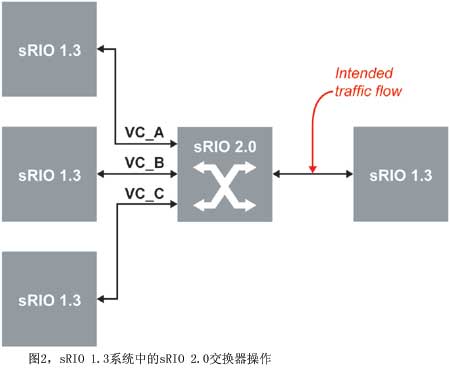

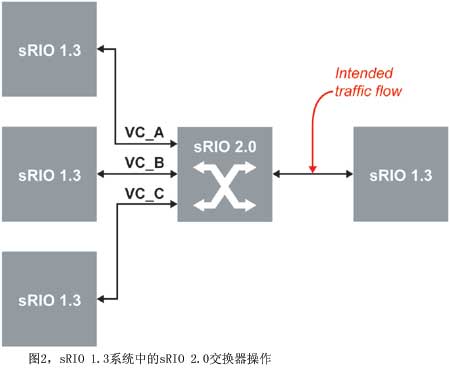

3798 sRIO 2.0中虛擬通道的優(yōu)勢(shì)和加速其采用的技術(shù)

Serial RapidIO(sRIO)是一種高性能、基于包的技術(shù),可以用于越來(lái)越多的應(yīng)用,包括無(wú)線基礎(chǔ)設(shè)施、存儲(chǔ)、醫(yī)學(xué)

2010-01-12 10:20:26 1525

1525

CEVA公司宣布,中國(guó)合肥東芯通信股份有限公司(Xincomm Communications,簡(jiǎn)稱東芯通信)已獲授權(quán)使用CEVA-X DSP內(nèi)核用于其下一代TDD/FDD-LTE UE基帶SoC產(chǎn)品設(shè)計(jì)

2011-03-25 09:20:45 795

795 本文介紹了這種基于SRIO互聯(lián)技術(shù)的高速實(shí)時(shí)數(shù)據(jù)處理硬件平臺(tái),并在該平臺(tái)上研究了多DSP之間、DSP與FPGA之間的SRIO通信技術(shù)。

2012-01-10 15:07:55 3561

3561

本內(nèi)容介紹了手機(jī)基帶相關(guān)內(nèi)容,手機(jī)基帶是什么,手機(jī)基帶版本等

2012-05-24 14:48:32 5527

5527 電路功能與優(yōu)勢(shì) 該電路是靈活的頻率捷變中頻至基帶接收機(jī)。中頻和基帶上的可變?cè)鲆?b class="flag-6" style="color: red">用于調(diào)整信號(hào)電平。 ADRF6510 基帶ADC驅(qū)動(dòng)器還包括可編程低通濾波器,可消除通道外阻塞和噪聲。 此濾波器的帶寬

2017-11-24 10:48:14 561

561

為了滿足2ynq-7000系列芯片的SRIO數(shù)據(jù)傳輸要求,提出了一種基于FPGA控制DMA傳輸進(jìn)行SRIO通信的設(shè)計(jì)方案,并完成了ARM與FPGA核間高吞吐率的數(shù)據(jù)交互操作。系統(tǒng)的FPGA部分主要

2017-12-21 11:37:03 30

30 本文件描述串行RapidIO?(srio)the on the tms320c6474外圍設(shè)備。

2018-04-16 16:49:07 10

10 SRIO是面向嵌入式系統(tǒng)開發(fā)提出的高可靠、高性能、基于包交換的新一代高速互聯(lián)技術(shù),已于2004年被國(guó)際標(biāo)準(zhǔn)化組織(ISO)和國(guó)際電工協(xié)會(huì)(IEC)批準(zhǔn)為ISO/IECDIS 18372標(biāo)準(zhǔn)。SRIO則是面向串行背板、DSP和相關(guān)串行數(shù)據(jù)平面連接應(yīng)用的串行RapidIO接口。

2020-06-17 11:48:12 2555

2555 本文為您分享基于C66x+FPGA的SRIO開發(fā)視頻教程,適用于創(chuàng)龍TMS320C6678、TMS320C665x、Kintex-7、Artix-7平臺(tái)。

2020-07-01 10:47:39 1760

1760 CN0320:基于IQ解調(diào)器,具有中頻和基帶可變?cè)鲆嬉约翱删幊?b class="flag-6" style="color: red">基帶濾波功能的中頻至基帶接收機(jī)

2021-03-18 23:25:41 0

0 對(duì)SRIO網(wǎng)絡(luò)中的節(jié)點(diǎn)進(jìn)行枚舉并建立網(wǎng)絡(luò)拓?fù)湫畔ⅲ月酚商鴶?shù)定義路由的成本,根據(jù)改進(jìn) Floyd- Marshal算法計(jì)算并保存交換節(jié)點(diǎn)間的K最短路徑。給岀預(yù)期負(fù)載的概念和鏈路上的路由路徑數(shù)量來(lái)定義鏈路的負(fù)載,采用負(fù)載均衡算法從K最短路徑中進(jìn)行選路,建

2021-05-11 14:47:51 9

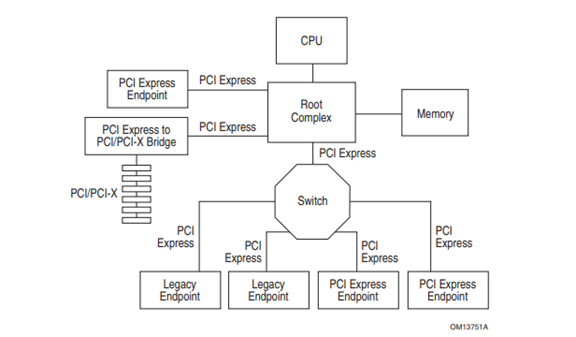

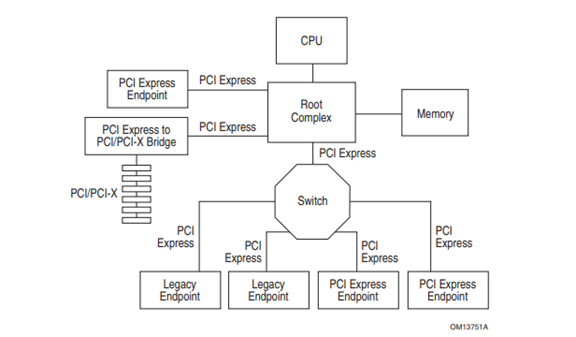

9 隨著PCIe接口、以太網(wǎng)接口的飛速發(fā)展,以及SOC芯片的層出不窮,芯片間的數(shù)據(jù)交互帶寬大大提升并且正在向片內(nèi)交互轉(zhuǎn)變;SRIO接口的應(yīng)用市場(chǎng)在縮小,但是由于DSP和PowerPC中集成了SRIO接口,因此在使用DSP/Power PC + FPGA的使用場(chǎng)景中仍然占有一席之地。

2022-08-02 10:00:26 3111

3111

基帶單元 (BBU) 是電信網(wǎng)絡(luò)中處理基帶信號(hào)的設(shè)備。BBU 充當(dāng)基站的集中“樞紐”,處理上行鏈路和下行鏈路數(shù)據(jù)流量,并通過(guò)光纖控制 RRU(遠(yuǎn)程無(wú)線電單元)功能。

2022-09-01 18:13:48 10683

10683 目前具備SRIO接口的硬件不多,推薦廣州星嵌電子科技有限公司開發(fā)的DSP+FPGA+RAM開發(fā)板XQ6657Z35-EVM。

2022-11-08 17:22:21 742

742

使用于STM32(符合IEC 61508標(biāo)準(zhǔn))的X-CUBE-STL功能安全包適應(yīng)其他安全標(biāo)準(zhǔn)

2022-11-21 17:06:43 2

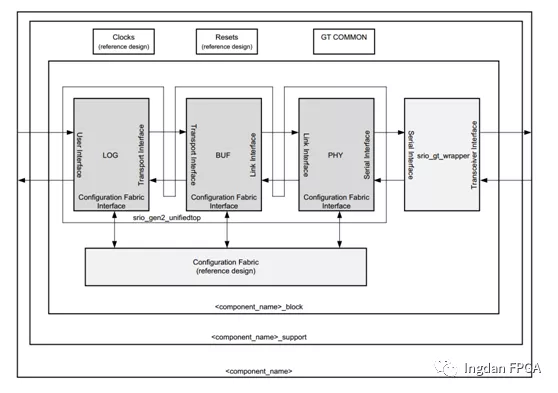

2 數(shù)據(jù)從遠(yuǎn)程設(shè)備(假設(shè)為DSP的SRIO端)傳輸過(guò)來(lái),F(xiàn)PGA端(假設(shè)我們這端為FPGA的SRIO端口)通過(guò)RX接收到串行數(shù)據(jù),先到達(dá)物理層進(jìn)行時(shí)鐘恢復(fù),串并轉(zhuǎn)換,之后進(jìn)行8b/10b解碼操作、CRC校驗(yàn),這一系列的操作都在物理層完成,之后進(jìn)入傳輸層

2023-03-03 10:19:53 725

725 摘要: 現(xiàn)代 信號(hào) 處理系統(tǒng)通常需要在不同處理器之間實(shí)現(xiàn)高速數(shù)據(jù) 通信 ,SRIO協(xié)議由于高效率、低延時(shí)的特性被廣泛使用。本文研究了在 FPGA 和 DSP 兩種處理器之間實(shí)現(xiàn)SRIO協(xié)議的方法

2023-03-20 15:00:01 1324

1324 SRIO這種高速串口復(fù)雜就復(fù)雜在它的協(xié)議上,三層協(xié)議:邏輯層,傳輸層以及物理層。

數(shù)據(jù)手冊(cè)會(huì)說(shuō)這三層協(xié)議是干什么的呢?也就是分工(【FPGA】SRIO IP核系統(tǒng)總覽以及端口介紹(一)(User Interfaces 之 I/O Port))

2023-04-25 11:20:55 1176

1176

本文介紹一個(gè)FPGA常用模塊:SRIO(Serial RapidIO)。SRIO協(xié)議是一種高速串行通信協(xié)議,在我參與的項(xiàng)目中主要是用于FPGA和DSP之間的高速通信。有關(guān)SRIO協(xié)議的詳細(xì)介紹網(wǎng)上有很多,本文主要簡(jiǎn)單介紹一下SRIO IP核的使用和本工程的源代碼結(jié)構(gòu)。

2023-09-04 18:19:18 683

683

電子發(fā)燒友網(wǎng)站提供《奈奎斯特準(zhǔn)則如何運(yùn)用于基帶采樣、欠采樣和過(guò)采樣應(yīng)用.pdf》資料免費(fèi)下載

2023-11-28 09:25:33 0

0 在于定義、功能的不同。射頻芯片是指用于實(shí)現(xiàn)無(wú)線通訊收發(fā)功能的芯片。它可以將模擬信號(hào)轉(zhuǎn)換成數(shù)字信號(hào),并進(jìn)行調(diào)制、解調(diào)等操作,在無(wú)線通訊中發(fā)揮著非常重要的作用。基帶芯片是指完成基礎(chǔ)處理功能的芯片,比如數(shù)字信號(hào)處理、調(diào)制解調(diào)等功能,但不包含射頻信號(hào)的處理。

2024-01-06 16:16:17 1506

1506

SRIO(Serial RapidIO)交換芯片是一種高性能的通信芯片,專門設(shè)計(jì)用于實(shí)現(xiàn)基于SRIO協(xié)議的數(shù)據(jù)交換和傳輸。SRIO是一種點(diǎn)對(duì)點(diǎn)串行通信協(xié)議,廣泛應(yīng)用于嵌入式系統(tǒng)、高性能計(jì)算、網(wǎng)絡(luò)通信

2024-03-16 16:40:42 1567

1567 SRIO(Serial RapidIO)交換芯片是一種基于RapidIO(快速輸入輸出)技術(shù)的高速網(wǎng)絡(luò)通信芯片。RapidIO是一種高性能、低延遲的網(wǎng)絡(luò)通信標(biāo)準(zhǔn),專為嵌入式系統(tǒng)設(shè)計(jì),廣泛應(yīng)用于通信基礎(chǔ)設(shè)施、軍事和航空、工業(yè)自動(dòng)化以及汽車等領(lǐng)域。

2024-03-21 16:30:37 72

72 SRIO交換芯片屬于高速網(wǎng)絡(luò)通信芯片的一種,具體來(lái)說(shuō),它們是基于RapidIO(快速輸入輸出)技術(shù)的串行通信芯片。RapidIO是一種用于高性能嵌入式系統(tǒng)的互連技術(shù),它支持多種通信協(xié)議和拓?fù)浣Y(jié)構(gòu),適用于需要高速、低延遲通信的應(yīng)用場(chǎng)景。

2024-03-21 16:33:20 98

98

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論