SystemC是基于C++的

系統(tǒng)級(jí)設(shè)計(jì)語(yǔ)言,兼具描述硬件電路模型和面向?qū)ο蟮某橄竽芰Α?/div>

2023-08-07 09:43:45 550

550

在 SystemVerilog 中,聯(lián)合只是信號(hào),可通過(guò)不同名稱和縱橫比來(lái)加以引用。

2023-10-08 15:45:14 593

593

使用默認(rèn)應(yīng)用程序模擬后,您可以:

·通過(guò)修改參考平臺(tái)測(cè)試臺(tái)和相應(yīng)的構(gòu)建系統(tǒng)對(duì)其進(jìn)行更改,以包括、實(shí)例化和連接新的或更新的模型。

·復(fù)制和移植作為參考平臺(tái)一部分的SystemC周期模型,并將其構(gòu)建到您自己的定制平臺(tái)中。

·修改ARM參考平臺(tái),方法是將您自己的SystemC模型類添加到參考平臺(tái)

2023-08-23 07:21:54

查看本節(jié)中使用ARM SystemC周期模型的前提條件。

有關(guān)以下必備條件的詳細(xì)信息,請(qǐng)參閱周期模型系統(tǒng)C運(yùn)行時(shí)安裝指南(101146):

·您的環(huán)境中必須安裝受支持的周期模型SystemC

2023-08-12 06:21:42

SystemC是什么?SystmeC的作用是什么?SystemC的用途是什么?

2021-06-21 07:37:41

SystemC是什么?SystmeC的作用是什么?

2021-06-21 08:05:06

SystemVerilog 的VMM 驗(yàn)證方法學(xué)教程教材包含大量經(jīng)典的VMM源代碼,可以實(shí)際操作練習(xí)的例子,更是ic從業(yè)人員的絕佳學(xué)習(xí)資料。SystemVerilog 的VMM 驗(yàn)證方法學(xué)教程教材[hide][/hide]

2012-01-11 11:21:38

本帖最后由 鼻子抽筋 于 2012-2-21 15:41 編輯

SystemVerilog給予Verilog、VHDL和C/C++優(yōu)點(diǎn)為一身的硬件描述語(yǔ)言,很值得學(xué)一學(xué)。1、8-bit up

2012-02-21 15:39:27

SystemVerilog有哪些標(biāo)準(zhǔn)?

2021-06-21 08:09:41

官方的一個(gè)systemverilog詳解,很詳細(xì)。推薦給打算往IC方面發(fā)展的朋友。QQ群374590107歡迎有志于FPGA開(kāi)發(fā),IC設(shè)計(jì)的朋友加入一起交流。一起為中國(guó)的IC加油!!!

2014-06-02 09:47:23

官方的一個(gè)systemverilog詳解,很詳細(xì)。推薦給打算往IC方面發(fā)展的朋友。

2014-06-02 09:30:16

systemverilog的一些基本語(yǔ)法以及和verilog語(yǔ)言之間的區(qū)別。

2015-04-01 14:24:14

),沒(méi)有任何圍欄。為了實(shí)現(xiàn)這一點(diǎn),需要采用協(xié)作式機(jī)器人網(wǎng)絡(luò)物理系統(tǒng)(CPS)實(shí)施額外的安全和保護(hù)措施,這要求基于人與機(jī)器人之間的交互程度,確保安全性,并提高生產(chǎn)率。實(shí)際上,協(xié)作機(jī)器人網(wǎng)絡(luò)物理系統(tǒng)的設(shè)計(jì)方法

2020-12-01 14:24:33

本節(jié)介紹ARM Cortex?-A53系統(tǒng)C周期模型。

ARM系統(tǒng)C周期模型直接從RTL代碼編譯而來(lái)。

SystemC模型包裝器以源代碼形式提供,使您能夠?yàn)槿魏畏?b class="flag-6" style="color: red">SystemC IEEE 1666

2023-08-16 07:30:34

本節(jié)介紹ARM Cortex?-R52系統(tǒng)C周期模型。

ARM系統(tǒng)C周期模型直接從RTL代碼編譯而來(lái)。

SystemC模型包裝器以源代碼形式提供,使您能夠?yàn)槿魏畏?b class="flag-6" style="color: red">SystemC IEEE 1666

2023-08-18 07:25:43

本節(jié)介紹ARM Cortex?-R8系統(tǒng)C周期模型。

ARM系統(tǒng)C周期模型直接從RTL代碼編譯而來(lái)。

SystemC模型包裝器以源代碼形式提供,使您能夠?yàn)槿魏畏?b class="flag-6" style="color: red">SystemC IEEE 1666

2023-08-16 06:47:09

的下一代協(xié)作平臺(tái) Jazz 平臺(tái)上的一個(gè)商用產(chǎn)品、一個(gè)協(xié)作式的軟件開(kāi)發(fā)環(huán)境,它包含了集成的源代碼控制、工作項(xiàng)管理和構(gòu)建管理等功能。RTC是一個(gè)可實(shí)時(shí)相互協(xié)作的軟件交付環(huán)境,可以幫助跨地域分布的開(kāi)發(fā)團(tuán)隊(duì)簡(jiǎn)化

2021-07-09 14:37:11

1.Verilog 中g(shù)enerate if語(yǔ)句如何用systemc實(shí)現(xiàn)?例如:generateif (SIZE < 8)assign y = a & b & c;else

2014-08-29 16:11:21

Verilog 中g(shù)enerate if語(yǔ)句如何用systemc實(shí)現(xiàn)?例如:generateif (SIZE < 8)assign y = a & b & c;else

2014-08-28 12:06:43

學(xué)快速發(fā)展,這些趨勢(shì)你了解嗎?SystemVerilog + VM是目前的主流,在未來(lái)也將被大量采用,這些語(yǔ)言和方法學(xué),你熟練掌握了嗎?對(duì)SoC芯片設(shè)計(jì)驗(yàn)證感興趣的朋友,可以關(guān)注啟芯工作室推出的SoC芯片

2013-06-10 09:25:55

大家好,我對(duì)一個(gè) round robin 的 systemverilog 代碼有疑惑。https://www.edaplayground.com/x/2TzD代碼第49和54行是怎么解析呢 ?

2017-03-14 19:16:04

在實(shí)際應(yīng)用中,搶中式的多任務(wù)某種程序上帶來(lái)了用戶程序設(shè)計(jì)時(shí)數(shù)據(jù)保護(hù)的困難,并且,具備搶占功能的多任務(wù)內(nèi)核設(shè)計(jì)時(shí)困難也比較多,這會(huì)增加操作系統(tǒng)自身的代碼,也使它在小資源單片機(jī)系統(tǒng)中應(yīng)用較少;而協(xié)作

2012-12-07 15:55:28

無(wú)線傳感器網(wǎng)絡(luò)是目前國(guó)內(nèi)外研究的熱點(diǎn)之一,它是由大量廉價(jià)的傳感器節(jié)點(diǎn)組成,通過(guò)有線/無(wú)線通信方式自組織形成的網(wǎng)絡(luò)系統(tǒng),相互協(xié)作地感知周圍的數(shù)據(jù)。

2019-10-17 08:03:26

在某大型科技公司的招聘網(wǎng)站上看到招聘邏輯硬件工程師需要掌握SystemVerilog語(yǔ)言,感覺(jué)SystemVerilog語(yǔ)言是用于ASIC驗(yàn)證的,那么做FPGA工程師有沒(méi)有必要掌握SystemVerilog語(yǔ)言呢?

2017-08-02 20:30:21

在verilog中實(shí)現(xiàn)上拉和下拉很容易,使用pullup 和 pulldown 就行,但在systemC設(shè)計(jì)中如何實(shí)現(xiàn)上拉和下拉?

2015-07-22 22:37:20

應(yīng)急現(xiàn)場(chǎng)可視化協(xié)作系統(tǒng)基于各種先進(jìn)的技術(shù),面向城市應(yīng)急現(xiàn)場(chǎng)處理和協(xié)作問(wèn)題,提供可靠、快速、完整的城市應(yīng)急現(xiàn)場(chǎng)可視化協(xié)作系統(tǒng)方案,為應(yīng)急事件實(shí)時(shí)上報(bào)、應(yīng)急事件快速響應(yīng)、應(yīng)急事件遠(yuǎn)程指揮和調(diào)度、應(yīng)急

2013-07-26 14:41:51

應(yīng)急現(xiàn)場(chǎng)可視化協(xié)作系統(tǒng)基于各種先進(jìn)的技術(shù),面向城市應(yīng)急現(xiàn)場(chǎng)處理和協(xié)作問(wèn)題,提供可靠、快速、完整的城市應(yīng)急現(xiàn)場(chǎng)可視化協(xié)作系統(tǒng)方案,為應(yīng)急事件實(shí)時(shí)上報(bào)、應(yīng)急事件快速響應(yīng)、應(yīng)急事件遠(yuǎn)程指揮和調(diào)度、應(yīng)急

2013-07-26 18:10:02

來(lái)源:互聯(lián)網(wǎng)隨著物聯(lián)網(wǎng)不斷的發(fā)展的趨于成熟期,我們同時(shí)也收集了更多的信息數(shù)據(jù),其實(shí)就是所謂的大數(shù)據(jù)。換個(gè)說(shuō)法,也就是說(shuō)物聯(lián)網(wǎng)和大數(shù)據(jù)可以互相協(xié)作。據(jù)統(tǒng)計(jì)《福布斯》預(yù)測(cè),到2025年,生成的數(shù)據(jù)量將增加到175 ZB。這將對(duì)收集、分析和報(bào)告數(shù)據(jù)的方式產(chǎn)生巨大的影響。

2020-10-22 06:01:50

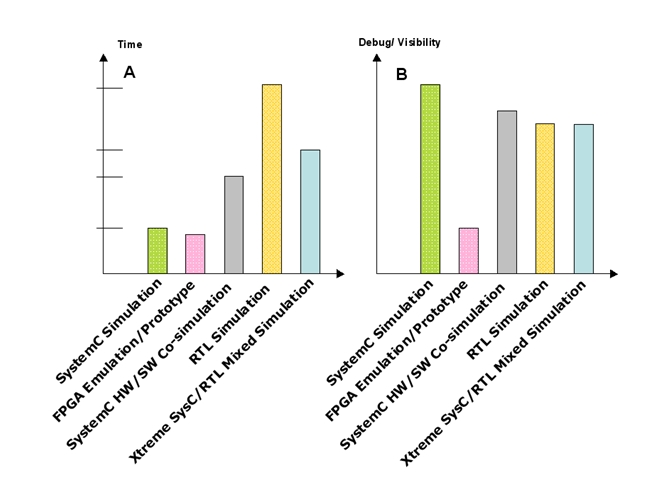

如何在ModelSim下編譯和仿真SystemC的設(shè)計(jì)?如何在ModelSim下用SystemC的做驗(yàn)證?SystemC作為一種系統(tǒng)級(jí)設(shè)計(jì)與驗(yàn)證語(yǔ)言,非常適合做復(fù)雜IC的驗(yàn)證,而不是用于RTL描述

2012-03-01 11:30:19

請(qǐng)教各位大佬,UVM是基于sv的驗(yàn)證方法學(xué),如果采用systemc語(yǔ)言編程,如何實(shí)現(xiàn)?

2019-11-07 15:30:16

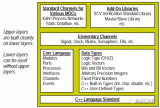

的基礎(chǔ)。 1800 SystemVerilog 標(biāo)準(zhǔn),造福于整個(gè)驗(yàn)證社區(qū),包括半導(dǎo)體、系統(tǒng)、IP和 EDA 行業(yè)的公司以及驗(yàn)證服務(wù)。 SystemC (***0, Accellera/IEEE) SystemC

2022-02-16 13:36:53

導(dǎo)入SystemVerilog程序包意味著什么?

2020-12-11 06:53:29

怎么在Modelsim下編譯SystemC ,例如使用命令sccom -link

2019-02-28 21:46:01

2打兩拍systemverilog與VHDL編碼1 本章目錄1)FPGA簡(jiǎn)介2)SystemVerilog簡(jiǎn)介3)VHDL簡(jiǎn)介4)打兩拍verilog編碼5)打兩拍VHDL編碼6)結(jié)束語(yǔ)2 FPGA

2021-07-26 06:19:28

decided

to write this book after learning SystemC and after using minimal documents

to help us through the quest of bec

2009-02-12 09:30:34 0

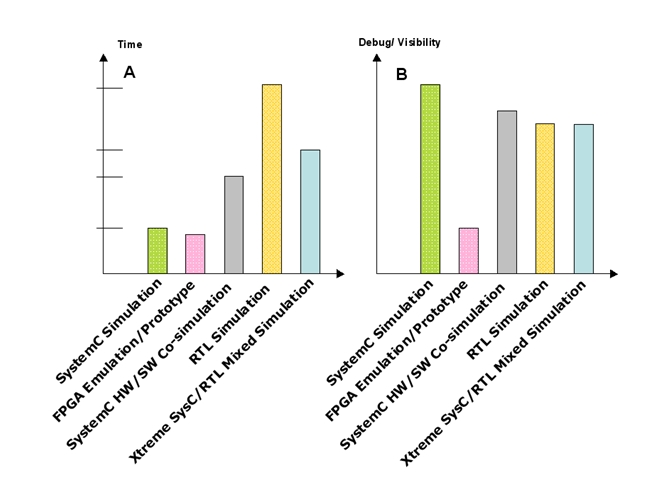

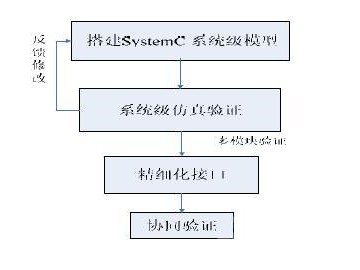

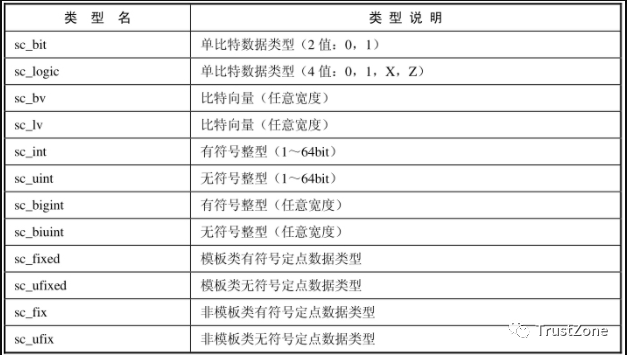

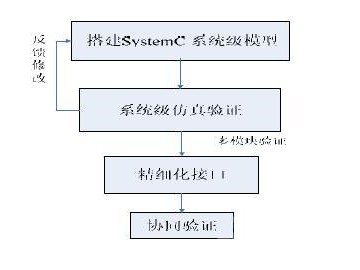

0 IC 技術(shù)已發(fā)展到SoC 階段,系統(tǒng)級(jí)設(shè)計(jì)、仿真和驗(yàn)證已成為IC 設(shè)計(jì)面臨的巨大挑戰(zhàn)。SystemC 是新興的系統(tǒng)級(jí)設(shè)計(jì)語(yǔ)言,為復(fù)雜系統(tǒng)的設(shè)計(jì)與驗(yàn)證提供了解決方案。本文介紹SystemC 的特點(diǎn)

2009-05-18 13:44:58 28

28 Systemc From The Ground Up:The first question any reader should ask is “Why this book?” We

2009-07-10 17:27:57 0

0 SystemVerilog Assertion Handbook1 ROLE OF SYSTEMVERILOG ASSERTIONSIN A VERIFICATION METHODOLOGY

2009-07-22 14:08:48 188

188 SystemVerilog Assertion Handbook1 ROLE OF SYSTEMVERILOG ASSERTIONSIN A VERIFICATION METHODOLOGY

2009-07-22 14:12:50 20

20 事務(wù)級(jí)(Transaction-Level,TL)建模是SystemC 中提出的一種新型高層次建模方法,以CoCentric System Studio(CCSS)作為SystemC 仿真工具,以一個(gè)IP 路由系統(tǒng)為建模實(shí)例,分析了事務(wù)級(jí)建模

2009-07-30 15:27:27 24

24 本文利用形式化的方法對(duì)SystemVerilog的指稱語(yǔ)義進(jìn)行研究,采用EBES(extendedbundle event structure)作為抽象模型,以便更好的描述SystemVerilog真并發(fā)的特點(diǎn)。我們的主要工作是:首先,

2009-12-22 14:01:07 12

12 如何采用SystemVerilog 來(lái)改善基于FPGA 的ASIC 原型關(guān)鍵詞:FPGA, ASIC, SystemVerilog摘要:ASIC 在解決高性能復(fù)雜設(shè)計(jì)概念方面提供了一種解決方案,但是ASIC 也是高投資風(fēng)險(xiǎn)的,如90nm ASIC/S

2010-02-08 09:53:33 10

10 視頻編解碼芯片中運(yùn)動(dòng)估計(jì)與補(bǔ)償單元(MECU)的算法復(fù)雜,使用傳統(tǒng)硬件描述語(yǔ)言建立模型和模型驗(yàn)證的過(guò)程繁瑣耗時(shí),為了縮短芯片驗(yàn)證時(shí)間,本文針對(duì)MECU模塊提出了基于SystemC語(yǔ)言

2010-02-24 12:07:21 16

16 論文提出了一種模塊化的高效電子商務(wù)推薦系統(tǒng)的體系結(jié)構(gòu),詳述了該系統(tǒng)各個(gè)模塊的構(gòu)造、功能以及如何相互協(xié)作從而最終完成推薦任務(wù)。并著重研究了數(shù)據(jù)預(yù)處理和序列模式挖

2010-03-02 11:59:09 19

19 利用基于SystemC/TLM的方法學(xué)進(jìn)行IP開(kāi)發(fā)和FPGA建模

隨著系統(tǒng)級(jí)芯片技術(shù)的出現(xiàn),設(shè)計(jì)規(guī)模正變得越來(lái)越大,因而變得非常復(fù)雜,同時(shí)上市時(shí)間也變得更加苛刻。通常RTL已

2010-01-04 13:11:50 5154

5154

污水處理智能化系統(tǒng)的Multi-Agent通信技術(shù)與實(shí)現(xiàn)

分布式人工智能(Distributed Artificial Intelligence,DAI)理論主要研究在邏輯上或物理上分散的智能系統(tǒng)如何并行地、相互協(xié)作

2010-03-12 11:35:42 758

758

就 SystemC 和 SystemVerilog 這兩種語(yǔ)言而言, SystemC 是C++在硬件支持方面的擴(kuò)展,而 SystemVerilog 則繼承了 Verilog,并對(duì) Verilog 在面向?qū)ο蠛万?yàn)證能力方面進(jìn)行了擴(kuò)展。這兩種語(yǔ)言均支持

2010-08-16 10:52:48 5140

5140 SystemVerilog 是過(guò)去10年來(lái)多方面技術(shù)發(fā)展和實(shí)際試驗(yàn)的結(jié)晶,包括硬件描述語(yǔ)言(HDL)、硬件驗(yàn)證語(yǔ)言(HVL)、SystemC、Superlog和屬性規(guī)范語(yǔ)言。它們都從技術(shù)和市場(chǎng)的成敗中得到了豐富的經(jīng)

2010-09-07 09:55:16 1118

1118 文章主要介紹《VMM for SystemVerilog》一書(shū)描述的如何利用SystemVerilog語(yǔ)言,采用驗(yàn)證方法學(xué)以及驗(yàn)證庫(kù)開(kāi)發(fā)出先進(jìn)驗(yàn)證環(huán)境。文章分為四部分,第一部分概述了用SystemVerilog語(yǔ)言驗(yàn)證復(fù)雜S

2011-05-09 15:22:02 52

52 本內(nèi)容提供了SystemC片上系統(tǒng)設(shè)計(jì)及源代碼 #include scv.h #include fifo_mutex.h class rw_task_if : virtual public

2011-05-10 15:32:40 101

101 為了研究前庭系統(tǒng)不同器官的運(yùn)動(dòng)以及它們之間相互協(xié)作的基本原理的需求,設(shè)計(jì)了一種基于前庭系統(tǒng)功能的頭眼運(yùn)動(dòng)系統(tǒng)層次消息總線(HMB)的體系結(jié)構(gòu)模型,并完成了該模型結(jié)構(gòu)的

2012-12-17 10:51:55 31

31 為了實(shí)現(xiàn)軟硬件協(xié)同設(shè)計(jì)和提高仿真速度的需求,采用SystemC語(yǔ)言的建模方法,通過(guò)對(duì)片上網(wǎng)絡(luò)體系結(jié)構(gòu)的研究,提出了一種片上網(wǎng)絡(luò)的建模方案,并對(duì)一個(gè)mesh結(jié)構(gòu)完成了SystemC的建模設(shè)

2013-07-30 11:46:44 42

42 systemc語(yǔ)言簡(jiǎn)單介紹,有助于初學(xué)者更好的運(yùn)用和了解

2015-12-07 10:33:57 0

0 基于SystemC構(gòu)建多核DSP軟件仿真平臺(tái)_韋祎

2017-01-03 17:41:32 3

3 據(jù)悉,OpenAI開(kāi)發(fā)了出了一套名為“OpenAI Five”的算法,雖然單獨(dú)來(lái)看這種算法并沒(méi)有什么突破,只是針對(duì)玩Dota2的一種神經(jīng)網(wǎng)絡(luò),并且此前也曾有AI算法在1對(duì)1的Dota2比賽中戰(zhàn)勝人類玩家,但是,本次AI的勝利重要意義在于5套算法之間學(xué)會(huì)了與隊(duì)友相互協(xié)作。

2018-06-27 05:29:00 499

499 針對(duì)無(wú)線傳感器網(wǎng)絡(luò)(WSN)中基于數(shù)字簽名的公鑰加密體制的廣播認(rèn)證需要耗費(fèi)大量的能量,以及傳感器節(jié)點(diǎn)資源有限的問(wèn)題,為了減少傳感器節(jié)點(diǎn)的能量耗費(fèi)和加快傳感器節(jié)點(diǎn)的認(rèn)證,提出一種傳感器節(jié)點(diǎn)相互協(xié)作

2017-12-14 10:07:56 0

0 為了提高視頻多播傳輸?shù)目煽啃裕治隽烁采w區(qū)域發(fā)生重疊的訪問(wèn)點(diǎn)間相互協(xié)作對(duì)于提高系統(tǒng)增益和系統(tǒng)公平性的作用,提出一種基于網(wǎng)絡(luò)編碼和多訪問(wèn)點(diǎn)協(xié)作的視頻多播方案。該方案首先將每個(gè)視頻劃分為大小相同的報(bào)文

2018-01-16 14:35:05 1

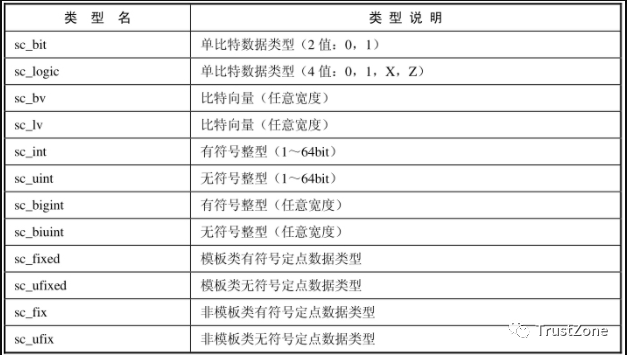

1 SystemC 是由C++衍生而來(lái),本質(zhì)是在C++的基礎(chǔ)上添加了硬件擴(kuò)展庫(kù)和仿真核,這使SystemC 可以在不同抽象級(jí)對(duì)復(fù)雜電子系統(tǒng)建模。

2018-07-19 11:55:00 4708

4708

電器與電器之間的協(xié)作性。Chef Connect,包括一個(gè)廚灶,以及位于其上方的微波爐,兩者可通過(guò)藍(lán)牙技術(shù)實(shí)現(xiàn)同步功能,打造統(tǒng)一的下廚體驗(yàn)。

2019-08-04 08:16:00 2670

2670 支持SystemC的電子系統(tǒng)級(jí)(ESL)設(shè)計(jì)和驗(yàn)證環(huán)境旨在設(shè)計(jì),分析,優(yōu)化和驗(yàn)證片上系統(tǒng)(SoC)平臺(tái)模型。這樣的環(huán)境構(gòu)成了已建立的RTL實(shí)現(xiàn)流程的前端。

2019-10-03 17:05:00 4546

4546 從連接性、傳感器和網(wǎng)關(guān)到云和應(yīng)用系統(tǒng),物聯(lián)網(wǎng)架構(gòu)由相互協(xié)作的各種組件組成。盡管確保整個(gè)物聯(lián)網(wǎng)價(jià)值鏈上的數(shù)據(jù)無(wú)縫流動(dòng)是至關(guān)重要的,但這僅僅只是成功了一半。

2019-10-16 10:44:42 854

854 工業(yè)制造業(yè)擺脫了手工制作,向機(jī)械化發(fā)展,目前我國(guó)工業(yè)制造業(yè)其實(shí)更多聚集在工業(yè)3.0時(shí)代,甚至有的還處于工業(yè)2.0時(shí)代,離工業(yè)4.0還很遠(yuǎn)。生產(chǎn)出來(lái)的產(chǎn)品質(zhì)量無(wú)法與先進(jìn)水平國(guó)家的產(chǎn)品相提并論,在世界上至今沒(méi)有定價(jià)權(quán),令我國(guó)處于被動(dòng)狀態(tài)。要想扭轉(zhuǎn)此局面,就不得不改造工業(yè)制造,實(shí)現(xiàn)標(biāo)準(zhǔn)化,就需要向網(wǎng)絡(luò)化、數(shù)字化、智能化轉(zhuǎn)型發(fā)展。看智能制造技術(shù)如何賦能生產(chǎn)線?

2019-11-25 15:39:43 3286

3286 疫情正在全球蔓延,但在輿論場(chǎng),相互指責(zé)的多,相互協(xié)作的少。尤其是以國(guó)為界,國(guó)籍歧視、種族歧視事件數(shù)量快速增加。

2020-03-08 16:27:00 1539

1539

PLC系統(tǒng)是一個(gè)復(fù)雜的控制系統(tǒng),它需要硬件和軟件相互協(xié)作才能才能完成我們“教”給它的任務(wù),這樣說(shuō)來(lái)它還真有點(diǎn)類似計(jì)算機(jī)的味道。

2020-10-02 18:11:00 4782

4782

手冊(cè)的這一部分探討了使用SystemVerilog進(jìn)行驗(yàn)證,然后查看了使用SystemVerilog的優(yōu)點(diǎn)和缺點(diǎn)。

2021-03-29 10:32:46 23

23 脈沖神經(jīng)膜系統(tǒng)是受到神經(jīng)生物系統(tǒng)中神經(jīng)元相互協(xié)作處理脈沖過(guò)程的啟發(fā)而提岀的一種新的計(jì)算模型。為了更進(jìn)步反映生物系統(tǒng)隨機(jī)性的特點(diǎn),文中首先提岀一種新脈沖神經(jīng)系統(tǒng)——粗糙規(guī)則脈沖神經(jīng)膜系統(tǒng),用上下近似

2021-06-15 15:35:58 4

4 、數(shù)據(jù)采集系統(tǒng)、數(shù)據(jù)處理與傳輸系統(tǒng)、在線監(jiān)測(cè)系統(tǒng)及遠(yuǎn)程數(shù)據(jù)管理中心等部分組成,這些系統(tǒng)各自工作又相互協(xié)作,完成整個(gè)系統(tǒng)的自動(dòng)在線監(jiān)測(cè)。

2021-06-23 09:38:01 819

819 得SystemVerilog在一個(gè)更高的抽象層次上提高了設(shè)計(jì)建模的能力。 SystemVerilog由Accellera開(kāi)發(fā),它主要定位在芯片的實(shí)現(xiàn)和驗(yàn)證流程上,并為系統(tǒng)級(jí)的設(shè)計(jì)流程提供了強(qiáng)大的連接能力。下面我們從幾個(gè)方面對(duì)S

2021-10-11 10:35:38 2042

2042 event是SystemVerilog語(yǔ)言中的一個(gè)強(qiáng)大特性,可以支持多個(gè)并發(fā)進(jìn)程之間的同步。

2022-10-17 10:21:33 1024

1024 SystemVerilog casting意味著將一種數(shù)據(jù)類型轉(zhuǎn)換為另一種數(shù)據(jù)類型。在將一個(gè)變量賦值給另一個(gè)變量時(shí),SystemVerilog要求這兩個(gè)變量具有相同的數(shù)據(jù)類型。

2022-10-17 14:35:40 1960

1960 學(xué)習(xí)Systemverilog必備的手冊(cè),很全且介紹詳細(xì)

2022-10-19 16:04:06 2

2 SystemVerilog提供了幾個(gè)內(nèi)置方法來(lái)支持?jǐn)?shù)組搜索、排序等功能。

2022-10-31 10:10:37 1760

1760 SystemVerilog packages提供了對(duì)于許多不同數(shù)據(jù)類型的封裝,包括變量、task、function、assertion等等,以至于可以在多個(gè)module中共享。

2022-11-07 09:44:45 862

862 SystemVerilog“struct”表示相同或不同數(shù)據(jù)類型的集合。

2022-11-07 10:18:20 1852

1852 SystemVerilog中的句柄賦值和對(duì)象復(fù)制的概念是有區(qū)別的。

2022-11-21 10:32:59 523

523 系統(tǒng)級(jí)的設(shè)計(jì)流程提供了強(qiáng)大的連接能力。下面我們從幾個(gè)方面對(duì)SystemVerilog所作的增強(qiáng)進(jìn)行簡(jiǎn)要的介紹,期望能夠通過(guò)這個(gè)介

2022-12-08 10:35:05 1262

1262 SystemVerilog中Semaphore(旗語(yǔ))是一個(gè)多個(gè)進(jìn)程之間同步的機(jī)制之一,這里需要同步的原因是這多個(gè)進(jìn)程共享某些資源。

2022-12-12 09:50:58 2344

2344 上一篇文章介紹了SystemVerilog的各種隨機(jī)化方法,本文將在其基礎(chǔ)上引入SystemVerilog的隨機(jī)約束方法(constraints)。通過(guò)使用隨機(jī)約束,我們可以將隨機(jī)限制在一定的空間內(nèi),有針對(duì)性地提高功能覆蓋率。

2023-01-21 17:03:00 1519

1519 寫過(guò)Verilog和systemverilog的人肯定都用過(guò)系統(tǒng)自定義的函數(shù)$display,這是預(yù)定好的,可以直接調(diào)用的功能。

2023-05-16 09:27:02 581

581

在systemverilog中,net用于對(duì)電路中連線進(jìn)行建模,driving strength(驅(qū)動(dòng)強(qiáng)度)可以讓net變量值的建模更加精確。

2023-06-14 15:50:16 751

751

本文講一下SystemVerilog的time slot里的regions以及events的調(diào)度。SystemVerilog語(yǔ)言是根據(jù)離散事件執(zhí)行模型定義的,由events驅(qū)動(dòng)。

2023-07-12 11:20:32 775

775

制冷系統(tǒng)是指由多個(gè)組件和設(shè)備組成的整體系統(tǒng),旨在實(shí)現(xiàn)冷卻效果。制冷系統(tǒng)通常包括制冷機(jī)、冷卻劑、壓縮機(jī)、冷凝器、蒸發(fā)器和控制裝置等多個(gè)組成部分。這些部件相互協(xié)作,通過(guò)循環(huán)過(guò)程來(lái)實(shí)現(xiàn)熱量的轉(zhuǎn)移和冷卻效果的達(dá)成。

2023-08-28 15:24:52 693

693 上一篇文章《暗藏玄機(jī)的SV隨機(jī)化》介紹了SystemVerilog的各種隨機(jī)化方法,本文將在其基礎(chǔ)上引入SystemVerilog的隨機(jī)約束方法(constraints)。通過(guò)使用隨機(jī)約束,我們可以將隨機(jī)限制在一定的空間內(nèi),有針對(duì)性地提高功能覆蓋率。

2023-09-24 12:15:30 396

396 談到SystemVerilog,很多工程師都認(rèn)為SystemVerilog僅僅是一門驗(yàn)證語(yǔ)言,事實(shí)上不只如此。傳統(tǒng)的Verilog和VHDL被稱為HDL(Hardware Description

2023-10-19 11:19:19 342

342

SystemC中的模塊 模塊(SC_MODULE)是SystemC系統(tǒng)建模的一個(gè)基本單位。一個(gè)系統(tǒng)由許多個(gè)模塊構(gòu)成,各個(gè)模塊實(shí)現(xiàn)系統(tǒng)中不同的功能。在設(shè)計(jì)中,設(shè)計(jì)者需要根據(jù)功能把復(fù)雜的系統(tǒng)劃分成若干個(gè)

2023-11-02 15:31:26 227

227 SystemC中的事件 在SystemC中,事件提供了一個(gè)底層的處理程序間同步及重新啟動(dòng)的方式,它能用來(lái)實(shí)現(xiàn)通道的功能,定義事件的語(yǔ)法如下: sc_event event_name; 另外,要觸發(fā)

2023-11-02 15:44:43 299

299

SystemC TLM中的接口 在SystemC TLM中,接口是一個(gè)C++的抽象類。抽象類中的所有方法都是用“=0”標(biāo)識(shí)表示的純虛函數(shù)。C++不允許創(chuàng)建抽象類的對(duì)象,因?yàn)槌橄箢悓?duì)象是沒(méi)有意義

2023-11-02 15:54:21 270

270 本文分享一些SystemVerilog的coding guideline。

2023-11-22 09:17:30 272

272

企業(yè)由傳統(tǒng)向數(shù)字化轉(zhuǎn)型,需要打通數(shù)據(jù)孤島,把各部門數(shù)據(jù)互通相互協(xié)作辦公和統(tǒng)一數(shù)據(jù)分析做決策。

2024-01-24 10:31:04 221

221

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論