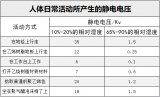

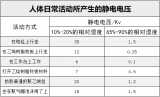

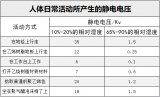

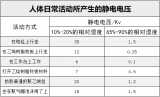

在干燥的環境下,人體靜電(ESD)的電壓很容易超過6~35Kv,當用手觸摸電子設備、PCB或PCB上的元器件時,會因為瞬間的靜電放電,而使元器件或設備受到干擾,甚至損壞設備或PCB上的元器件。

2023-05-12 09:34:01 999

999

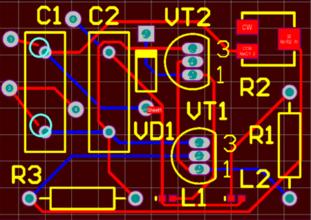

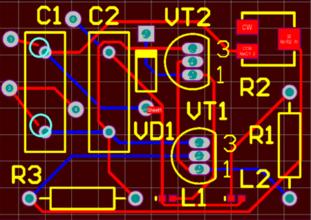

在PCB板的設計當中,可以通過分層、恰當的布局布線和安裝實現PCB的抗ESD設計。

2015-04-07 15:30:53 2009

2009

在PCB板的設計當中,可以通過分層、恰當的布局布線和安裝實現PCB的抗ESD設計。通過調整PCB布局布線,能夠很好地防范ESD.盡可能使用多層PCB,相對于雙面PCB而言,地平面和電源平面,以及排列

2016-01-20 09:59:14 3293

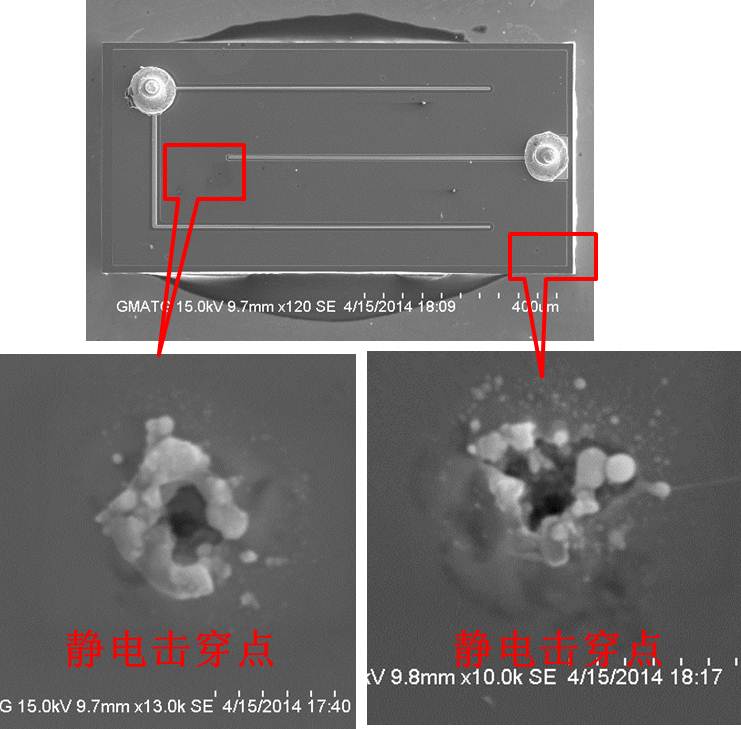

3293 ,光衰加重,甚至出現死燈現象,靜電對LED品質有非常重要的影響。LED的抗靜電指標絕不僅僅是簡單地體現它的抗靜電強度,LED的抗靜電能力與其漏電值、整體可靠性有很大關系,更是一個整體質素和可靠性的綜合體現。因為往往抗靜電高的LED,它的光特性、電特性都會

2021-11-17 12:01:33 4382

4382

從這期開始我將帶大家進入靜電放電問題的典型案例分析,通過具體的實際案例以幫助大家消化前面的知識,并通過典型案例的分析為后面靜電放電設計做鋪墊。

2023-11-29 09:17:53 347

347

這期我帶大家繼續進行靜電放電問題典型案例分析,前篇文章分別介紹了復位信號、DC-DC芯片設計問題引發的靜電放電問題;這篇文章將介紹軟件設計、PCB環路設計引發的靜電放電問題;話不多說,還是通過兩個案例展現給大家。

2023-12-11 10:03:46 489

489 或者變壓器,以及結合介質隔離和屏蔽,都可以很好的抑制靜電放電沖擊;

5)可將PCB的GND與外殼地進行單點接地,防止靜電放電電流在機箱上產生的電壓耦合進電路,但需注意接地點的選擇,選擇在電纜入口處接地

2023-05-12 12:02:17

電路設計中如何防止靜電放電? 對某些人來說 ESD 是一種挑戰,因為需要在處理和組裝未受保護的電子元件時不能造成任何損壞。 這是一種電路設計挑戰,因為需要保證系統承受住 ESD 的沖擊,之后

2023-04-07 17:07:59

排列緊密的信號線-地線間距能夠減小共模阻抗和感性耦合,使之達到雙面PCB的1/10到1/100。對于頂層和底層表面都有元器件、具有很短連接線。來自人體、環境甚至電子設備內部的靜電對于精密的半導體芯片會

2019-05-22 09:49:34

是在銅皮構成的微帶線層使用尖端相互對準的三角銅皮構成,三角銅皮一端連接在信號線,另一個三角銅皮連接地。當有靜電時會產生尖端放電進而消耗電能。 5、 采用LC濾波器的方法進行保護電路。 LC組成

2018-09-17 17:43:16

PCB設計中如何防止靜電放電我們的手都曾有過靜電放電(ESD)的體驗,即使只是從地毯上走過然后觸摸某些金屬部件也會在瞬間釋放積累起來的靜電。我們許多人都曾抱怨在實驗室中使用導電毯、ESD靜電腕帶

2013-01-29 10:38:41

緊密的信號線-地線間距能夠減小共模阻抗和感性耦合,使之達到雙面PCB的1/10到1/100.對于頂層和底層表面都有元器件、具有很短連接線。來自人體、環境甚至電子設備內部的靜電對于精密的半導體芯片會造成

2016-07-21 11:00:16

正向偏置的PN結;熔化有源器件內部的焊接線或鋁線。為了消除靜電釋放(ESD)對電子設備的干擾和破壞,需要采取多種技術手段進行防范。 在PCB板的設計當中,可以通過分層、恰當的布局布線和安裝實現PCB

2018-11-26 11:09:39

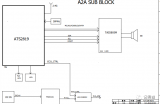

PCB上安裝光耦合器或者變壓器,以及結合介質隔離和屏蔽,都可以很好的抑制靜電放電沖擊;

5)可將PCB的GND與外殼地進行單點接地,防止靜電放電電流在機箱上產生的電壓耦合進電路,但需注意接地點的選擇,選擇

2023-05-08 18:28:47

或者變壓器,以及結合介質隔離和屏蔽,都可以很好的抑制靜電放電沖擊;

5)可將PCB的GND與外殼地進行單點接地,防止靜電放電電流在機箱上產生的電壓耦合進電路,但需注意接地點的選擇,選擇在電纜入口處接地

2023-05-12 11:52:56

開關電源電路和數字電路中的時鐘電路是目前電子產品中最主要的電磁干擾源,它們是電磁兼容設計的主要內容。那么如何針對性避免靜電放電及EMI設計,需要重點考慮有哪些要點?

2019-08-22 10:06:59

靜電放電是普遍存在的自然現象(當充有電荷的物體靠近或接觸一個導體時,電荷就要發生轉移,這就是靜電放電)。無處不在的影響著電子產品,是一種危害程度極高的電磁能量。只有提高電子產品抗靜電能力水平,才能

2018-01-03 10:22:07

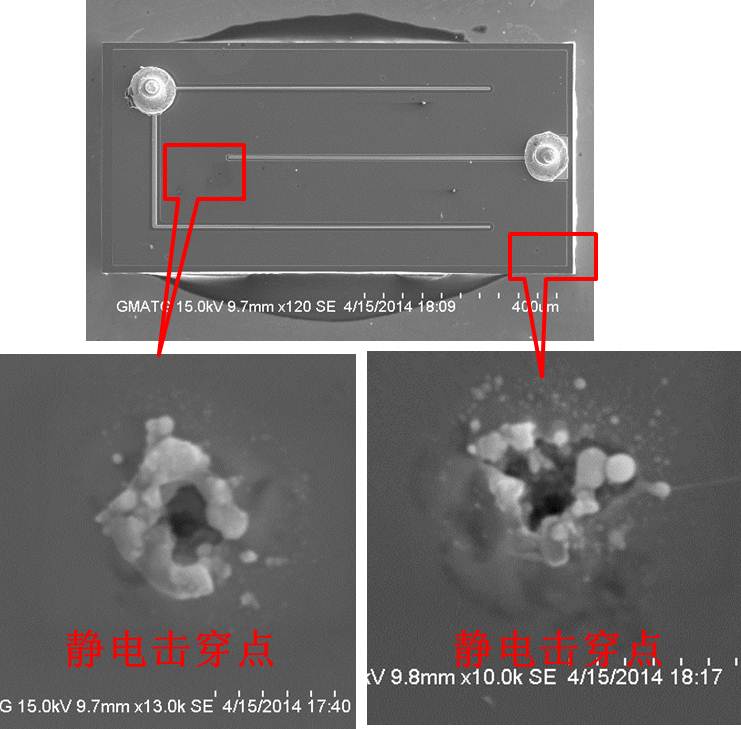

LED死燈有很多種原因,但由于LED本身抗靜電能力弱,因此,大部分死燈都是由于靜電擊穿造成的。LED內部的PN結在應用到電子產品的制造、組裝篩選、測試、包裝、儲運及安裝使用等環節,難免不受靜電

2013-06-03 12:57:51

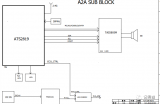

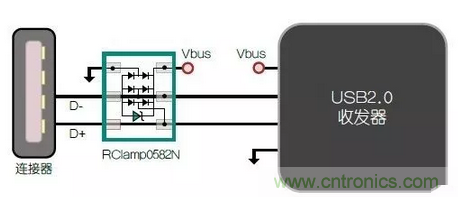

正常通訊。 USB計算器將輸入的數據保存到存儲模塊中,通過計算模塊進行數據運算,最后將數據傳輸至PC主機。解決該過程相關的ESD靜電問題,是提高USB計算器抗靜電性能的關鍵。安達森科技為你提供專門針對USB接口的防靜電電子元器件。

2013-12-21 09:52:50

,然后又重新燒寫程序就好了。 如果又遇到靜電又會丟失 Flash內容…………結論是 CC2540抗靜電能力太差了, 不知道有沒有什么方法可以改善? 或者 CC2541會不會好一點?

2016-04-27 10:46:56

也許是指導PCB布局、系統布局以及接地的最合適人選。深思熟慮的規劃以及實施能幫助實現好的結果。考慮在靜電放電過程中電流的流向,考慮電流的兩個極性來確保安全的電流路徑。最好能把放電路徑限制到接入點附近

2018-09-21 09:54:40

隨著電子技術的以及集成電路的發展,電子設備日趨小型化、多功能及智能化。然而高集成度的電路元件都可能因靜電電場和靜電放電(ESD)引起失效,導致電子設備鎖死、復位、數據丟失而影響設備正常工作,使

2021-01-06 17:26:05

靜電放電(ESD, electrostatic discharge )是在電子裝配中電路板與元件損害的一個熟悉而低估的根源。它影響每一個制造商,無任其大小。雖然許多人認為他們是在ESD安全的環境中生

2018-10-11 16:10:23

防靜電咨訊網上了解了很可能是靜電放電的原因,對于手機,在正常使用下,手機不接地,加之夏季天氣會很干燥,人體靜電自然多一些,上述靜電現象很可能是這個原因,合成纖維衣服與皮膚相互摩擦而產生靜電,靜電的電壓

2013-03-15 11:25:19

抗靜電為什么是三極管優于MOS?那么三極管和MOS管抗靜電?接下來就跟著深圳比創達EMC小編一起來看下吧!

首先要了解電子元件的特性,三極管是電流驅動元件,MOS管是電壓驅動元件,為什么說MOS管用

2023-09-25 10:56:07

什么是靜電放電?什么是電遷移?

2021-06-17 07:34:44

—05 單電源運放電路實例從零學運放—06 運放中器件介紹&音頻功放電路從零學運放—07 理想晶體管-運放從零學運放—08 積分電路_開關電源等一些電路講解從零學運放—09 電容電感PCB

2017-04-08 16:44:35

,以及排列緊密的信號線-地線間距能夠減小共模阻抗和感性耦合,使之達到雙面PCB的1/10到1/100。對于頂層和底層表面都有元器件、具有很短連接線。 來自人體、環境甚至電子設備內部的靜電對于精密

2018-08-27 15:54:33

失效的電路。經過反復試驗,出現重復性; (2)拿幾塊合格的CMOS電路進行抗靜電能力測試。測試結果為一級(0~1999)V。實測試結果,該批CMOS電路的抗靜電能力為(600~1100)V。分析:1

2018-06-08 10:37:27

微電子電路面臨的風險比以往任何時候都大,罪魁禍首是靜電放電(ESD)。靜電放電是隱秘的殺手,特別容易攻擊敏感的 IC。單次靜電放電事件就可以將 PCB 摧毀。抗靜電放電設計只要錯失一步就可能意味著

2020-01-03 09:15:31

電場的能量達到一定程度后,擊穿其間介質而進行放電的現象就是靜電放電. 4、靜電敏感度:元器件所能承受的靜電放電電壓. 5、靜電敏感器件:對靜電放電敏感的器件. 6、接地:電氣連接到能供給或接受大量電荷

2019-07-02 06:42:48

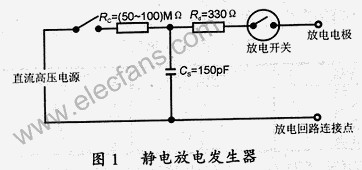

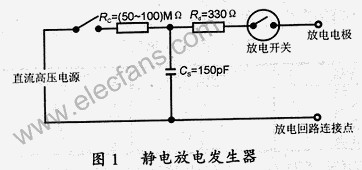

請問各位大神,在靜電放電抗擾度試驗中,靜電放電發生器的直流高壓電源、充電電阻、放電電阻、儲能電容器、放電開關、等等的各項具體要求是什么?比如功率,電流,耐壓值什么的。希望大家可以幫助我這個小菜鳥,我是剛剛開始學習EMC。謝謝!!!

2013-12-22 15:47:30

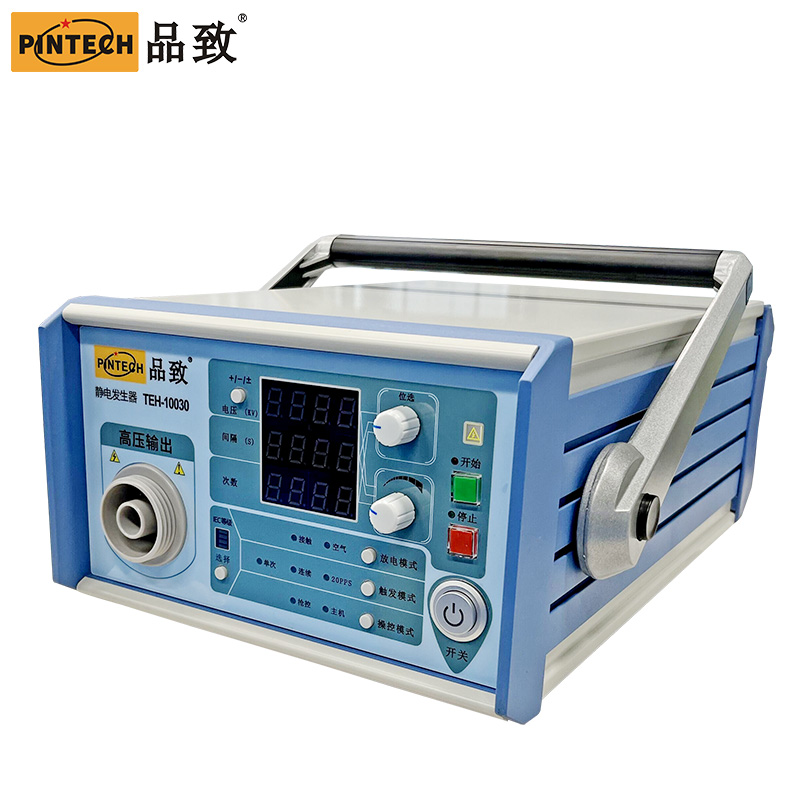

是測試樣機抗靜電干擾能力,為評估手機在實際使用中抗靜電能力提供數據支持。靜電測試需要在溫度15℃~ 35℃,濕度 30% ~ 60% 的環境下進行,測試需要用到的工具有靜電

2017-09-29 11:58:21

。本文介紹了手機靜電放電測試的要求和方法,總結分析了手機靜電放電抗擾度試驗的主要失效現象和模式, 可供手機靜電放電抗擾度試驗及提高手機抗靜電能力設計時參考。

2019-07-25 06:51:33

汽車整車靜電放電測試[qq]1611675225[/qq] 汽車靜電放電試驗分為直接放電和間接放電兩種放電方式。其中直接放電是對受試設備放電,間接放電是對耦合板的放電。汽車靜電放電抗擾度測試標準

2016-02-23 21:48:50

來源:看點快報本篇文章主要針對靜電放電的一些難點進行一個匯總,進而進行詳細的分析,跟著小編一起來看看吧!靜電放電ESD(Electro-Static Discharge)是EMC測試常見的項目之一

2020-10-23 09:28:57

本帖最后由 jinyi7016 于 2019-9-5 14:13 編輯

電阻屏如何抗靜電:接觸6kV,空間8kV

2019-09-05 09:32:41

隨著半導體制程技術的不斷演進,以及集成電路大量的運用在電子產品中,靜電放電已經成為影響電子產品良率的主要因素。美國最近公布因為靜電放電而造成的國家損失,一年就高達兩百多億美金,而光是電子產品部份

2019-07-25 06:45:53

板邊緣。 PCB要插入機箱內,不要安裝在開口位置或者內部接縫處。 要注意磁珠下、焊盤之間和可能接觸到磁珠的信號線的布線。有些磁珠導電性能相當好,可能會產生意想不到的導電路徑。 如果一個機箱或者主板要內裝幾個電路板,應該將對靜電最敏感的電路板放在最中間。

2018-09-17 17:34:36

μModule電源穩壓器LTM4644的抗靜電等級多少?能耐多少kV的靜電電壓呢?

人體接觸靜電電壓值(HBM)多少?

2024-01-05 07:10:08

運放電路PCB設計技巧

2020-12-29 07:50:05

隨著集成電路及電子設備的廣泛應用,人體靜電放電的危害性日益引起人們的重視。首先介紹人體靜電放電模型及測試方法,然后闡述幾種新型集成化靜電放電保護器件的原理與應

2009-08-05 15:04:54 114

114 盡管印刷線路板(PWB,通常也稱之為PCB)的設計會對下述三種效應都產生影響,但是主要是對第三種效應產生影響。

1. 靜電放電之前靜電場的效應2. 放電產生的電荷注入

2010-06-12 15:43:49 58

58 靜電放電(ESD)是大家熟知的電磁兼容問題,它可引起電子設備失靈或使其損壞。當半導體器件單獨放置或裝入電路模塊時,即使

2010-08-19 12:13:07 30

30 靜電放電發生器及電路

靜電放電的起因

&

2010-03-04 09:17:45 2893

2893

PCB設計時怎樣抗靜電放電

靜電對于精密的半導體芯片會造成各種損傷,例如穿透元器件內部薄的絕緣層;損毀MOSFET和CMOS元器件的柵極

2010-03-13 14:55:50 1661

1661 內容提要 一、何謂ESD 二、靜電的產生機理 三、靜電的危害 四、靜電放電模型 五、電子工作區的靜電防護 六、靜電消除方法 七、靜電接地的目的 八、靜電防護設備要求 九、人員訓練

2011-03-23 13:39:52 1412

1412 本文介紹了手機靜電放電測試的要求和方法, 總結分析了手機靜電放電抗擾度試驗的主要失效現象和模式, 可供手機靜電放電抗擾度試驗及提高手機抗靜電能力設計時參考。

2011-10-20 10:02:18 3375

3375 ESD 是代表英文ElectroStatic Discharge 即靜電放電的意思。ESD 是本世紀中期以來形成的以研究靜電的產生與衰減、靜電放電模型、靜電放電效應如電流熱(火花)效應(如靜電引起的著火與

2011-11-25 14:05:43 125

125 將大尺寸的靜電放電防護元件放置在靠近射頻電路之輸入端,可以提供很高的靜電放電耐受程度。但是其寄生的電容負載卻造成寬頻電路的阻抗無法良好匹配以及頻寬衰減的問題。傳統

2011-11-29 14:44:27 36

36 在深次微米半導體製程中,由于元件尺寸微縮,元件的靜電放電(ElectrostaticDischarge,ESD) 耐受度相對變差,因此靜電放電防護設計在IC 設計時即必需被加入考量 [1]。通常商用IC 的靜電放

2011-11-30 09:55:40 51

51 由于CMOS器件靜電損傷90%是延遲失效,對整機應用的可靠性影響太大,因而有必要對CMOS器件進行抗靜電措施。本文描述了CMOS器件受靜電損傷的機理,從而對設計人員提出了幾種在線路設

2012-02-02 10:53:26 54

54 gb17626.2-1998(ESD)靜電放電抗擾度

2016-03-22 14:46:36 26

26 現行國家標準:靜電放電抗擾度試驗

2016-12-09 15:10:30 8

8 靜電放電原理

2016-12-30 15:22:44 0

0 先來談靜電放電(ESD: Electrostatic Discharge)是什么?這應該是造成所有電子元器件或集成電路系統過度電應力破壞的主要元兇。

2017-02-10 02:10:11 3974

3974

RDA5807FP-抗靜電8000V收音機文檔資料

2017-09-01 14:46:42 133

133 ,光衰加重,甚至出現死ce燈現象,靜電對LED品質有非常重要的影響。LED的抗靜電指標絕不僅僅是簡單地體現它的抗靜電強度,LED的抗靜電能力與其漏電值、整體可靠性有很大關系,更是一個整體質素和可靠性的綜合體現。因為往往抗靜電高的LED,它的光特性、電特性

2017-10-12 18:00:32 10

10 隨著半導體制程技術的不斷演進,以及集成電路大量的運用在電子產品中,靜電放電已經成為影響電子產品良率的主要因素。美國最近公布因為靜電放電而造 成的國家損失,一年就高達兩百多億美金,而光是電子產品部份

2017-11-08 15:45:02 16

16 一種普通的物理過程。靜電產生不僅取決于材質,而且在相當程度上還與外界因素有關。運動摩擦可引起靜電放電效應。以下是我們日常生產活動中所產生的靜電電壓; 3、LED抗靜電與襯底材質 摩擦產生靜電的強弱與材質的電阻率有關,電

2017-11-14 10:19:35 7

7 電場的能量達到一定程度后,擊穿其間介質而進行放電的現象就是靜電放電. 4、靜電敏感度:元器件所能承受的靜電放電電壓. 5、靜電敏感器件:對靜電放電敏感的器件. 6、接地:電氣連接到能供給或接受大量電荷的物體,如大地、船

2017-11-23 05:45:51 1089

1089 微電子電路面臨的風險比以往任何時候都大,罪魁禍首是靜電放電(ESD)。這些禍害是隱秘的殺手,特別容易攻擊敏感的IC。單次靜電放電事件就可以將PCB送入地獄。抗靜電放電設計只要錯失一步就可能意味著延誤上市時間、影響開發進度,以及激怒客戶。在某些高壓力情況下,甚至意味著你的飯碗不保。

2018-06-05 15:40:00 3778

3778

汽車電子車聯網的普及,敏感器件的大量使用,要求汽車級的抗靜電ESD元件,抗靜電能力高達30KV,抗浪涌能力也是越高越好。現在市面上的ESD,很多還是按消費級標準8KV接觸 15KV空氣靜電生產,沒法滿足汽車電子要求標準。

2018-06-01 08:07:00 5

5 盡可能使用多層PCB,相對于雙面PCB而言,地平面和電源平面,以及排列緊密的信號線-地線間距能夠減小共模阻抗和感性耦合,使之達到雙面PCB的 1/10到1/100.盡量地將每一個信號層都緊靠一個電源層或地線層。對于頂層和底層表面都有元器件、具有很短連接線以及許多填充地的高密度PCB,可以考慮使用內層線。

2019-08-17 17:35:00 1818

1818 PCB設計中,對于靜電的防護,一般采用隔離、增強單板靜電免疫力和采用保護電路三項措施來進行設計。

2019-05-24 15:49:57 16325

16325 靜電放電(ESD)理論研究的已經相當成熟,為了模擬分析靜電事件,前人設計了很多靜電放電模型。

2019-08-11 11:46:41 8831

8831

在pcb板的設計當中,可以通過分層、恰當的布局布線和安裝實現PCB的抗ESD設計。

2020-04-01 17:40:18 1760

1760 在pcb板的設計當中,可以通過分層、恰當的布局布線和安裝實現PCB的抗ESD設計。

2019-08-22 11:02:49 449

449 了手機靜電放電測試的要求和方法,總結分析了手機靜電放電抗擾度試驗的主要失效現象和模式,可供手機靜電放電抗擾度試驗及提高手機抗靜電能力設計時參考。

2020-07-10 10:29:00 6

6 .靜電電場的能量達到一定程度后,擊穿其間介質而進行放電的現象就是靜電放電.

4、靜電敏感度:元器件所能承受的靜電放電電壓.

5、靜電敏感器件:對靜電放電敏感的器件.

6、接地:電氣連接到能供給或接受大量電荷的物體,如大地、

2020-07-24 18:54:00 5

5 來源:羅姆半導體社區? 微電子電路面臨的風險比以往任何時候都大,罪魁禍首是靜電放電(ESD)。靜電放電是隱秘的殺手,特別容易攻擊敏感的 IC。單次靜電放電事件就可以將 PCB 摧毀。抗靜電放電

2022-11-15 16:23:37 964

964 依據標準IEC 61000-4-2/GBT17626.2的定義,靜電放電就是具有不同靜電電位的物體相互靠近或直接接觸引起的電荷轉移。 當人體穿著絕緣材料的織物并且對地絕緣時,在地面上運動時可能積累

2020-11-19 10:29:47 7976

7976 介紹靜電放電的基礎知識。

2021-03-22 15:39:12 29

29 電子發燒友網為你提供PCB板中靜電放電的設計與解決方法資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-04 08:52:11 36

36 ,光衰加重,甚至出現死燈現象,靜電對LED品質有非常重要的影響。LED的抗靜電指標絕不僅僅是簡單地體現它的抗靜電強度,LED的抗靜電能力與其漏電值、整體可靠性有很大關系,更是一個整體質素和可靠性的綜合體

2021-07-15 15:40:27 854

854 靜電放電問題案例分析資源下載

2021-07-01 09:45:31 11

11 微電子電路面臨的風險比以往任何時候都大,罪魁禍首是靜電放電(ESD)。這些禍害是隱秘的殺手,特別容易攻擊敏感的IC。單次靜電放電事件就可以將PCB送入地獄。抗靜電放電設計只要錯失一步就可能意味著延誤

2022-02-10 11:48:27 2

2 靜電放電抗擾度試驗。模擬操作員或物體接觸設備時產生的放電,以及人員或物體相對于相鄰物體的放電,以測試被測設備對靜電放電的干擾能力

2022-09-05 09:48:49 15

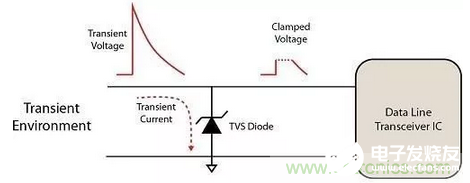

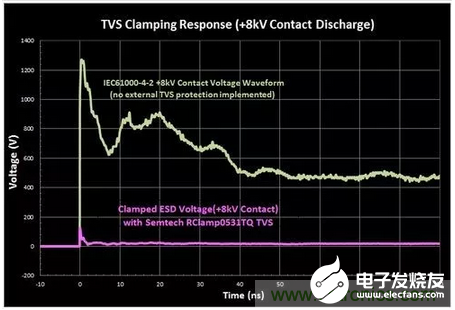

15 靜電放電對電路的影響主要是通過電壓、電流和能量傳遞的方式產生的。靜電放電是由于電荷積累在物體表面,當電荷之間或物體與接地之間存在電勢差時,會發生電荷的突然釋放,形成放電現象。 靜電放電可能對電路產生

2023-06-07 10:27:18 552

552 在干燥的環境下,人體靜電(ESD)的電壓很容易超過6~35Kv,當用手觸摸電子設備、PCB或PCB上的元器件時,會因為瞬間的靜電放電,而使元器件或設備受到干擾,甚至損壞設備或PCB上的元器件。

2023-07-04 09:07:44 1004

1004

在pcb板的設計當中,可以通過分層、恰當的布局布線和安裝實現PCB的抗ESD設計。在設計過程中,通過預測可以將絕大多數設計修改僅限于增減元器件。通過調整PCB布局布線,能夠很好地防范ESD。

2023-07-20 14:52:15 412

412 靜電放電的產生有兩個基本條件,一. 是電荷的積累,電荷的積累是前提,然后是“跨接”,電荷的劇烈流動就是放電。所以從這兩個方面就行控制就能有效地防護靜電放電的產生。

2023-09-05 11:08:19 479

479

三極管和MOS管抗靜電?|深圳比創達EMC

2023-09-25 10:54:53 343

343

靜電放電是一種自然現象 ,當兩種不同介電強度的材料相互摩擦時,就會產生靜電電荷,當其中一種材料上的靜電荷積累到一定程度,在與另外一個物體接觸時,就會通過這個物體到大地的阻抗而進行放電。靜電放電及影響是電子設備的一個主要干擾源。

2023-09-26 14:48:42 342

342

因為靜電積聚或者電壓過高而引起的,電子產品中如果存在電容器、電感器等元件,這些元件會積聚電荷,當電壓過高或者其他因素造成電壓跳變時,這些電荷會以尖端的形式放電,從而燒毀電路板上的某些部件。 雖然 PCB尖端放電的原因很多,但是可以

2023-11-06 10:14:25 737

737 在PCB板的設計當中,可以通過分層、恰當的布局布線和安裝實現PCB的抗ESD設計。在設計過程中,通過預測可以將絕大多數設計修改僅限于增減元器件。通過調整PCB布局布線,能夠很好地防范ESD。以下是一些常見的防范措施。

2023-11-20 15:28:27 158

158 靜電放電對電路的影響主要是通過電壓、電流和能量傳遞的方式產生的。靜電放電是由于電荷積累在物體表面,當電荷之間或物體與接地之間存在電勢差時,會發生電荷的突然釋放,形成放電現象。

2023-11-21 16:28:41 612

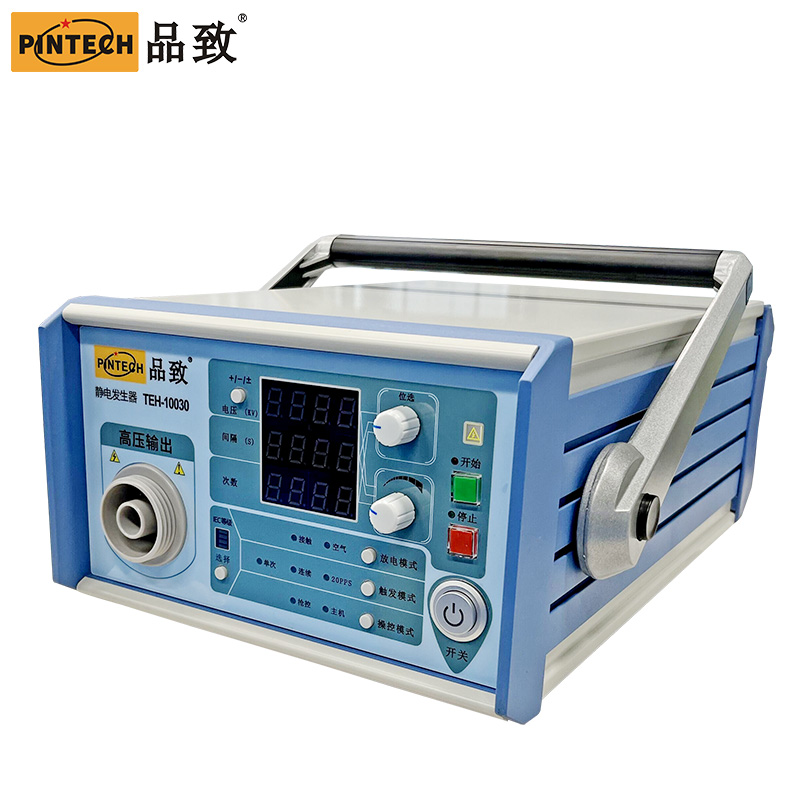

612 (ESD)等靜電相關環境下的耐受能力的設備。它主要通過模擬靜電放電的幅值、頻率和波形來模擬現實環境中的ESD事件,以驗證設備的耐受能力和性能。 靜電放電發生器的原理: 靜電放電發生器主要由電源、高壓發生電路、儲存電容器、接觸裝置以及控制、顯示系統等組成。其中,電源提

2023-11-23 10:07:22 668

668 靜電放電與電路在一些環境下,靜電很容易積累并在放電的時候產生很大的電擊。我們做個實驗,穿著襪子在地毯上來回走動,然后去觸碰別人引起別人電擊驚嚇。被電擊后驚訝之余,我們并不太擔心,因為普通靜電不會

2023-11-23 10:06:40 201

201

依據靜電放電產生原因及其對集成電路放電方式的不同,靜電放電模型可分成以下四類模型:1、人體放電模型(HBM,Human-BodyModel)、2、機器放電模型(MM,MachineModel

2023-11-24 08:13:23 243

243

控制靜電放電的三個基本原則? 控制靜電放電是一項關鍵的工程問題,尤其是在現代工業中。靜電放電不僅可能損壞電子設備和電子元件,還可能引發火災和爆炸等安全問題。為了有效地控制靜電放電,我們需要遵循三個

2024-01-03 11:00:40 390

390 靜電對集成電路板的危害 靜電是指帶電物體之間的電荷差異引起的電力現象,在日常生活中經常出現。雖然靜電可以帶來一些有趣的現象,但它也對集成電路板(PCB)造成了嚴重的危害。本文將詳細分析靜電對PCB

2024-01-03 11:09:38 479

479 最容易在導電材料上產生,因此選擇具有良好防靜電性能的材料是防止靜電放電損傷的基礎。常見的防靜電材料包括抗靜電塑料、抗靜電硅膠等,這些材料能夠有效吸收和分散靜電,減小靜電放電的能量。 2. 使用靜電消除器:靜電消除器是

2024-01-03 11:43:27 230

230

電子發燒友App

電子發燒友App

評論