自動(dòng)測(cè)試設(shè)備、儀器、精密醫(yī)療設(shè)備和過程控制都需要在轉(zhuǎn)換器的激勵(lì)放大器(運(yùn)算放大器)與模數(shù)轉(zhuǎn)換器 (ADC) 之間實(shí)現(xiàn)良好的噪聲規(guī)格匹配。但由于運(yùn)算放大器與 ADC 的規(guī)格存在不一致,因此設(shè)計(jì)人員如果

2018-07-03 09:29:31 6547

6547

影響放大器性能的誤差項(xiàng)有哪些?當(dāng)今的放大器已很難滿足高難度的技術(shù)規(guī)范組合,設(shè)計(jì)師們?cè)?b class="flag-6" style="color: red">怎樣去開發(fā)具有適合的交流和直流性能組合的現(xiàn)代高速放大器?

2021-04-12 06:05:24

怎樣去檢查低壓差測(cè)量中的誤差問題?如何檢測(cè)RFI?差分放大器共模抑制功能有幫助嗎?

2021-04-29 06:14:01

4通道D類音頻放大器的特性和功能是什么?怎樣去設(shè)計(jì)一種4通道D類音頻放大器?

2021-06-04 06:36:54

怎樣去避免運(yùn)算放大器增益誤差?來自高速設(shè)計(jì)專家的告誡是:您應(yīng)該避免使用相對(duì)您的應(yīng)用而言速度過快的模擬器件。

2021-04-13 06:07:36

在實(shí)際應(yīng)用中,必須處理日益增多的射頻干擾(RFI),對(duì)于信號(hào)傳輸線路較長(zhǎng)且信號(hào)強(qiáng)度較低的情況尤其如此,而儀表放大器的典型應(yīng)用就是這種情況,因?yàn)槠鋬?nèi)在的共模抑制能力,它能從較強(qiáng)共模噪聲和干擾中提取較弱

2019-06-24 08:04:48

的輸入更接近于正電壓軌時(shí),NMOS晶體管為“開”,而PMOS晶體管為“關(guān)”。這種設(shè)計(jì)拓?fù)湓?b class="flag-6" style="color: red">共模輸入范圍會(huì)存在極大的放大器失調(diào)電壓差異。在接地電壓附近的輸入范圍,PMOS晶體管的失調(diào)誤差為主要誤差。在

2019-06-20 06:50:04

專注于重要的信號(hào)...比賽。信號(hào)通過量及中斷我看比賽的程度類似于放大器CMRR。在真正談?wù)揅MRR之前,必須先談?wù)?b class="flag-6" style="color: red">共模電壓。對(duì)于非反相配置的放大器,輸入信號(hào)是共模信號(hào)。反相配置始終具有與輸入信號(hào)無關(guān)

2019-03-20 06:45:09

源流入放大器輸入端。其中,共模輸入阻抗(Zcm+、Zcm–)是放大器任一輸入端與地之間阻抗,Zcm+、Zcm–阻抗值近似相同,數(shù)據(jù)手冊(cè)中通常不區(qū)分。差分輸入阻抗(Zdiff-)是放大器的兩個(gè)輸入端之間

2021-01-02 08:00:00

具有低輸入偏置電流和高交流共模抑制性能的高速FET輸入儀表放大器

2021-04-06 09:16:55

的影響,最簡(jiǎn)單的方法是采用等電位屏蔽的措施,即不把電纜的屏蔽層接地,而是接到與輸入共模信號(hào)相等的某等電位點(diǎn)上,亦即使電纜芯線與屏蔽層之間處于等電位,從而消除了共模輸入信號(hào)在差動(dòng)放大器兩端形成的誤差電壓

2018-10-08 10:27:27

特性。雖然AD623是為單電源優(yōu)化的,其在雙電源供電下依然能提供相差無幾的性能。需要注意的是,AD623采用的是3運(yùn)放的標(biāo)準(zhǔn)儀表放大器電路,故如果在單電源狀態(tài)下工作,輸入信號(hào)的共模電壓需要貼近VCC/2

2023-11-23 08:27:19

,那么對(duì)應(yīng)的輸出失調(diào)電壓將變化100mV。 其中 Vout 為輸出失調(diào)電壓;Vcm 為輸入共模電壓;即輸入端對(duì)地共模電壓與 Vref 之間的差值;Gain 為儀表放大器的增益。從公式上看,儀表放大器

2019-03-12 06:45:04

。JFET放大器電流和功率增益前面我們?cè)f過,由于極高的柵極阻抗Rg,共源JFET放大器的輸入電流Ig非常小。因此,共源JFET放大器在其輸入阻抗和輸出阻抗之間具有非常好的比率,并且對(duì)于任何數(shù)量的輸出

2020-11-03 09:34:54

大家好,為什么有些差分放大器可以工作在很高的共模電壓條件下,比如說AD629就可以工作在正負(fù)290V的共模電壓下,是因?yàn)樾酒瑑?nèi)部有特殊處理的電路嗎?

2023-11-20 07:10:42

在一些需要正弦激勵(lì)源的電橋激勵(lì)下,儀表放大器輸入RFI濾波器共模濾波和差模濾波截止頻率的選取?

參考儀表放大器指南:

按照描述,本截止頻率應(yīng)該針對(duì)直流電壓激勵(lì)電橋,所以截止頻率設(shè)置略高于

2023-11-20 07:01:41

得放大器的輸出端和ADC的輸入端之間共模簡(jiǎn)單對(duì)齊,兩者均需在AIN+和AIN?保持+0.525 V。同樣,注意幾個(gè)接地使能的放大器引腳功能(VSS),單電源現(xiàn)強(qiáng)制 設(shè)置為?2 V供電(新VSS)。CM電壓

2018-10-11 10:34:45

儀表放大器AD620的共模輸入范圍超過電源電壓,會(huì)影響共模抑制比嗎?比如AD620采用正負(fù)5V電源供電,放大倍數(shù)為10倍,測(cè)試時(shí)共模輸入范圍為7.07V / 100Hz,會(huì)影響共模抑制比嗎?

2023-11-15 06:49:17

初學(xué)者向各位請(qǐng)教一些問題!

1.儀表放大器和普通運(yùn)算放大器有什么不同呢?二者在組建電路上有什么區(qū)別呢?

2.使用儀表放大器對(duì)差分輸入信號(hào)自身的性能有什么要求嗎?(比如共模電壓要到一定值,這是

2023-11-20 07:56:29

1.儀表放大器的誤差預(yù)算計(jì)算2.儀表放大器設(shè)計(jì)中的常見陷阱3.儀表放大器的輸入共模電壓范圍4.儀表放大器共模范圍:鉆石圖(應(yīng)用筆記)5.使用鉆石圖工具(視頻)

2021-01-21 07:49:48

的差分電壓,抑制兩個(gè)輸入端的共模。 圖 2:三運(yùn)算放大器儀表放大器的標(biāo)準(zhǔn)拓?fù)?b class="flag-6" style="color: red">放大器的輸入級(jí)包含兩個(gè)放大器:A1 和 A2。電源電壓或共模電壓的變化會(huì)帶來這兩個(gè)放大器輸入失調(diào)的相應(yīng)變化,在圖 3 中分

2018-09-19 10:53:42

輸出信號(hào)升高同等電壓。這樣就能簡(jiǎn)單精確地將儀表放大器的輸出調(diào)整到ADC所需的輸入電平,從而可以使用ADC的完整輸入范圍,同時(shí)提高分辨率。在具有高共模信號(hào)的情況下,另一優(yōu)勢(shì)是極為出色的共模抑制比和高精度。

2019-07-19 07:24:39

描述此參考設(shè)計(jì)展示了高速放大器 THS4509 執(zhí)行單端至差動(dòng)轉(zhuǎn)換以驅(qū)動(dòng)高速模數(shù)轉(zhuǎn)換器 (ADC),同時(shí)保持卓越的噪聲和失真性能的能力。為交流和直流耦合應(yīng)用顯示了連接到 ADS4449 四通

2018-08-09 08:38:52

。兩個(gè)輸入端通常共用一個(gè)大共模電壓。差分放大器會(huì)抑制共模電壓,剩余電壓經(jīng)放大后,在放大器輸出端表現(xiàn)為單端電壓。共模電壓可以是交流或直流電壓,此電壓通常會(huì)大于差分輸入電壓。抑制效果隨著共模電壓頻率增加而降

2018-10-11 10:44:09

全差分儀表放大器具有其他單端輸出放大器所沒有的優(yōu)勢(shì),它具有很強(qiáng)的共模噪聲源抗干擾性,可減少二次諧波失真并提高信噪比,還可提供一種與現(xiàn)代差分輸入ADC連接的簡(jiǎn)單方式。低功耗全差分儀表放大器電路怎么設(shè)計(jì)?

2021-04-06 08:11:07

電路是高速FET輸入,增益為-5的儀表放大器(儀表放大器),具有寬帶寬(35 MHz)和出色的交流共模抑制CMR(10 MHz時(shí)為55 dB)。該電路非常適用于需要高輸入阻抗,快速儀表放大器的應(yīng)用,包括RF,視頻,光信號(hào)檢測(cè)和高速儀器。高CMR和帶寬也使其成為寬帶差分線路接收器的理想選擇

2020-06-04 14:22:34

這些轉(zhuǎn)換器時(shí),必須使用放大器來防止發(fā)生輸入負(fù)載。對(duì)于快速采樣速率,ADC輸入需要在數(shù)字化開始之前快速穩(wěn)定在0.5 LSB以內(nèi),由于其增益帶寬積更大,因此可以使用高速放大器,從而實(shí)現(xiàn)環(huán)路增益并改善穩(wěn)定性

2019-08-21 04:45:05

關(guān)于測(cè)量放大器共模抑制能力的研究,看完你就懂了

2021-04-14 06:11:07

描述數(shù)字可變?cè)鲆?b class="flag-6" style="color: red">高速放大器 LMH6401 可驅(qū)動(dòng)高速模數(shù)轉(zhuǎn)換器 (ADC) ADS54J60 器件,此參考設(shè)計(jì)討論了其使用和性能。此參考設(shè)計(jì)討論并測(cè)量了共模電壓、電源和接口的不同選項(xiàng)(包括交流耦合

2022-09-19 06:09:01

Chau Tran和Jordyn RombolaADI公司簡(jiǎn)介在許多應(yīng)用中,ADC需要在存在大共模信號(hào)的情況下處理一個(gè)很小的差分輸入信號(hào)。傳統(tǒng)的儀表放大器(In-Amp)只具有單端輸出和有限的共模范

2018-10-19 10:30:35

設(shè)置的單片電阻網(wǎng)絡(luò)過于龐大且成本較高。此外,大多數(shù)分立式運(yùn)算放大器電路的共模抑制都比較差,并且輸入電壓范圍小于電源電壓。雖然單片差分放大器的共模抑制比較好,但由于片內(nèi)器件與外部增益電阻之間本身不匹配

2019-07-05 07:09:03

號(hào)就屬于這種情況。根據(jù)前面的假設(shè)條件,在電阻失配的情況下,這個(gè)電路就不再是一個(gè)真正的差分放大器,VO會(huì)隨著共模分量而變化。 小結(jié) 運(yùn)算放大器,如果選取恰當(dāng)?shù)耐獠吭軌驑?gòu)成各種運(yùn)算電路,如放大、加、減、微分和積分等運(yùn)算電路。運(yùn)算放大器實(shí)現(xiàn)數(shù)學(xué)運(yùn)算的能力,是將高增益與負(fù)反饋結(jié)合起來的結(jié)果。

2021-02-20 16:21:09

電壓設(shè)置運(yùn)算放大器的共模輸出電壓的能力。這是因?yàn)轵?qū)動(dòng)ADC輸入的信號(hào)放大器將共模輸出電壓(VCMO)設(shè)置在最適合的ADC范圍內(nèi)是很重要的。如果不能滿足這些條件,ADC的性能會(huì)隨著放大器的VCMO和ADC

2011-07-28 09:32:59

TI高精度實(shí)驗(yàn)室-運(yùn)算放大器-第七節(jié)-共模抑制和電源抑制抑制可能是一件好事,特別是在共模或電源電壓錯(cuò)誤的情況下。 本系列視頻介紹了如何改變運(yùn)算放大器的共模電壓或電源電壓,從而在交流和直流兩端引入誤差

2021-12-30 06:50:21

如何設(shè)計(jì)用于運(yùn)算放大器的共模反饋電路?共模反饋電路的設(shè)計(jì)要點(diǎn)有哪些?全差分運(yùn)算放大器的共模反饋原理是什么?

2021-04-20 06:17:09

都可作為共模噪聲耦合。很多差分器件都能很好地抑制這種噪聲。下面是 LMH6881 可編程差分放大器 (PDA) 的共模抑制比 (CMRR) 圖示。CMRR 可確定差分信號(hào)受共模噪聲干擾的“污染程度

2022-11-21 06:34:35

很好了,但卻沒有回答如何顯著降低運(yùn)算放大器功耗的問題。那么我們應(yīng)該如何做呢?ADS7881 是一款 12 位 ADC,電壓輸入范圍介于 0V 至 +2.5V 之間。我選用 OPA836 作為放大器

2018-09-21 15:16:44

共模抑制和差模信號(hào)介紹不同結(jié)構(gòu)的儀表放大器解析

2021-04-07 06:04:27

公司產(chǎn)品需要用到電流檢測(cè),使用的是AD620,正負(fù)15V供電,原設(shè)計(jì)的IN+和IN-的最大共模輸入電壓為12V,所以AD620可以正常工作。 現(xiàn)在要做一款新的基板,也要用到儀表放大器,但其

2018-11-12 15:10:21

我想設(shè)計(jì)采集200~300MHz的信號(hào)的系統(tǒng),首先2路反相的信號(hào)輸入差動(dòng)放大器,然后差動(dòng)放大器輸出接1G采樣率的高速采集卡,接著當(dāng)采集到信號(hào)高于某一閾值時(shí)將其輸出到電腦里,其他時(shí)間采集的的信號(hào)不輸出。我想請(qǐng)問這樣設(shè)計(jì)是否合理,差動(dòng)放大器應(yīng)該怎么選擇,高速采集卡只輸出大于某一閾值的信號(hào)能否實(shí)現(xiàn)

2012-06-09 22:18:09

的噪聲(例如本地振蕩器或混頻器寄生信號(hào)),那么對(duì)噪聲而言會(huì)怎樣呢?正如我們從 CMRR 與共模增益圖中可以看到的那樣,放大器防止共模噪聲進(jìn)入差分信號(hào)的能力以及減弱共模噪聲的能力,在更高頻率下都會(huì)顯著降低

2018-09-13 14:27:23

噪聲通常是共模的,而信號(hào)應(yīng)該是差分的,所以儀表放大器利用其共模抑制(CMR)特性將有用信號(hào)與噪聲區(qū)分開。 在儀表放大器應(yīng)用中的信號(hào)源通常具有幾千歐姆(kΩ)甚至更大的輸出阻抗,因此儀表放大器應(yīng)該具有

2018-10-17 15:06:47

影響應(yīng)變計(jì)與放大器一起使用參數(shù)是什么?怎樣去選擇合適的放大器?

2021-04-07 06:40:16

共源共柵電感的工作機(jī)理是什么?怎么實(shí)現(xiàn)共源共柵CMOS功率放大器的設(shè)計(jì)?

2021-06-18 06:53:41

請(qǐng)問大佬怎么實(shí)現(xiàn)放大器與ADC之間的共模融合?

2021-04-13 06:33:06

求一款實(shí)現(xiàn)IR接近檢測(cè)的高速運(yùn)算放大器

2021-04-25 09:00:00

用數(shù)據(jù)采集卡測(cè)試SAR ADC/DAC,數(shù)據(jù)采集卡輸出和輸入(單端)的電壓范圍是-2V-2V,SAR ADC/DAC的輸入和輸出(單端)電壓范圍是0-2.5V,想用一個(gè)帶輸出共模電壓管腳的單端運(yùn)算放大器匹配數(shù)據(jù)采集卡和SAR ADC/DAC之間的電壓范圍,求推薦,謝謝。

2023-11-15 06:37:35

求微弱電流檢測(cè)用的共模電壓范圍最大值大于65V的運(yùn)算放大器或儀表放大器

2023-11-14 07:21:08

電流反饋 (CFB) 放大器大部分歸屬高速放大器范疇;那么到底應(yīng)該怎么使用電流反饋放大器才有效?

2021-04-02 07:42:13

儀表放大器(IA)常用于需要高增益精度和高直流精度的場(chǎng)合,比如:測(cè)試測(cè)量和實(shí)驗(yàn)儀器,但這類器件成本較高。而電流檢測(cè)放大器價(jià)格便宜,能夠處理較高的共模電壓,部分特性與儀表放大器類似,如何在-48V至+5V電源變換器中,用電流檢測(cè)放大器替代儀表放大器?

2019-02-21 14:36:04

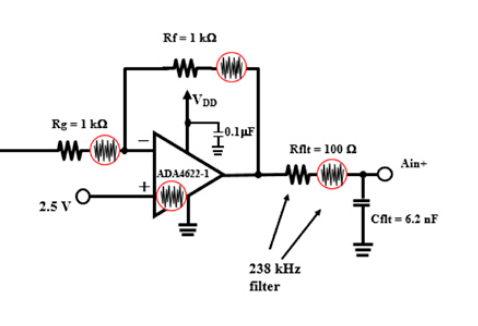

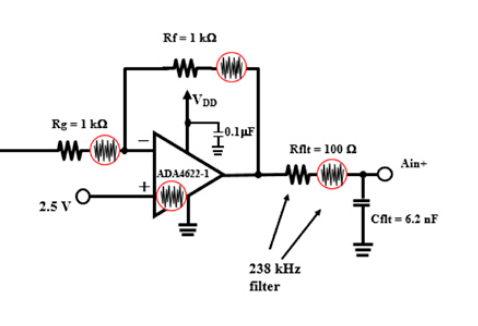

Electronics)在此電路中,使用反向放大器配置是一項(xiàng)優(yōu)勢(shì),因?yàn)?b class="flag-6" style="color: red">放大器輸入級(jí)的共模電壓將保持固定的 2.5 V。緊跟 ADA4622-1 放大器的是一個(gè) 250 kHz 的 1 階濾波器。該

2018-11-29 17:52:59

。對(duì)于快速采樣速率,ADC輸入需要在數(shù)字化開始之前快速穩(wěn)定在0.5 LSB以內(nèi),由于其增益帶寬積更大,因此可以使用高速放大器,從而實(shí)現(xiàn)環(huán)路增益并改善穩(wěn)定性能。如圖5所示,OPA2810在約130ns內(nèi)

2019-02-27 13:51:06

請(qǐng)教各位大佬們,都什么情況用到cmfb放大器,是不是抑制共模干擾,sansen書里說經(jīng)常接成單位增益形式,那還怎么抑制共模?請(qǐng)不吝賜教,謝謝但您說的是加入共模反饋支路的原因,是為了確定輸出共模電壓

2021-06-24 07:36:18

摘要ADI專利的容性可編程增益放大器(PGA)相比傳統(tǒng)的阻性PGA具有更佳的性能,包括針對(duì)模擬輸入信號(hào)的更高共模電壓抑制能力。本文描述了斬波容性放大器的工作原理,強(qiáng)調(diào)了需要放大傳感器小信號(hào)至接近供電

2018-10-31 10:20:33

CMOS運(yùn)算放大器結(jié)構(gòu)具有哪些特點(diǎn)?如何去設(shè)計(jì)CMOS運(yùn)算放大器?怎樣對(duì)CMOS運(yùn)算放大器進(jìn)行仿真測(cè)試?

2021-04-21 07:21:39

怎樣去設(shè)計(jì)一種低噪聲放大器?如何對(duì)低噪聲放大器進(jìn)行仿真?

2021-05-26 06:04:52

怎樣去設(shè)計(jì)全集成的低噪聲放大器?怎樣對(duì)全集成的低噪聲放大器進(jìn)行模擬仿真?

2021-04-21 06:18:40

為什么要設(shè)計(jì)一種可編程放大器?怎樣去設(shè)計(jì)一種可編程放大器?可編程放大器有什么優(yōu)點(diǎn)?

2021-04-22 07:06:51

前置放大器的簡(jiǎn)介怎樣去設(shè)計(jì)前置放大器?如何對(duì)前置放大器進(jìn)行仿真測(cè)試?

2021-04-21 06:24:39

可變?cè)鲆?b class="flag-6" style="color: red">放大器的分類怎樣去設(shè)計(jì)可變?cè)鲆嬷蓄l放大器?怎樣對(duì)可變?cè)鲆嬷蓄l放大器進(jìn)行仿真?

2021-04-21 06:04:59

初學(xué)者向各位請(qǐng)教一些問題!1.儀表放大器和普通運(yùn)算放大器有什么不同呢?二者在組建電路上有什么區(qū)別呢?2.使用儀表放大器對(duì)差分輸入信號(hào)自身的性能有什么要求嗎?(比如共模電壓要到一定值,這是為什么呢

2018-08-19 07:02:41

麻煩問一下,我想做檢測(cè)電流,儀表放大器的最大共模電壓該如何確定啊?我看到的都是共模抑制比。。希望得到解答。謝謝

2019-01-02 11:02:20

如何實(shí)現(xiàn)適用于高速數(shù)據(jù)采集ADC模擬前端的運(yùn)算放大器設(shè)計(jì)?

2021-04-20 07:16:44

大家好,為什么有些差分放大器可以工作在很高的共模電壓條件下,比如說AD629就可以工作在正負(fù)290V的共模電壓下,是因?yàn)樾酒瑑?nèi)部有特殊處理的電路嗎?

2018-08-22 10:26:28

運(yùn)算放大器共模抑制(CMR)的問題出在哪里呢?我們?cè)撛趺?b class="flag-6" style="color: red">去解決這個(gè)問題?

2021-04-07 06:55:35

(因?yàn)樘摱淌巧疃蓉?fù)反饋的結(jié)果,是人為的)的增大了兩輸入端的共模信號(hào),這樣就對(duì)運(yùn)算放大器的 性能構(gòu)成挑 戰(zhàn)。為什么運(yùn)算放大器要這么使用? (1)同相放大器的共模信號(hào)比反相放大器大得多對(duì)共模抑制比要求高

2019-07-21 22:54:12

非ppm放大器類型運(yùn)算放大器的誤差源輸入共模抑制和偏置誤差

2021-02-05 06:17:26

VOUT下限為50 mV。顯然,給定運(yùn)算放大器的內(nèi)部設(shè)計(jì)會(huì)影響該輸出共模動(dòng)態(tài)范圍,必要時(shí),器件本身的設(shè)計(jì)應(yīng)當(dāng)最大程度地減小VSAT(HI)和VSAT(LO),以便實(shí)現(xiàn)最大輸出動(dòng)態(tài)范圍。某些類型的運(yùn)算放大器

2014-08-13 15:34:22

為50 mV。 顯然,給定運(yùn)算放大器的內(nèi)部設(shè)計(jì)會(huì)影響該輸出共模動(dòng)態(tài)范圍,必要時(shí),器件本身的設(shè)計(jì)應(yīng)當(dāng)最大程度地減小VSAT(HI)和VSAT(LO),以便實(shí)現(xiàn)最大輸出動(dòng)態(tài)范圍。某些類型的運(yùn)算放大器就采用

2018-09-21 14:50:51

兩個(gè)器件之間的公共地有時(shí)比較隱蔽。對(duì)于放大器和模數(shù)轉(zhuǎn)換器(ADC),在指定新型信號(hào)鏈應(yīng)用時(shí)經(jīng)常會(huì)忽視這些需求,這一般是因?yàn)閿?shù)據(jù)手冊(cè)被忽略太久了!兩個(gè)器件當(dāng)然都會(huì)有些

2010-11-27 16:56:03 24

24 差分放大器驅(qū)動(dòng)高速ADC的電路

目前,用來驅(qū)動(dòng)ADC的方案有兩種,第一種是使用變壓器,第二種則是差分放大器,

新型的差分放大器

2009-03-22 15:48:27 2150

2150

軌至軌單端至差分放大器驅(qū)動(dòng)高速 16 位至 18 位 SAR ADC

2021-03-19 08:03:46 3

3 LTC6400-20 - 1GHz 和 2GHz 全差分放大器實(shí)現(xiàn)了高速 ADC 性能

2021-03-20 15:03:21 0

0 固定增益差分放大器簡(jiǎn)化對(duì)高速 ADC 的驅(qū)動(dòng)

2021-03-21 03:06:00 10

10

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論