本文中的測控系統是某型號無人機電子系統中的一個重要部分。為了對測控系統的改進優化設計進行驗證,需要對軟件進行長期運行考核,對該分系統進行單機驗收與聯試,驗證其與其它分系統接口的匹配性;同時還要為測控系統提供真實的物理連接接口、動態輸入參數,進而提供與無人機同步的仿真運行環境。遙測解調及遙控注入測試卡是根據驗證測控系統工作的需要而設計開發的,它能為其提供遙測解調、遙控數據注入、直接指令注入、觸點信號和40kHz時鐘等接口信號。能對原測控系統進行測試的遙測解調及遙控注入測試卡是ISA插卡,使用分離器件來實現。隨著計算機硬件的發展,PCI總線已經成為當今高性能微型計算機事實上的總線標準,PCI總線的性能遠遠高于ISA總線,因此基于PCI的遙測解調及遙控注入測試卡更符合實際應用的需要。FPGA技術的應用日益成熟和廣泛,用FPGA芯片替代分離器件將大大提高測試卡的可靠性。本文論述了基于Altera公司的Acex1K系列芯片(如ACEK1K30QC208等),采用PCI局部總線標準,設計基于PCI的遙測解調及遙控注入測試卡的一些關鍵技術。

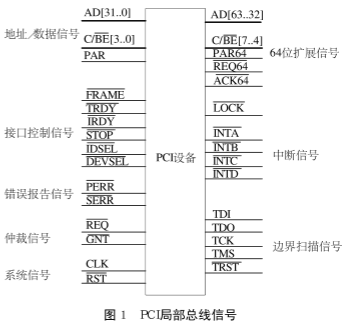

1 PCI局部總線

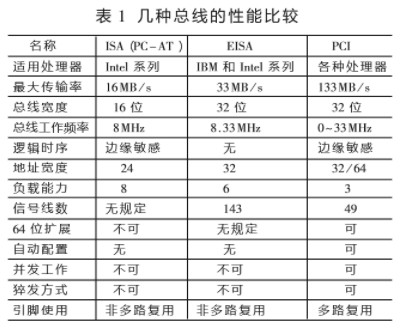

以Intel公司為首的PCI SIG小組推出的PCI總線標準是一種高端現代局部總線,它具有符合工業標準、性能高、成本低、獨立于處理器、允許靈活配置、使用壽命長、可操作性強和軟件兼容性好等優點,因此在嵌入式計算機和工業控制計算機領域具有廣闊的應用前景。PCI總線與傳統ISA總線、現代的EISA總線的性能比較如表1所示。

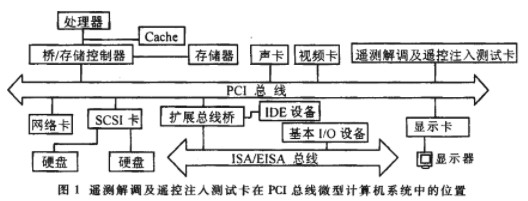

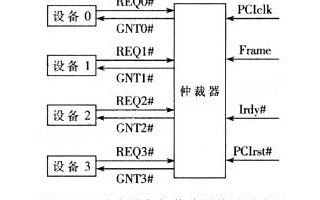

PCI局部總線是微型計算機中處理器/存儲器與外圍控制部件、擴展卡之間的互連接口。PCI總線規范是互連機構的協議及電氣和機械配置的規范,其用途是在高度集成的外設控制器器件、擴展板和處理器之間提供一種內部聯結機制。本文中的基于PCI的遙測解調及遙控注入測試卡是由PCI總線完成測試卡和處理器/存儲器的連接,其在PCI總線微型計算機系統中的位置如圖1所示。

2 FPGA技術

在現代電子系統領域,EDA技術已經逐漸成為電子系統的主要設計手段。FPGA(現場可編程門陣列)是EDA技術中的一種重要應用。FPGA器件在結構上由邏輯功能塊排列為陣列,并由可編程的內部連線連接這些功能塊,來實現一定的邏輯功能。設計遙測解調及遙控注入測試卡的數字和邏輯電路部分均由FPGA器件來完成。

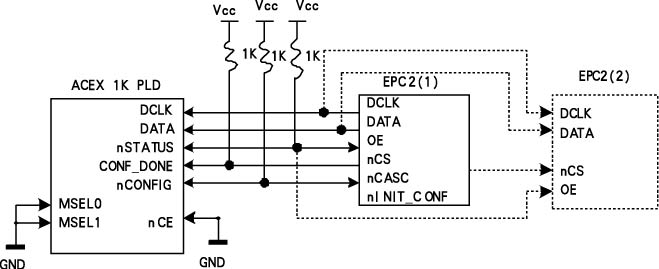

考慮到遙測解調及遙控注入測試卡邏輯功能的需要,本設計采用Altera公司的FPGA芯片ACEK1K50QC208。該芯片具有5萬門可編程邏輯單元,屬于Sram型的FPGA芯片,邏輯信息保存在專門的靜態存儲器中(本設計中使用EPC1PC8芯片作為靜態儲存器),上電時動態加載。這種類型的器件在驗證期間可以使用下載工具將邏輯加載到芯片中,驗證完畢后需要將邏輯信息燒寫在靜態存儲器中,以后系統上電時,FPGA從靜態存儲器中自動加載邏輯。

使用FPGA進行電路設計的步驟為:首先采用目前流行的硬件描述語言Verilog HDL設計輸入,即將設計的邏輯、時序關系輸入計算機;之后,使用Maxplus II軟件進行前仿真、綜合、布局布線和后仿真,即驗證輸入的硬件描述語言的邏輯關系是否正確,若正確則用抽象語言將邏輯描述分解為具體的邏輯單元,在FPGA器件中實現,并驗證布局布線后仿真是否正確;最后,進行硬件驗證,將計算機上布局布線之后生成的文件加載到FPGA中,以驗證它的實際工作情況同設計是否一致。

3 遙測解調及遙控注入測試卡的設計

3.1 測試卡的測試接口信號要求

測試卡要根據測試的需要提供測試接口信號。這些測試接口信號共包括五類:

(1)遙測解調信號:測試卡集成了兩路遙測解調器的功能。其中每一路遙測解調器都能夠輸出幀同步信號、路同步信號和數據時鐘信號。被測系統根據解調器卡輸出的上述三個信號,按照一定的時序關系輸出串行的遙測數據。

(2)遙控數據注入:測試卡集成了兩路遙控數據注入單元。其中每一路遙控數據注入單元都能夠提供數據有效信號、時鐘信號和數據信號。

(3)遙控指令:測試卡提供1套24路直接遙控指令輸出。每路指令處于工作狀態時,集電極開路門接通(低電平);處于非工作狀態時,集電極開路門不接通(高電平)。

(4)觸點信號:測試卡提供1套11路(共22根引腳)觸點輸出信號。每路觸點信號為開關閉合有效,斷開無效。

(5)時鐘輸出:測試卡提供1路40kHz的時鐘輸出信號。

3.2 測試卡硬件系統的實現

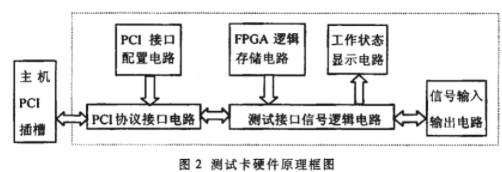

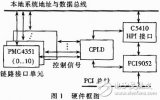

在該測試卡的電路系統中,由FPGA芯片提供測試接口信號并實現軟件接口邏輯設計;由PCI接口芯片實現測試卡同計算機上PCI總線的連接;由分離器件實現測試接口信號的輸入輸出。測試卡的硬件原理框圖如圖2所示。

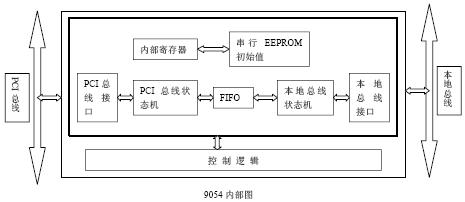

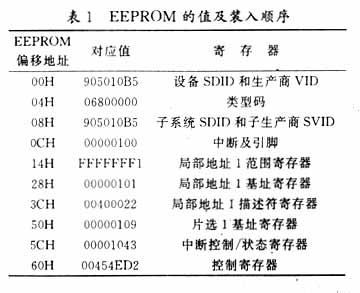

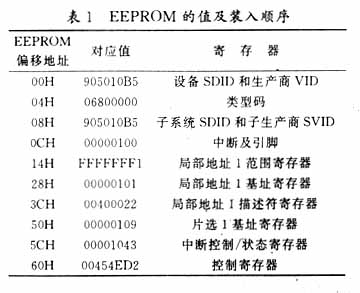

在圖2中,PCI協議接口電路主要是使用PCI總線接口芯片9052來提供高性能的PCI總線接口,其使用需要對它的PCI配置寄存器和本地配置寄存器進行設置。在PCI接口配置電路中,采用93CS46N串行EEROM芯片對9052芯片PCI配置寄存器和本地配置寄存器進行設置。

測試接口信號邏輯電路圍繞FPGA芯片ACEK1K30QC208進行設計。該芯片能夠完成測試卡需要的五類測試信號的邏輯設計,還能實現可供使用人員配置的測試卡軟件接口,以及和PCI總線接口進行信號傳輸的邏輯。ACEK1K30QC208芯片是Sram型的FPGA芯片,還需要專門的邏輯存儲電路來保存上述邏輯信息。邏輯存儲電路使用靜態存儲器芯片EPC1PC8芯片,系統上電時,FPGA從存儲器中自動加載邏輯。

測試信號輸入輸出電路完成測試卡與被測設備的信息交換。對于測試卡提供的五類測試信息,遙控指令和觸電信號需要模擬器件和電子開關進行轉換,而其它信號則可以通過連接器直接輸入輸出。

工作狀態顯示電路提供測試卡的工作狀態,如測試卡是否加電成功、是否邏輯下載成功、是否在進行遙控指令注入、是否在進行遙測數據接收等。工作狀態顯示電路的邏輯也來自于測試接口信號邏輯電路。

3.3 PCI局部總線和測試卡本地總線的連接

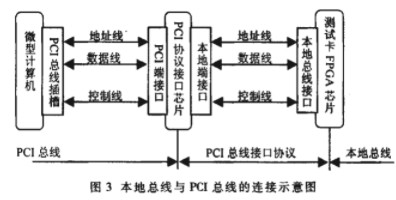

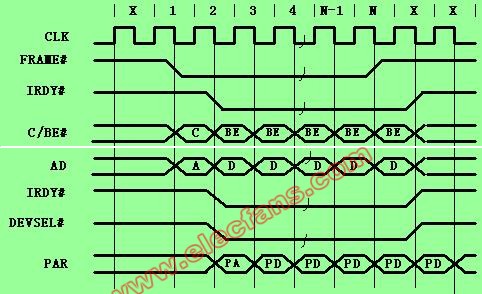

本設計采用了PLX Technology公司的PCI總線協議接口芯片9052來實現PCI 總線和本地總線之間的連接。PCI總線協議接口芯片9052為各類適配卡提供高性能的PCI總線接口,可以將PCI總線同各種傳輸速率低于132Mb/s的本地總線進行連接。采用PCI總線協議接口芯片9052來實現PCI總線和本地總線之間的連接,如圖3所示。

由于9052是專門的PCI協議芯片,所以它的PCI端可以直接通過插卡上的引線和PCI插槽連接。二者連接時不用做任何變換,將二者的復用數據線和地址線直接連通,將9052的PCI端的控制線與PCI插槽上的作為從設備的控制線直接連通即可。

9052芯片本地端接口和FPGA芯片的連接也就是PCI總線接口和測試卡本地總線的連接,是本接口卡設計的一個關鍵。在FPGA芯片的邏輯設計中,根據測試卡對主機系統資源的需求,提供了一個測試卡本地總線接口。本地總線接口包括4K字節的存儲器和16字節的寄存器,所以將要使用9052芯片的兩個地址空間分別設置為4K字節和16字節,將存儲器和寄存器空間分開。在地址線和數據線的設計上,采用地址線和數據線非復用模式,本地的地址線和數據線分別與9052本地端的地址線和數據線連接。在控制線的設計上,根據二者的讀寫時序,將9052芯片設置為直接讀寫的方式,用9052芯片的讀信號和寫信號直接驅動本地總線的讀寫信號。另外還要使用9052芯片提供的一個片選信號,來選擇不同的16個字節的寄存器地址空間。9052本地端和BU-61580要采用同一個時鐘信號,以保證二者讀寫時序的同步。

3.4 測試卡軟件接口的設計

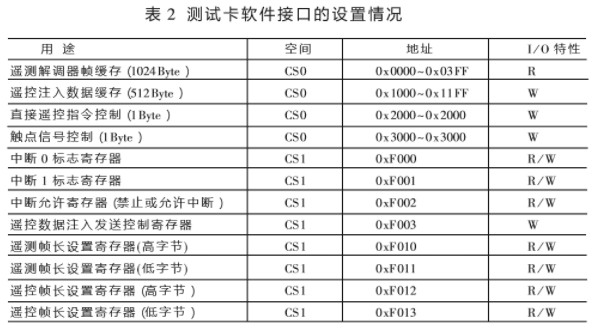

測試用戶需要對測試卡進行軟件設置,來實現遙控注入數據、遙測和遙控幀長、遙控數據發送等。這些軟件接口是通過FPGA芯片進行邏輯設計來提供的。測試卡加電后,這些軟件接口就存在于測試卡上,通過軟件編程可以控制軟件接口,來實現測試卡的測試工作。測試卡實現的軟件接口如表2所示。

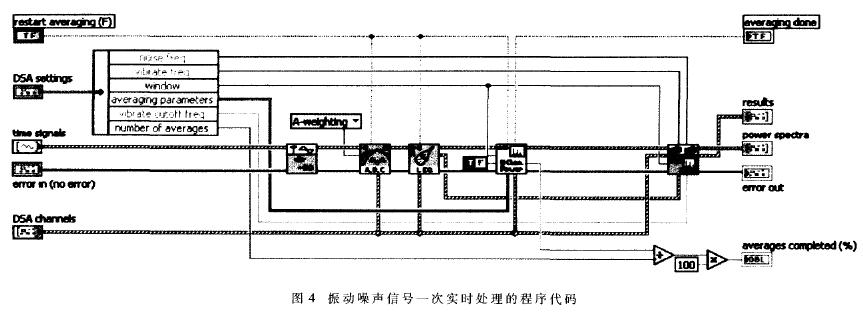

4 測試卡與其配套軟件的數據流和控制流

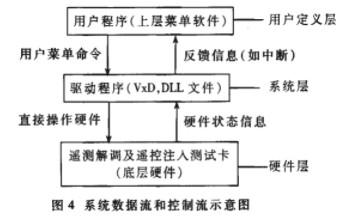

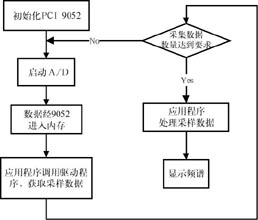

遙測解調及遙控注入測試卡要和其配套的軟件接口卡驅動程序(VxD)及用戶菜單應用軟件共同使用。遙測解調及遙控注入測試卡作為硬件BIU同被測測控系統連接,負責接收與發送各類測試數據,并且可以由主機來配置測試卡上的寄存器。驅動程序則作為遙測解調及遙控注入測試卡和用戶菜單軟件的接口程序,負責接收菜單軟件的命令,并依據此命令來操作硬件,或者向菜單軟件報告總線適配器的工作情況(如通知中斷已經產生以及告知中斷原因),包括安裝信息文件(INF)、虛擬設備驅動程序(VxD)、接口函數文件(DLL)三個組成部分。菜單軟件作為用戶界面程序接收用戶的輸入,并以可視的方式將結果數據反饋。遙測解調及遙控注入測試卡與處理器之間所構成系統的數據流和控制流如圖4所示。

責任編輯:gt

電子發燒友App

電子發燒友App

評論