1 ISP技術

在系統編程(In-System-Programming,ISP)技術是美國Lattice半導體公司首先提出來的一種能在產品設計、制造過程中的每個環節具有對其器件、電路或整個數字系統的邏輯和功能隨時進行組態或重組能力的最新技術。在可編程邏輯器件(Programming Logic Device,PLD)及其技術中,ISP是一種新的概念、新的標準。傳統的編程技術是將PLD器件插在編程器上編程的,ISP技術則可不用編程器,直接在用戶自己設計的目標系統中或線路板上對PLD器件編程。常規PLD在使用中通常是先編程后裝備,而采用ISP技術的PLD則是先裝備后編程,成為產品后還可反復編程。ISP硬件靈活且易于軟件修改,便于設計升級。

2 ISP器件的編程軟件

ispEXPERT是由Lattice公司提供的一種通用電子設計軟件。他支持ABEL-HDL語言、VHDL語言、原理圖3種電子設計方式,以及這些設計方式的混合使用。他能對所設計的數字系統進行功能模擬和時序模擬,能對設計進行邏輯優化,并將邏輯映射到器件中去,自動完成預布線,生成編程所需的熔絲圖文件,通過下載電纜下載到器件中。

ispEXPERT中的項目導航器引導設計一步步進行,最終生成器件編程所需的JEDEC文件,并下載到ISP器件中。項目導航器是一個很好的設計工具,便于用戶跟蹤軟件的運行流程。

用ispEXPERT對可編程器件進行設計,除了確定設計思想等準備工作外,大部分工作是在計算機上進行的。整個工作流程分為創建新沒計項目、選擇器件、輸入源文件或原理圖、編譯與優化、邏輯模擬、連接和器件適配等過程。這些過程是在項目導航器引導下進行的。

3 ISP在數字電路課程設計中的舉例

目前的數字電路課程設計多為用中小規模集成電路和GAL芯片的方法實現。在設計較大規模的數字系統時,由于電路板的限制,過多的集成塊使學生花費很多時間都無法調試成功,影響學生的積極性。為此,把ISP器件引入數字電路課程設計,選取了一些有代表性的課題,如多功能電子鐘、密碼鎖、交通燈、數字頻率計等,讓學生設計實踐,取得了很好的效果。

下面舉例用ISP對電子鐘進行開發設計。

3.1 設計要求

該設計用ispEXPERT軟件在ISP1016芯片上實現電子鐘的。電子鐘具有下述功能:

(1)用實驗臺上的6個數碼管顯示時、分、秒。

(2)能使電子鐘復位(清零)。

(3)能啟動或停止電子鐘運行。

(4)在電子鐘停止運行狀態下,能夠修改時、分、秒的值。

(5)具有報時功能,整點時喇叭鳴叫。

3.2 功能分析

電子鐘工作時的最高頻率是秒針的1 Hz,而實驗設備所提供的連續脈沖的最低頻率為1 kHz,因而需要一個分頻模塊,這可通過設計一個模為1 000的計數器設計。

電子鐘的秒針是每來一個脈沖計數一次,分針是每過60 s計數一次,時針是每過60 min計數一次,秒針和分針由0計到59又回到0,而時針由0 計到23又回到0。這樣需要設計2個模為60的計數器和一個模為24的計數器,例化成秒針模塊、分針模塊和時針模塊。

秒針、分針和時針的計數信號要轉換成BCD碼后輸出,這可以通過在上述各模塊內增加一個由二進制碼轉換為BCD碼的編碼轉換單元實現。

要求能啟動或停止電子鐘運行,且能在電子鐘停止運行狀態下修改時、分、秒的值,可增加一個啟動/停止控制端實現。如啟動/停止控制端接低電平,分頻模塊的時鐘接1 kHz的連續脈沖,其他模塊分別接對應輸出,電子鐘便啟動。而當啟動/停止控制端接高電平,分頻模塊的時鐘接地,其他模塊的時鐘分別接3個單脈沖手動輸入,電子鐘停止運行,手動產生一個單脈沖,與其相連的模塊就計數一次,達到了修改時、分、秒的目的,即實現了電子鐘更改時間的功能。

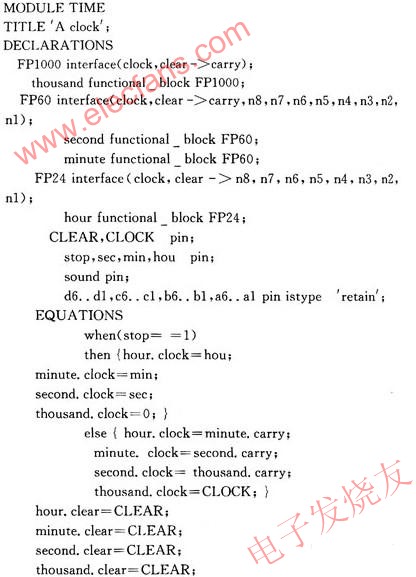

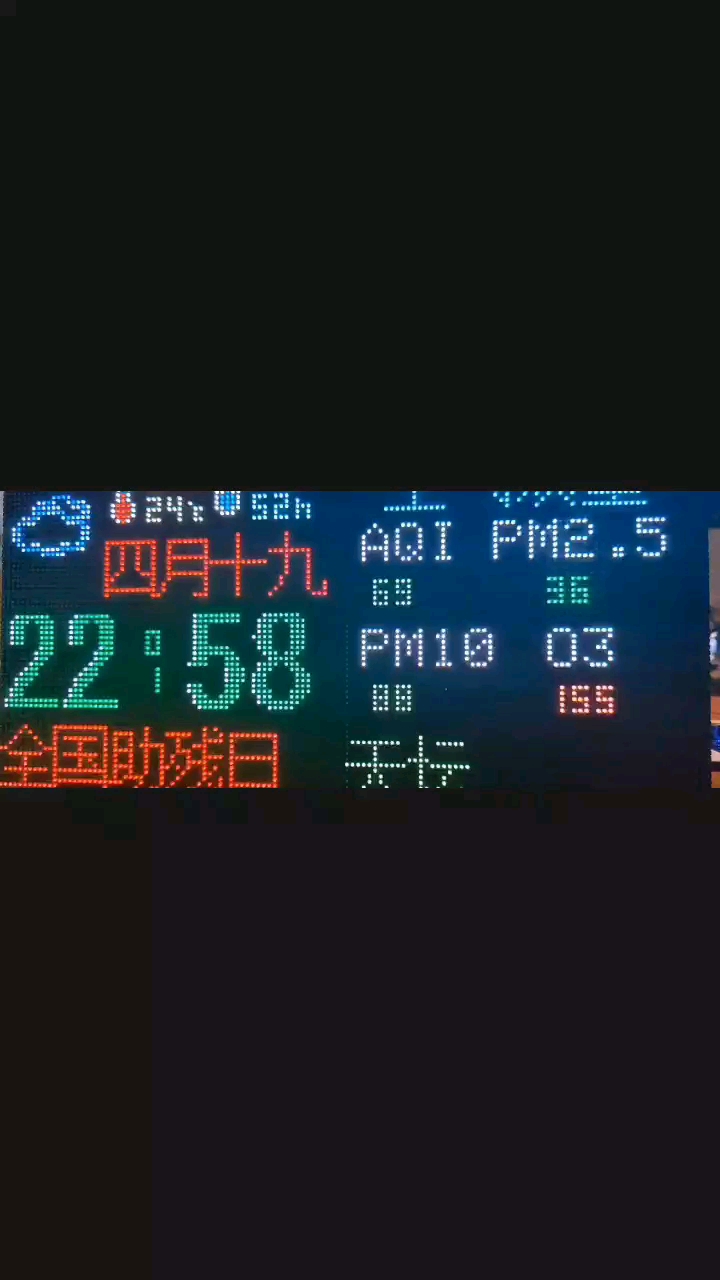

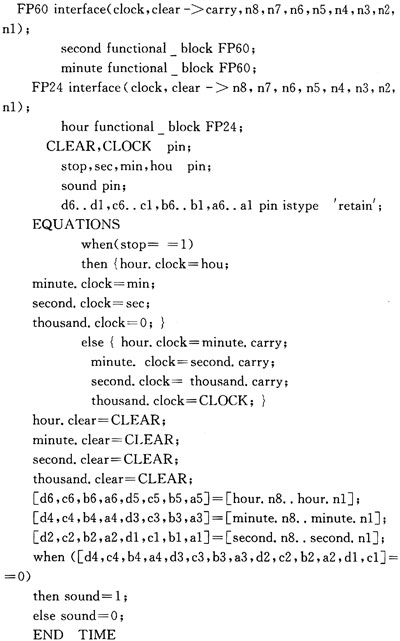

3.3 ABEL語言描述

下面用ABEL語言的層次結構實現電子鐘的設計可分為頂層模塊Clock,3個底層模塊FP1000,FP60和FP24。下面介紹頂層模塊CLOCK,其中調用了3個底層模塊。

4 結 語

從上例可知,用ISP器件可進行各種數字電路實驗,代替了古老的面模板實驗,而且靈活方便,是一種較理想的數字電路課程設計方法,值得推廣應用。

電子發燒友App

電子發燒友App

評論