architecture behavioral of laohu is

signal count0:integer range 0 to 31;--change

signal clk2:std_logic;

begin p1:process(clk) --對12mhz系統時鐘進行3m的分頻,得到4hz的信號clk2

variable count:integer range 0 to 3000000;

begin if clk‘event and clk=’1‘ then

count:=count+1;

if count=1500000 then

clk2<=’1‘;

elsif count=3000000 then

clk2<=’0‘;

count:=0;

end if;

end if;

end process p1;

p2:process(clk2)--此進程完成自動演奏部分樂曲的地址累加

begin if clk2’event and clk2=‘1’ then

if count0=29 then

count0<=0;

else count0<=count0+1;

end if;

end if;

end process p2;

p3:process(count0,tone_key_0)

begin

case count0 is--此case語句:存儲自動演奏部分的樂曲

when 0 => tone_key_0<=b“00000001_00000000”; --1

when 1 => tone_key_0<=b“00000010_00000000”; --2

when 2 => tone_key_0<=b“00000100_00000000”; --3

when 3 => tone_key_0<=b“00000001_00000000”; --1

when 4 => tone_key_0<=b“00000001_00000000”; --1

when 5 => tone_key_0<=b“00000010_00000000”; --2

when 6 => tone_key_0<=b“00000100_00000000”; --3

when 7 => tone_key_0<=b“00000001_00000000”; --1

when 8 => tone_key_0<=b“00000100_00000000”; --3

when 9 => tone_key_0<=b“00001000_00000000”; --4

when 10 => tone_key_0<=b“00010000_00000000”; --5

when 11 => tone_key_0<=b“00000100_00000000”; --3

when 12 => tone_key_0<=b“00001000_00000000”; --4

when 13 => tone_key_0<=b“00010000_00000000”; --5

when 14 => tone_key_0<=b“00010000_00000000”; --5

when 15 => tone_key_0<=b“00100000_00000000”; --6

when 16 => tone_key_0<=b“00010000_00000000”; --5

when 17 => tone_key_0<=b“00001000_00000000”; --4

when 18 => tone_key_0<=b“00000100_00000000”; --3

when 19 => tone_key_0<=b“00000001_00000000”; --1

when 20 => tone_key_0<=b“00010000_00000000”; --5

when 21 => tone_key_0<=b“00100000_00000000”; --6

when 22 => tone_key_0<=b“00010000_00000000”; --5

when 23 => tone_key_0<=b“00001000_00000000”; --4

when 24 => tone_key_0<=b“00000100_00000000”; --3

when 25 => tone_key_0<=b“00000001_00000000”; --1

when 26 => tone_key_0<=b“00000100_00000000”; --3

when 27 => tone_key_0<=b“00000000_00100000”; --di6

when 28 => tone_key_0<=b“00000001_00000000”; --1

when others => null;

end case;

end process p3;

end behavioral;

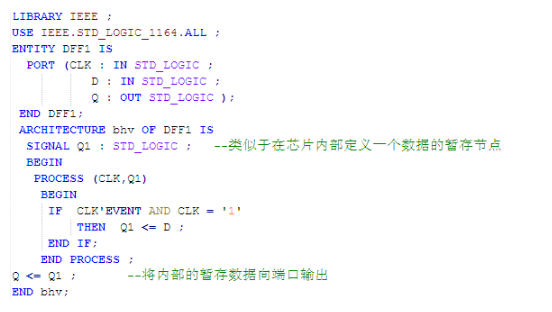

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity beep0 is

port( clk:in std_logic; device:out std_logic );

end beep0;

architecture behavioral of beep0 is

component laohu is port( clk: in std_logic;--系統時鐘;鍵盤輸入/自動演奏

tone_key_0: out std_logic_vector(15 downto 0)--音符信號輸出 );

end component;

component tone is

port( index: in std_logic_vector(15 downto 0);--音符輸入信號

tone0: out integer range 0 to 2047--音符的分頻系數 );

end component;

component speaker is

port(

clk1: in std_logic;--系統時鐘12mhz

tone1: in integer range 0 to 2047; --音符分頻系數

spks: out std_logic--驅動揚聲器的音頻信號 );

end component;

signal mid:std_logic_vector(15 downto 0);

signal tones:integer;

begin

u0:laohu port map(clk,mid);

u1:tone port map(mid,tones);

u2:speaker port map(clk,tones,device);

end behavioral;

電子發燒友App

電子發燒友App

評論