實(shí)驗(yàn)五? 數(shù)字鎖相環(huán)與位同步

一、?實(shí)驗(yàn)?zāi)康?/font>

??? 1. 掌握數(shù)字鎖相環(huán)工作原理以及觸發(fā)式數(shù)字鎖相環(huán)的快速捕獲原理。

??? 2. 掌握用數(shù)字環(huán)提取位同步信號(hào)的原理及對(duì)信息代碼的要求。

3. 掌握位同步器的同步建立時(shí)間、同步保持時(shí)間、位同步信號(hào)同步抖動(dòng)等概念。

二、?實(shí)驗(yàn)內(nèi)容

??? 1. 觀察數(shù)字環(huán)的失鎖狀態(tài)、鎖定狀態(tài)。

??? 2. 觀察數(shù)字環(huán)鎖定狀態(tài)下位同步信號(hào)的相位抖動(dòng)現(xiàn)象及相位抖動(dòng)大小與固有頻差、信息代碼的關(guān)系。

3. 觀察數(shù)字環(huán)位同步器的同步保持時(shí)間與固有頻差之間的關(guān)系。

三、?基本原理

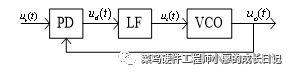

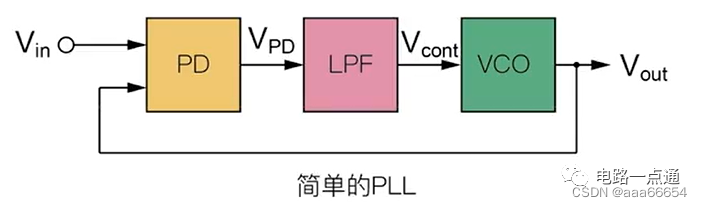

??? 可用窄帶帶通濾波器,鎖相環(huán)來提取位同步信號(hào)。實(shí)驗(yàn)一中用模數(shù)混合鎖相環(huán)(電荷泵鎖相環(huán))提取位同步信號(hào),它要求輸入信號(hào)是一個(gè)準(zhǔn)周期數(shù)字信號(hào)。實(shí)驗(yàn)三中的模擬環(huán)也可以提取位同步信號(hào),它要求輸入準(zhǔn)周期正弦信號(hào)。本實(shí)驗(yàn)使用數(shù)字鎖相環(huán)提取位同步信號(hào),它不要求輸入信號(hào)一定是周期信號(hào)或準(zhǔn)周期信號(hào),其工作頻率低于模數(shù)環(huán)和模擬環(huán)。

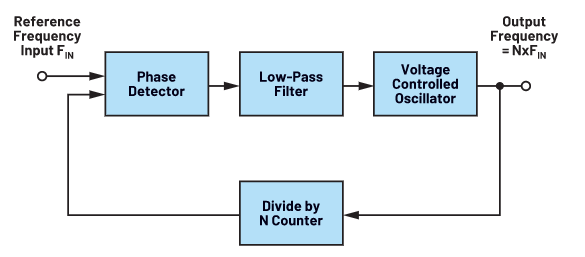

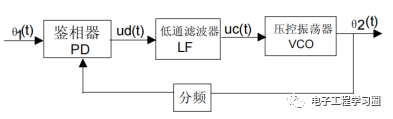

用于提取位同步信號(hào)的數(shù)字環(huán)有超前滯后型數(shù)字環(huán)和觸發(fā)器型數(shù)字環(huán),此實(shí)驗(yàn)系統(tǒng)中的位同步提取模塊用的是觸發(fā)器型數(shù)字環(huán),它具有捕捉時(shí)間短、抗噪能力強(qiáng)等特點(diǎn)。位同步模塊原理框圖如圖5-1所示,電原理圖如圖5-2所示(見附錄)。其內(nèi)部僅使用+5V電壓。

圖5-1? 位同步器方框圖

位同步模塊有以下測(cè)試點(diǎn)及輸入輸出點(diǎn):

??? ? S-IN?????基帶信號(hào)輸入點(diǎn)/測(cè)試點(diǎn)(2個(gè))

? BS-OUT?????位同步信號(hào)輸出點(diǎn)/測(cè)試點(diǎn)(3個(gè))

??? 圖5-1中各單元與電路板上元器件的對(duì)應(yīng)關(guān)系如下:

??? ? 晶振?????CRY3:晶體;U39:7404

??? ? 控制器?????U48:或門7432;U41:計(jì)數(shù)器74190

??? ? 鑒相器?????U40:D觸發(fā)器7474

??? ? 量化器?????U45:可編程計(jì)數(shù)器8254

??? ? 數(shù)字環(huán)路濾波器???由軟件完成

??? ? 數(shù)控振蕩????U46、U45:8254

??? ? 脈沖展寬器????U47:單穩(wěn)態(tài)觸發(fā)器74123

??? 位同步器由控制器、數(shù)字鎖相環(huán)及脈沖展寬器組成,數(shù)字鎖相環(huán)包括數(shù)字鑒相器、量化器、數(shù)字環(huán)路濾波器、數(shù)控振蕩器等單元。

??? 下面介紹位同步器的工作原理。

??? 數(shù)字鎖相環(huán)是一個(gè)單片機(jī)系統(tǒng),主要器件是單片機(jī)89C51及可編程計(jì)數(shù)器8254。環(huán)路中使用了兩片8254,共六個(gè)計(jì)數(shù)器,分別表示為8254A0、8254A1、8254A2、8254B0、8254B1、8254B2。它們分別工作在M0、M1、M2三種工作模式。M0為計(jì)數(shù)中斷方式,M1為單穩(wěn)方式,M2為分頻方式。除地址線、數(shù)據(jù)線外,每個(gè)8254芯片還有時(shí)鐘輸入端C、門控信號(hào)輸入端G和輸出端O。

數(shù)字鑒相器電原理圖及波形圖如圖5-3(a)、圖5-3(b)所示。輸出信號(hào)寬度正比于信號(hào)ui及uo上升沿之間的相位差,最大值為ui的碼元寬度。稱此鑒相器為觸發(fā)器型鑒相器,稱包含有觸發(fā)器型鑒相器的數(shù)字環(huán)路為觸發(fā)器型數(shù)字鎖相環(huán)。

圖5-3? 數(shù)字鑒相器

量化器把相位誤差變?yōu)槎噙M(jìn)制數(shù)字信號(hào),它由工作于M0方式、計(jì)數(shù)常數(shù)為N0的8254 B2完成(N0為量化級(jí)數(shù),此處N0=52)。ud作為8254B2的門控信號(hào),ud為高電平時(shí)8254B2進(jìn)行減計(jì)數(shù),ud為低電平時(shí)禁止計(jì)數(shù),計(jì)數(shù)結(jié)束后從8254B2讀得的數(shù)字為

Nd= N0-N’d

式中N’d為ud脈沖寬度的量化值(下面用量化值表示脈沖寬度和時(shí)間間隔),N0≥N’d,讀數(shù)結(jié)束后再給8254B2寫入計(jì)數(shù)常數(shù)N0。讀數(shù)時(shí)刻由8254A2控制,它工作在M1模式,計(jì)數(shù)常數(shù)為N0,ui作為門控信號(hào)。一個(gè)ui脈沖使8254A2產(chǎn)生一個(gè)寬度為N0的負(fù)脈沖,倒相后變?yōu)檎}沖送到89C51的 端,而89C51的外中斷1被設(shè)置為負(fù)跳變中斷申請(qǐng)方式。由于8254A2產(chǎn)生的脈沖寬度不小于ud脈沖寬度且它們的前沿處于同一時(shí)刻,所以可以確保中斷申請(qǐng)后對(duì)8254B2讀數(shù)時(shí)它已停止計(jì)數(shù)。

??? 數(shù)字環(huán)路濾波器由軟件完成。可采用許多種軟件算法,一種簡單有效的方法是對(duì)一組N0作平均處理。設(shè)無噪聲時(shí)環(huán)路鎖定后ui與uo的相位差為N0/2,則在噪聲的作用下,鎖定時(shí)的相位誤差可能大于N0/2也可能小于N0/2。這兩種情況出現(xiàn)的概率相同,所以平均處理可以減小噪聲的影響,m個(gè)Nd值的平均值為

????????(5-2)

數(shù)字濾波器的輸出為

??????????????????????? Nc = No / 2 + Nd????????(5-3)

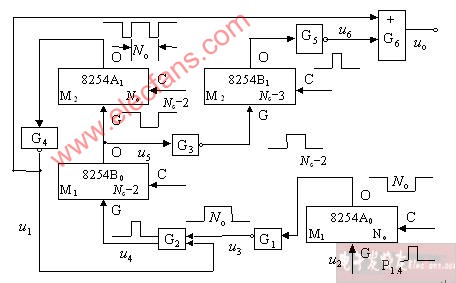

數(shù)控振蕩器由四個(gè)8254計(jì)數(shù)器及一些門電路構(gòu)成,其原理框圖如圖5-4所示,圖中已注明了各個(gè)計(jì)數(shù)器的工作方式和計(jì)數(shù)常數(shù)。

??? 以下分析環(huán)路的鎖定狀態(tài)及捕捉過程,此時(shí)不考慮噪聲的影響。

圖5-4? 數(shù)控振蕩器

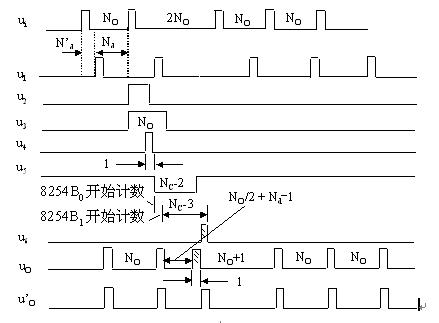

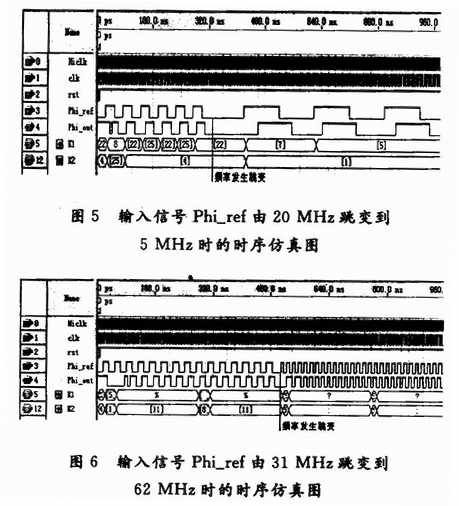

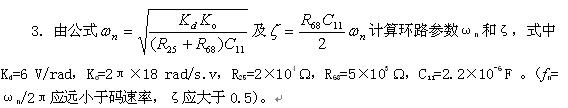

??? 環(huán)路開始工作時(shí),軟件使8254B0和8254B1輸出高電平,從而使8254A1處于計(jì)數(shù)工作狀態(tài)、8254B1處于停止計(jì)數(shù)狀態(tài),G6處于開啟狀態(tài),8254A1輸出一個(gè)周期為N0的周期信號(hào)。若環(huán)路處于鎖定狀態(tài),則N’d=N0/2,由式(5-1)及式(5-2)得Nd=N0/2。此時(shí)89c51的P1.4口不輸出觸發(fā)脈沖,8254A0輸出端仍保持初始化時(shí)的高電平,從而使8254B0的門控端G保持低電平、輸出端O保持高電平。這樣可保持8254A1、8254B1的工作狀態(tài)不變、環(huán)路仍處于鎖定狀態(tài)。若環(huán)路失鎖,則N’d≠N0/2,Nd≠N0/2,P1.4口輸出一個(gè)正脈沖u2,在u2作用下,8254A0輸出一個(gè)寬度為N0的負(fù)脈沖,倒相后變?yōu)檎}沖u3送給與門G2。G2的另一個(gè)輸入信號(hào)u1來自8254A1。在G1輸出的寬度為N 0的正脈沖持續(xù)時(shí)間內(nèi),8254A1一定有(也只有)一個(gè)負(fù)脈沖信號(hào)輸入,此負(fù)脈沖經(jīng)G4倒相后與G1輸出的正脈沖相與后給8254B0的G端送一個(gè)觸發(fā)信號(hào)u4。在u4的作用下,8254B0輸出一個(gè)寬度為N0-2的負(fù)脈沖。在這段時(shí)間內(nèi),8254A1停止計(jì)數(shù)工作,8254B1進(jìn)行減計(jì)數(shù)且在此時(shí)間內(nèi)的最后一個(gè)時(shí)鐘周期輸出一個(gè)負(fù)脈沖。8254B0輸出的負(fù)脈沖的后沿重新啟動(dòng)8254A1,使它重新作÷N0分頻。設(shè)m=1,上述過程的有關(guān)波形如圖5-5所示,圖中u?O為環(huán)路鎖定狀態(tài)下數(shù)控振蕩器的輸出信號(hào)。由圖5-5可見,不管失鎖時(shí)相位誤差多少(不會(huì)大于N0),只要對(duì)數(shù)控振蕩器作一次調(diào)整,就可使環(huán)路進(jìn)入鎖定狀態(tài),從而實(shí)現(xiàn)快速捕捉。

??? 程序流程如圖5-6所示,輸入信號(hào)ui使IE1置“1”,且使8254B2計(jì)數(shù),對(duì)IE1進(jìn)行位操作時(shí)又使之置“0”。由于量化誤差,故當(dāng)Nd為N0/2,N0/2+1或N0/2-1時(shí),環(huán)路皆處于鎖定狀態(tài),不對(duì)數(shù)控振蕩器進(jìn)行調(diào)整。程序中令m=16,進(jìn)行16次鑒相后做一次平均運(yùn)算,若發(fā)現(xiàn)環(huán)路失鎖,則對(duì)數(shù)控振蕩器進(jìn)行一次調(diào)整。

??? 控制器的作用是保證每次對(duì)8254B2進(jìn)行讀操作之前鑒相器只輸出一個(gè)正脈沖,它由或門7432(U5:B)及16分頻器74190(U13)組成。

圖5-5? 捕獲過程波形

??? 當(dāng)數(shù)字環(huán)輸入信號(hào)的碼速率與數(shù)控振蕩器的固有頻率完全相同時(shí),環(huán)路鎖定后輸入信號(hào)與反饋信號(hào)(即位同步信號(hào))的相位關(guān)系是固定的且符合抽樣判決器的要求(當(dāng)然開環(huán)時(shí)它們的相位誤差也是固定的,但不符合抽樣判決器的要求)。輸入信號(hào)碼速率決定于發(fā)送端的時(shí)鐘頻率,數(shù)控振蕩器固有頻率決定于位同步器的時(shí)鐘頻率和數(shù)控振蕩器固有分頻比。由于時(shí)鐘信號(hào)頻率穩(wěn)定度是有限的,故這兩個(gè)時(shí)鐘信號(hào)的頻率不可能完全相同,因此鎖相環(huán)輸入信號(hào)碼速率與數(shù)控振蕩器固有頻率不可能完全相等(即環(huán)路固有頻差不為0)。數(shù)字環(huán)位同步器是一個(gè)離散同步器,只有當(dāng)輸入信號(hào)的電平發(fā)生跳變時(shí)才可能對(duì)輸入信號(hào)的相位和反饋信號(hào)的相位進(jìn)行比較從而調(diào)整反饋信號(hào)的相位,在兩次相位調(diào)整的時(shí)間間隔內(nèi),反饋信號(hào)的相位相對(duì)于輸入信號(hào)的相位是變化的,即數(shù)字環(huán)位同步器提取的位同步信號(hào)的相位是抖動(dòng)的,即使輸入信號(hào)無噪聲也是如此。

圖5-6? 鎖相環(huán)程序流程

??? 顯然,收發(fā)時(shí)鐘頻率穩(wěn)定度越高,數(shù)字環(huán)的固有頻差就越小,提取的位同步信號(hào)的相位抖動(dòng)范圍越小。反之,對(duì)同步信號(hào)的相位抖動(dòng)要求越嚴(yán)格,則收發(fā)時(shí)鐘的頻率穩(wěn)定度也應(yīng)越高。

??? 位同步信號(hào)抖動(dòng)范圍還與數(shù)字位同步器輸入信號(hào)的連“1”或“0”個(gè)數(shù)有關(guān),連“1”或“0”個(gè)數(shù)越多,兩次相位調(diào)整之間的時(shí)間間隔越長,位同步信號(hào)的相位抖動(dòng)越大。

??? 對(duì)于NRZ碼來說,允許其連“1”、連“0”的個(gè)數(shù)決定于數(shù)字環(huán)的同步保持時(shí)間tc。tc與收發(fā)時(shí)鐘頻率穩(wěn)定度?、碼速率RB、允許的同步誤差最大值 的關(guān)系為:

tC =η/(2RBε)

tC的定義是:位同步器輸入信號(hào)斷開后,收發(fā)位同步信號(hào)相位誤差不超過 的時(shí)間。

關(guān)于數(shù)字環(huán)位同步器的工作原理,可參考文獻(xiàn)[3]、[4]、[5]。

用模擬環(huán)位同步器或模數(shù)環(huán)位同步器提取的位同步信號(hào)的相位抖動(dòng)與固有頻差無關(guān),但隨信息碼連“1”、連“0”的個(gè)數(shù)增多而增大。

四、?實(shí)驗(yàn)步驟

??? 本實(shí)驗(yàn)使用數(shù)字信源單元和位同步單元。

??? 1、熟悉位同步單元工作原理。將數(shù)字信源單元的NRZ-OUT連接到位同步單元的S-IN點(diǎn),接通實(shí)驗(yàn)箱電源。調(diào)整信源模塊的K1、K2、K3開關(guān),使NRZ-OUT的連“0”和連“1”個(gè)數(shù)較少。

??? 2、觀察數(shù)字環(huán)的鎖定狀態(tài)和失鎖狀態(tài)。

將示波器的兩個(gè)探頭分別接數(shù)字信源單元的NRZ-OUT和位同步單元的BS-OUT,調(diào)節(jié)位同步單元上的可變電容C2,觀察數(shù)字環(huán)的鎖定狀態(tài)和失鎖狀態(tài)。鎖定時(shí)BS-OUT信號(hào)上升沿位于NRZ-OUT信號(hào)的碼元中間且在很小范圍內(nèi)抖動(dòng);失鎖時(shí),BS-OUT的相位抖動(dòng)很大,可能超出一個(gè)碼元寬度范圍,變得模糊混亂。

??? 3、觀察位同步信號(hào)抖動(dòng)范圍與位同步器輸入信號(hào)連“1”或連“0”個(gè)數(shù)的關(guān)系。

調(diào)節(jié)可變電容使環(huán)路鎖定且BS-OUT信號(hào)相位抖動(dòng)范圍最小(即固有頻差最小),增大NRZ-OUT信號(hào)的連“0”或連“1”個(gè)數(shù),觀察BS-OUT信號(hào)的相位抖動(dòng)變化情況。

??? 4、觀察位同步器的快速捕捉現(xiàn)象、位同步信號(hào)相位抖動(dòng)大小及同步保持時(shí)間與環(huán)路固有頻差的關(guān)系。

??? 先使BS-OUT信號(hào)的相位抖動(dòng)最小,按一下復(fù)位鍵,觀察NRZ-OUT與BS-OUT信號(hào)的之間的相位關(guān)系變化快慢情況,再按一下復(fù)位鍵,觀察快速捕捉現(xiàn)象(位同步信號(hào)BS-OUT的相位一步調(diào)整到位)。再微調(diào)位同步單元上的可變電容(即增大固有頻差)當(dāng)BS-OUT相位抖動(dòng)增大時(shí)按一下復(fù)位鍵,觀察NRZ-OUT信號(hào)與BS-OUT信號(hào)的相位關(guān)變化快慢情況并與固有頻差最小時(shí)進(jìn)行定性比較。

五、?實(shí)驗(yàn)報(bào)告要求

??? 1、數(shù)字環(huán)位同步器輸入NRZ碼連“1”或連“0”個(gè)數(shù)增加時(shí),提取的位同步信號(hào)相位抖動(dòng)增大,試解釋此現(xiàn)象。

??? 2、設(shè)數(shù)字環(huán)固有頻差為Δf,允許同步信號(hào)相位抖動(dòng)范圍為碼元寬度TS的η倍,求同步保持時(shí)間tC及允許輸入的NRZ碼的連“1”或“0”個(gè)數(shù)最大值。

??? 3、數(shù)字環(huán)同步器的同步抖動(dòng)范圍隨固有頻差增大而增大,試解釋此現(xiàn)象。

4、若將AMI碼或HDB3碼整流后作為數(shù)字環(huán)位同步器的輸入信號(hào),能否提取出位同步信號(hào)?為什么?對(duì)這兩種碼的信息代碼中連“1”個(gè)數(shù)有無限制?對(duì)AMI碼的信息代碼中連“0”個(gè)數(shù)有無限制?對(duì)HDB3碼的信息代碼中連“0”個(gè)數(shù)有無限制?為什么?

5、試提出一種新的環(huán)路濾波器算法,使環(huán)路具有更好的抗噪能力。

6、試解釋本實(shí)驗(yàn)使用的數(shù)字鎖相環(huán)快速捕捉機(jī)理,并與超前滯后型數(shù)字環(huán)進(jìn)行比較。

更多鎖相環(huán)知識(shí)請(qǐng)?jiān)L問 http://www.xsypw.cn/zhuanti/PLL.html

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論