1. 背景

時鐘電路是芯片中最基礎的電路,時鐘電路性能的好壞關乎SoC中所有電路能否達到預期目標,例如:計算核(CPU/GPU/NPU)的主頻,DDR的帶寬,高速接口(PCIE)的帶寬等。對于時鐘電路,其最關鍵的性能指標就是jitter,jitter會影響數字電路的頻率,影響SerDes的誤碼率。因此,在設計初期合理的考慮各個模塊的時鐘jitter尤為重要。

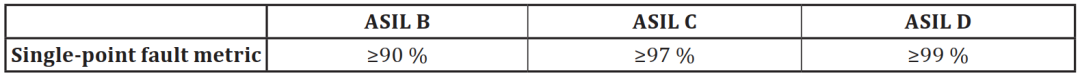

對于汽車芯片,由于其需要具備安全機制檢測故障的能力,因此對jitter有更高的要求。ISO26262中做了明確的汽車安全完整性等級(ASIL)規定,由低到高分別為ASIL A、ASIL B、ASIL C和ASIL D四個級別,對應的單點故障率如Table 1所示。

Table 1. Possible source for the derivation of the target “single-point fault metric” value

同時,由于座艙芯片和ADS芯片對算力需求越來越大,進而導致芯片面積和功耗也越來越大。大面積和高功耗對芯片的時鐘設計帶來巨大挑戰:長距離的時鐘路徑和電源噪聲會使得時鐘jitter發生顯著惡化,使得整芯片性能發生惡化。因此,分析出各種jitter對芯片性能的影響進而對芯片進行精細化設計尤為重要。

對于真實物理世界的時鐘源,包括PLL、DLL、晶振、甚至是函數發生器,它們的時鐘輸出周期都不可能是一個單點的固定值。所有的真實時鐘源的輸出周期都是隨時間而變化的,即同一個時鐘,它的此刻時鐘周期的邊沿與它下一個時鐘周期的邊沿都是會發生變化的。這種時鐘周期的變化稱為jitter。

本文詳細描述了一些關于jitter的關鍵術語和參數,它可以幫助我們深入的理解時鐘最重要的參數,從而根據不同的應用場景合理的選擇PLL和設計對應的時鐘電路。

2. 應用分析

不同的應用對jitter的需求是不同的。

2.1 數字系統

在數字系統中,時鐘定義了電路可以完成一定工作量的時間段。由于每個基本單元的工作都需要一段時間(例如邏輯門的固有延遲、高低電平轉換的延遲和線延遲等)來完成,因此數字系統的時鐘頻率主要是受邏輯復雜度以及組合電路的邏輯深度限制的。

在數字系統中,時鐘邊沿決定了每個基本單元的開始和結束時間。當jitter改變了時鐘邊沿從而導致時鐘周期變短時,每個基本單元的有效工作時間也會變短。

Period jitter是用來衡量單個時鐘周期變化的指標,它也是描述每個基本單元可用時間的最佳指標。這個指標是數字系統的設計人員最應該密切關注的指標。

2.2 RF系統

RF系統的本振時鐘是通常用于混頻器中,用于生產發射信號或者下變頻的接收信號以進行后續處理。

在這種場景下,accumulated jitter(也叫long-term jitter)可以用來衡量系統中的相位噪聲。當混頻器工作時,源信號會乘以本振時鐘來進行上變頻或下變頻,得到目標信號的頻譜為源信號頻譜與本振時鐘頻譜的乘積。本振時鐘中的任何相位噪聲都會在輸出端產生不想要的信號并混在目標信號中,從而降低系統的信噪比(SNR)。

在模數轉換器(ADC)和數模轉換器(DAC)中,時鐘決定了信號采樣時間。如果jitter導致采樣時間偏離了理想采樣時間,這就會導致采樣到的信號值相比于理想的信號值發生變化。

ADC和DAC對信號的采樣的可以轉換為信號與時鐘乘積的模型。這就意味著該系統信噪比(SNR)的退化模型與2.2節描述的場景相同,因此對于ADC和DAC來說,accumulated jitter依然是最重要的參數。

2.4 SerDes系統

當使用Serdes發送或者接收串行bit流時,時鐘是用于對傳輸的數據進行編碼,并將時鐘信息嵌入到傳輸的數據中。接收器會從傳輸的比特流中分離出單獨的時鐘,用于對數據進行采樣和捕捉。在該系統中,accumulated jitter決定了bit到達與采樣之間的時間差,因此它是最重要的。如果整個系統的jitter太大,那就會導致采樣到錯誤的bit。

3. Jitter的隨機性與確定性

在測量jitter時,需要將多個周期一并考慮進來,從而從統計學的角度來了解整體的性能。對于RF、ADC/DAC和SerDes等系統,從統計數據中可以直接得到設計人員需要的重要信息。而對于數字系統,統計數據可以給出時鐘周期小于目標周期的概率,這是時序收斂的關鍵指標。

3.1 Random Jitter

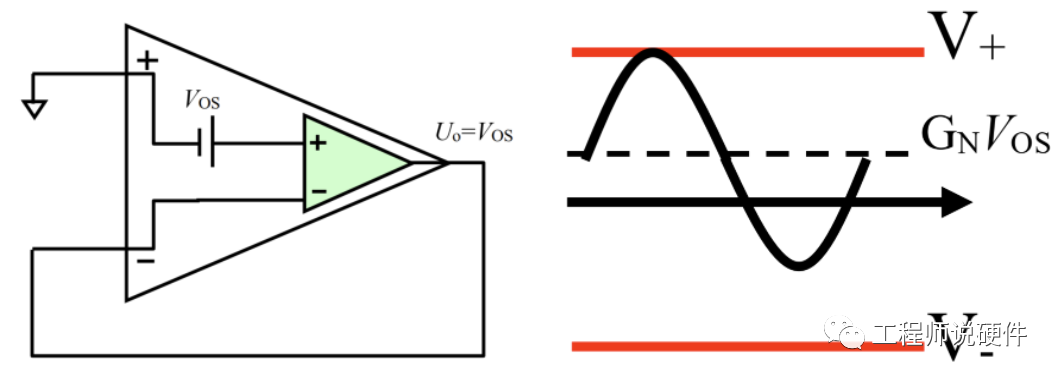

PLL內產生的jitter主要是帶寬有限的random jitter。此外,PLL電源的的白噪聲也會轉換為PLL輸出上的random jitter。

Random jitter來自真正的隨機行為,例如熱噪聲和閃爍噪聲。random jitter也可能由電源噪聲引起,該電源噪聲也來源于隨機行為,例如SoC電源,尤其是PLL電源中的熱噪聲。

Random jitter,顧名思義,在任何周期中都是無法預測的。只能預測一組時鐘的統計特性。其中,最常用于RJ測量的是正態分布的標準差,也叫RMS jitter。

Figure 1. Normal Distribution

Figure 1是jitter的正態分布,通常用于描述jitter的概率。PLL產生的random jitter都符合正態分布。

對于1-6倍標準差(σ),Figure 1標示了時鐘邊沿超出幾倍σ的概率。從圖中可以看出,隨著σ的倍數增大,概率很快地接近零,但是永遠不會到達零。例如,時鐘邊沿超過1倍σ的概率為31.7%,但超過6σ的概率為1.97x10-9,這個概率非常小,以至于在幾乎所有分析案例中,我們都可以將其近似為零。

需要注意的是,現代數字系統的設計通常要求非常嚴格,例如致信區間要處于5σ或6σ之間。串行通信標準通常具有更嚴格的標準,通常會指定更大倍數的來計算peak jitter。

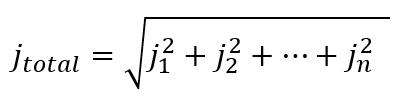

如果存在多個不相關的random jitter源,則需要以RMS的方式對它們進行匯總。因此得到組合后的:

其中:

jtotal是總的jitter

jk?for k=1…n是單獨的、不相關的jitter分量

3.2 Deterministic Jitter

Deterministic jitter是遵循已知模式的jitter。

在時鐘輸出中潛在的deterministic jitter源:

Spread Spectrum Clocking (SSC);

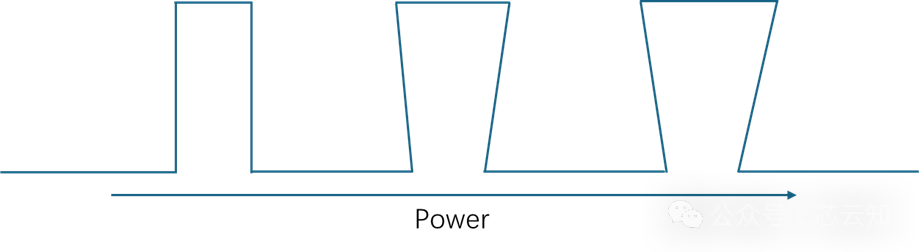

電源的確定性調制:如果SoC具有重復的高功率模式和低功率模式的切換,這可能會導致電源的確定性調整;

其他源的調制;

以確定性方式運行的任何其他機制。

Deterministic jitter的峰值可以直接測量。因為它是確定性的并且不依賴于出現的概率,所以測量的結果是絕對的。

例如,PLL的供電電壓可能會存在500kHz的紋波,這是由于電源開關切換引起的。該電源的噪聲分量將導致PLL輸出具有deterministic period jitter,并且該jitter的峰值與輸入電源的峰值波動成正比。在給定的時間內,電源電壓與PLL輸出時鐘瞬時period jitter存在直接關系。隨著電源電壓的變化,PLL輸出的周期變化將被視為deterministic jitter。

3.3 Random Jitter和Deterministic Jitter的組合

Random jitter和deterministic jitter只有峰值或者峰峰值可以組合在一起:

取給定σ的random jitter(Rj)

取deterministic jitter的峰值(Dj)

將兩個峰值相加得到total jitter(Tj=Rj+Dj)

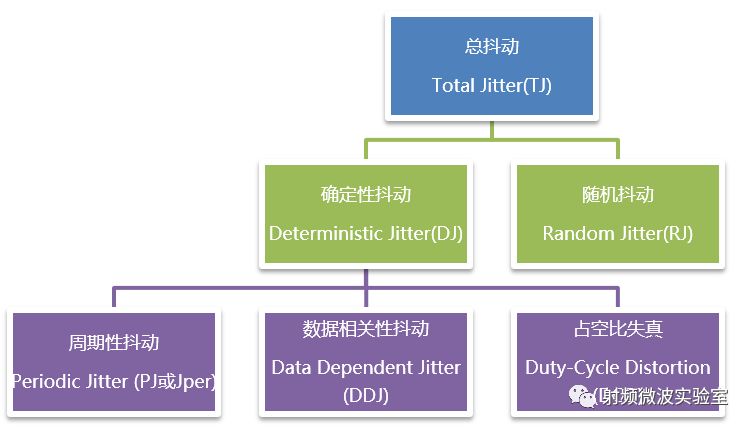

4 Jitter的定義與分類

4.1 Period Jitter

Period jitter是數字系統中最重要的jitter。它描述的是時鐘周期與該時鐘平均周期的偏差。

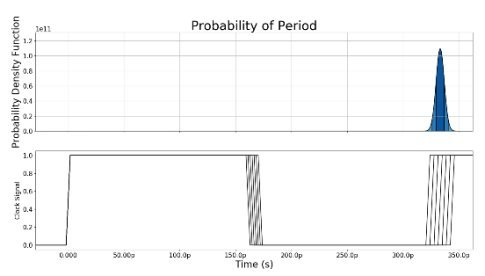

Figure 2. Period Jitter Example

Figure 2是3-GHz時鐘的period jitter示例。繪制在下軸上的每個時鐘周期與所有其他周期均不同。時鐘周期開始時所有的上升沿均已對其,從而顯示jitter帶來的周期差異。時鐘邊沿差異遵循正態分布,如上軸所示。

在數學上,period jitter可以表示為:

jperiod?= periodcurrent cycle-periodmean

其中:

jperiod是給定時鐘周期的瞬時period jitter

periodcurrent cycle是當前時鐘周期的瞬時周期

periodmean是被測量時鐘的平均周期

Period jitter包含random jitter和deterministic jitter兩個分量。這兩個分量可以單獨分析,但通常沒必要這么做,因為在大多數應用中,唯一重要的參數是可能出現的最短周期。

在數字系統中,可能出現的最短周期就是數字邏輯可用的時間。

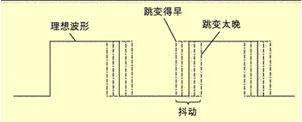

4.2 Cycle-to-Cycle Jitter

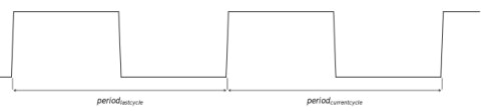

Cycle-to-cycle jitter表示兩個相鄰時鐘周期間的變化,如Figure 3所示。

Figure 3. Cycle-to-Cycle Jitter Definition

數學上,cycle-to-cycle jitter可以表示為:

jcc?= periodcurrent cycle-periodlast cycle

其中:

jcc?是給定時鐘周期的瞬時cycle-to-cycle jitter

periodcurrent cycle是當前時鐘周期的瞬時時鐘周期

periodlast cycle是上一個時鐘周期的瞬時時鐘周期

雖然不同的應用對不同的jitter要求不同,但是通常cycle-to-cycle jitter并不常用,因為它與數字、RF、ADC/DAC或Serdes系統中的任何常用性能指標無關。

4.3 Accumulated Jitter

Accumulated jitter,也叫long-term jitter,是指多個時鐘周期下給定時鐘沿與理想時鐘沿的偏差。這種偏差與period jitter不同,它是指在多個時鐘周期上累計值。

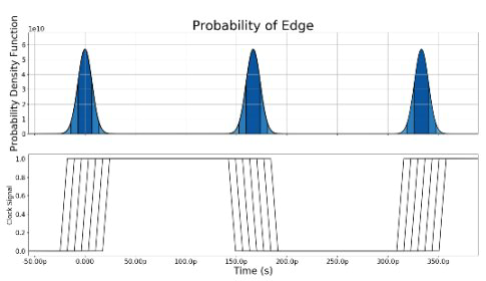

Figure 4. Accumulated Jitter Definition

Figure 4顯示了存在accumulated jitter的時鐘信號。Accumulated jitter是多個周期內period jitter的累積。在實際系統中,我們只需要考慮特定帶寬上的jitter,因此accumulated jitter會達到與時間無關的極限,不會變得無限大。

Accumulated jitter對于RF 系統、 ADCDAC、SerDes系統的時鐘非常重要。Accumulated jitter是隨機分量和確定性分量的總和。

電子發燒友App

電子發燒友App

評論