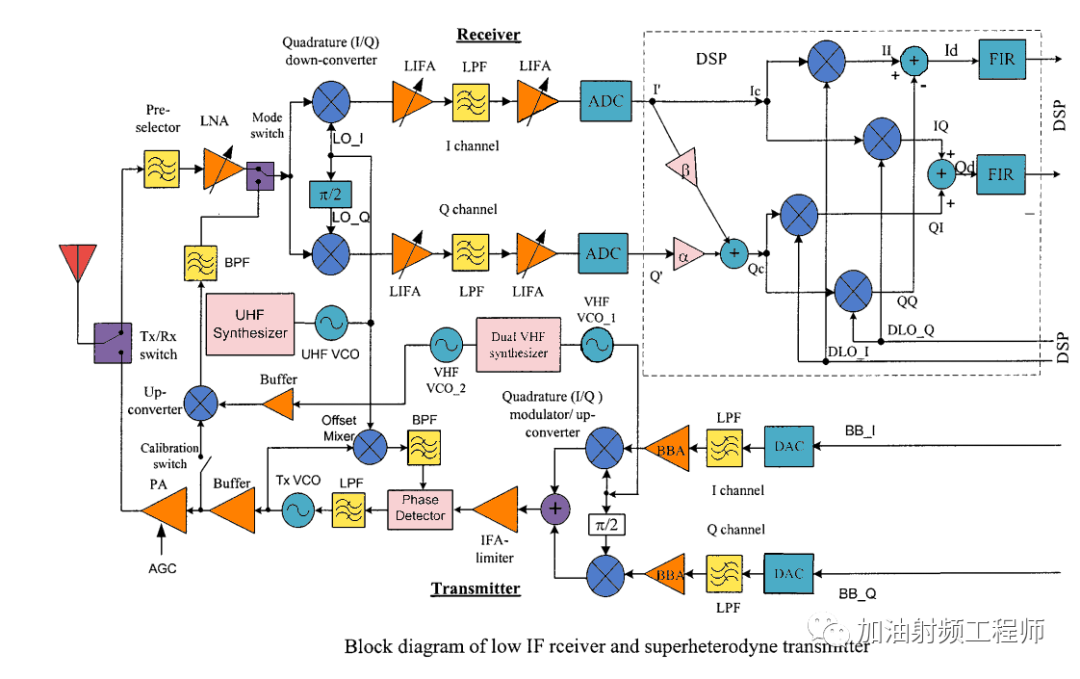

電路功能與優勢

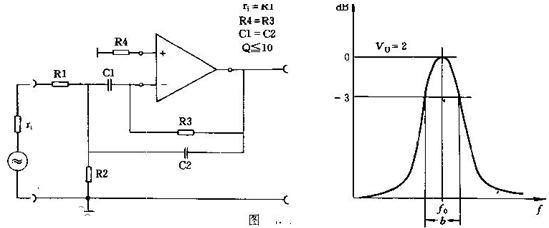

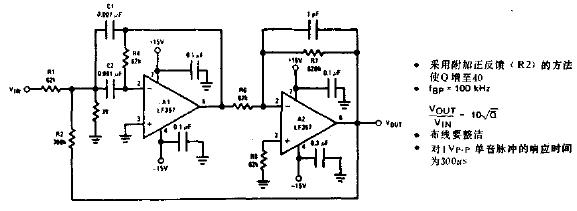

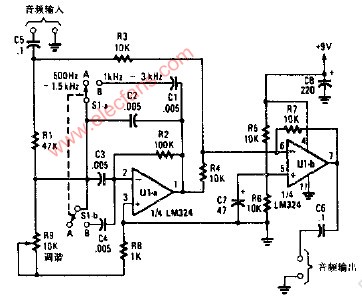

圖1中的電路是基于 ADL5565 超低噪聲差分放大器驅動器和 AD9642 14位、250 MSPS模數轉換器(ADC)的窄帶通接收機前端。

三階巴特沃茲抗混疊濾波器基于放大器和ADC的性能和接口要求而優化。濾波器網絡和其它組件引起的總插入損耗僅有5.8 dB。

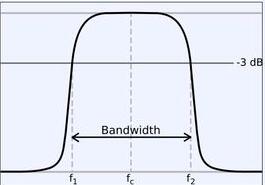

整體電路帶寬為18 MHz,通帶平坦度為3 dB。采用127MHz模擬輸入時,測量得到信噪比(SNR)和無雜散動態范圍(SFDR)分別為71.7dBFS和92 dBc。采樣頻率為205 MSPS,因此中頻輸入信號定位于102.5 MHz和205 MHz之間的第二奈奎斯特頻率區域。

電路描述

該電路接受單端輸入并使用寬帶寬(3 GHz) Mini-Circuits TC2-1T 1:2變壓器將其轉換為差分信號。6 GHz差分放大器 ADL5565 以6 dB的增益工作時,差分輸入阻抗為200Ω;以12 dB的增益工作時,差分輸入阻抗為100 Ω。它還提供15.5 dB的增益選項。

ADL5565是 AD9642的理想驅動器,通過帶通濾波器可在ADC中實現全差分架構,提供良好的高頻共模抑制,同時將二階失真產物降至最低。根據輸入連接的不同,ADL5565提供6dB或12dB的增益。本電路使用12dB的增益來補償濾波器網絡和變壓器的插入損耗(約5.8dB),總信號增益為5.5dB。

圖1. 14位、250 MSPS寬帶接收機前端(原理示意圖:未顯示所有連接和去耦)增益、損耗和信號電平在127 MHz輸入頻率下測得

1.5 dBm的輸入信號在ADC輸入端產生1.75 V p-p滿量程差分信號。

抗混疊濾波器是采用標準濾波器設計程序設計出的三階巴特沃茲濾波器。選擇巴特沃茲濾波器是因為它具有通帶平坦度。三階濾波器產生的交流噪聲帶寬噪聲比為1.05,可以借助多款免費濾波器程序進行設計,例如Nuhertz Technologies Filter Free或Quite Universal Circuit Simulator (Qucs) Free Simulation等。

為了實現最佳性能, ADL5565 應載入200 Ω的凈差分負載。15 Ω串聯電阻將濾波器電容與放大器輸出隔離開,100Ω電阻與下游阻抗并聯,當加入30 Ω串聯電阻時可產生217Ω的凈負載阻抗。

5Ω電阻與ADC輸入串聯,將內部開關瞬變與濾波器和放大器隔離開。

2.85kΩ輸入阻抗由可通過 AD9642 網頁上下載的電子表格確定。只需使用目標中頻頻率處于中心時的并聯跟蹤模式值。電子表格同時給出實值與虛值。

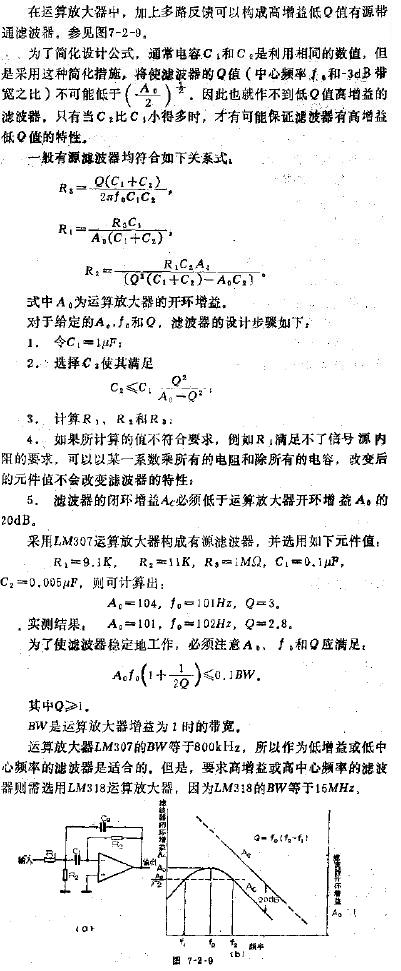

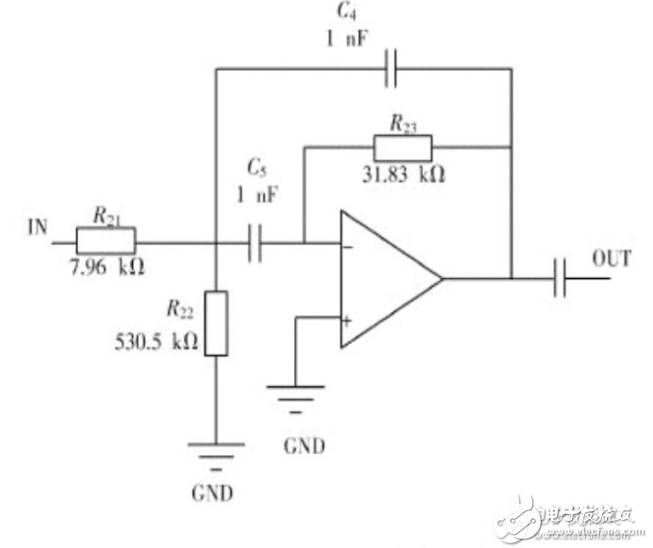

三階巴特沃茲濾波器采用源阻抗(差分)為200Ω、負載阻抗(差分)為200Ω、中心頻率為127MHz和20 MHz的3dB帶寬設計而成。標準濾波器設計程序計算出的值如圖1所示。由于需要較大的串聯電感,1.59 μH的電感被降為620nH,并且0.987pF的電容按比例提高到2.53 pF,因此保持127 MHz的諧振頻率不變,使元件值更真實。

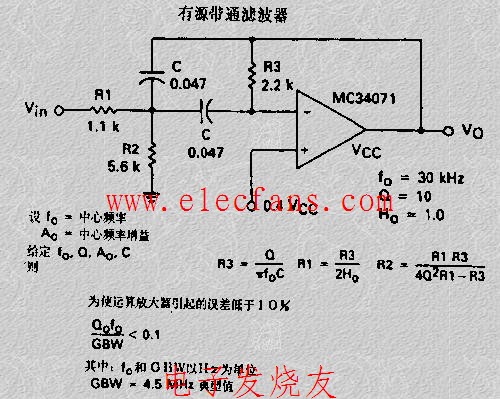

圖2. 開始三階差分巴特沃茲濾波器的設計,ZS = 200 Ω,ZL = 200 Ω,FC = 127 MHz,BW = 20 MHz

第二并聯電容的值減去ADC的2.5 pF內部電容,得到37.3 pF的值。該電路中,電容位于ADC附近,以減少/吸收電荷反沖。

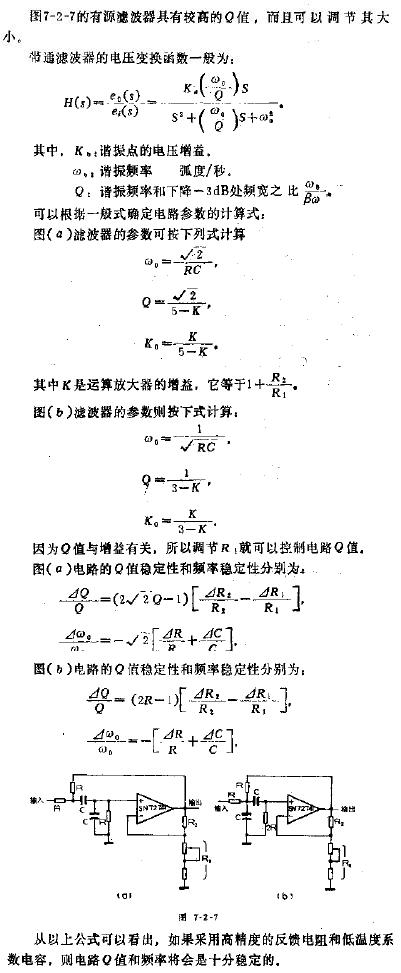

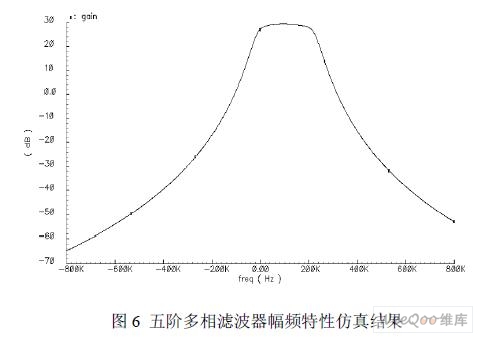

為最終濾波器無源元件選擇的值(經實際電路寄生效應調整后)顯示在圖1中。表1總結了系統的測量性能,其中3 dB帶寬為18 MHz,以127 MHz為中心。網絡的總插入損耗約為5.8 dB。圖3所示為頻率響應;圖4所示為SNR和SFDR性能。

表1. 電路的測定性能

圖3. 通帶平坦度性能與頻率的關系

圖4. SNR/SFDR性能與頻率的關系,采樣速率 = 205 MSPS

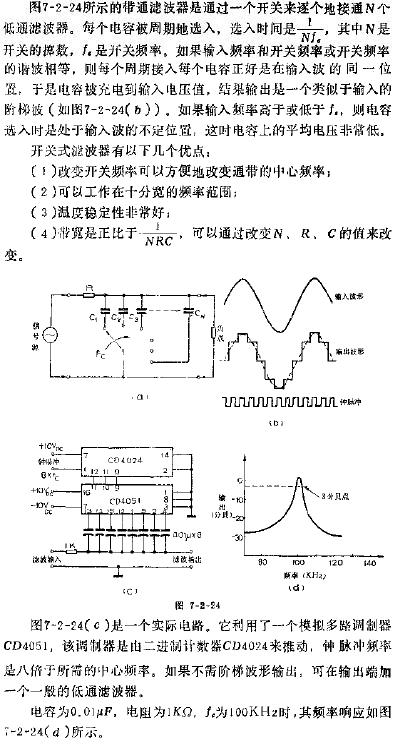

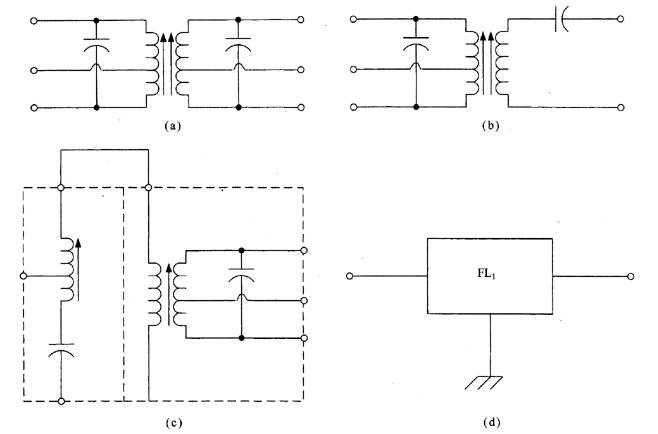

圖5. 采用帶通濾波器的一般差分放大器/ADC接口

濾波器和接口設計程序

本節介紹放大器/ADC與帶通濾波器接口設計的常用方法。為實現最佳性能(帶寬、SNR和SFDR),放大器和ADC應對一般電路形成一定設計限制。

1. 放大器必須參考數據手冊推薦的正確直流負載,以獲得最佳性能。

2. 放大器與濾波器的負載間必須使用正確數量的串聯電阻。這是為了防止通帶內的不良信號尖峰。

3. ADC的輸入必須通過外部并聯電阻降低,并使用正確串聯電阻將ADC與濾波器隔離開。此串聯電阻也會減少信號尖峰。

圖5所示的一般電路適用于大多數高速差分放大器/ADC接口,并作為帶通濾波器的基礎。此設計方法傾向于利用大多數高速ADC的相對較高輸入阻抗和驅動源(放大器)的相對較低阻抗,將濾波器的插入損耗降至最低。

基本設計流程如下:

1. 設置外部ADC端接電阻RTADC ,使得和 RADC的并聯組合介于200 Ω和400 Ω之間。

2. 根據經驗和/或ADC數據手冊建議選擇RKB ,通常介于5Ω和36Ω之間。

3. 使用下式計算濾波器負載阻抗

ZAAFL = 2RTADC ||(RADC + 2RKB)

4. 選擇放大器外部串聯電阻RRA。如果放大器差分輸出阻抗在100 Ω至200 Ω范圍內,RA 應小于10 Ω。如果放大器輸出阻抗為12 Ω或更低,RA應介于5 Ω和36 Ω之間。

5. 選擇 ZAAFL ,使放大器獲得的總負載ZAL最適合通過以下公式選擇的特定差分放大器:

ZAL = 2RA + ZAAFL

6. 使用下式計算濾波器源阻抗

ZAAFS = ZO + 2RA

7. 利用濾波器設計程序或表格,以及源阻抗ZAAFS 、負載阻抗 ZAAFL、濾波器類型、帶寬和階數,設計濾波器。實際使用的帶寬比應用的通帶所需帶寬高出10%,以確保頻率范圍內的平坦度。

經過上述初步計算,須了解電路的下列項目。

1. CAAF3 值必須至少為10 pF,比 CADC大數倍。這樣可將濾波器對CADC波動的敏感度降至最低。

2. ZAAFL與ZAAFS 之比不可高于約7,使濾波器在大多數濾波器表和設計程序的限值內。

3. CAAF1 值必須至少為5 pF,以盡可能降低對寄生電容和元件波動的敏感度。

4. 電感 LAAF必須為合理值,至少為數nH。

5. CAFF2 和 LAAF1 必須為合理值。有時電路仿真器會使這些值太低或太高。為使這些值更合理,只需保持同樣的諧振頻率并將這些值與更好的標準值元件相比。

在某些情況下,濾波器設計程序可提供一個以上獨特解決方案,特別是對于更高階濾波器。應始終選擇采用最合理元件值組合的解決方案。另外應選擇結束于分流電容的配置,以便分流電容與ADC輸入電容組合。

電路優化技術和權衡

本接口電路內的參數具有高互動性;因此優化電路的所有關鍵規格(帶寬、帶寬平坦度、SNR、SFDR和增益)幾乎不可能。不過,通過變更RA 和RKB,可以最大程度地減少通常發生于帶寬響應內的信號尖峰。

RA 值也會影響SNR性能。更大值在降低帶寬峰化的同時傾向略微提高SNR,因為驅動ADC滿量程需要更高信號電平。

選擇ADC輸入端的 RKB 串聯電阻以盡量減少任何殘余電荷注入(從ADC內部采樣電容)造成的失真。增加此電阻也傾向減少帶內的信號尖峰。

不過,增加 RKB 會增加信號衰減,因此放大器必須驅動更大信號才能填充ADC的輸入范圍。

為優化中心頻率,通帶特性、串聯電容、CAAF2可在小范圍內變動。

ADC的輸入端接電阻RTADC 通常選擇為使凈ADC輸入阻抗介于200 Ω和400 Ω之間,是大多數放大器的典型特性負載值。選擇的數值太高或太低都可能對放大器的線性度造成不利影響。

上述因素的權衡可能有些困難。本設計中,每個參數權重相等;因此所選值代表了所有設計特征的接口性能。某些設計中,根據系統要求,可能會選擇不同的值,以便優化SFDR、SNR或輸入驅動電平。

本設計的SFDR性能取決于兩個因素:放大器和ADC接口元件值,如圖1所示。

請注意,本設計中的信號與0.1 μF電容進行交流耦合,以阻擋放大器、其端接電阻和ADC輸入之間的共模電壓。有關共模電壓的更多信息,請參閱AD9642數據手冊。

無源組件和PCB寄生效應考慮

該電路或任何高速電路的性能都高度依賴于適當的印刷電路板(PCB)布局,包括但不限于電源旁路、受控阻抗線路(如需要)、元件布局、信號布線以及電源層和接地層。高速ADC和放大器PCB布局的詳情請參見指南 MT-031 和 MT-101 for。此外,請參考 CN-0227 和 CN-0238。

對于濾波器內的無源元件,使用低寄生表面貼裝電容、電感和電阻。所選電感來自Coilcraft 0603CS系列。濾波器使用的表貼電容為5%、C0G、0402型,以確保穩定性和精度。

常見變化

AD9643是AD9642的雙通道版本。

如需較低的功耗和帶寬,還可使用 ADA4950-1和/或 ADL5561/ ADL5562 。這些元件與之前列舉的單通道元件引腳兼容。

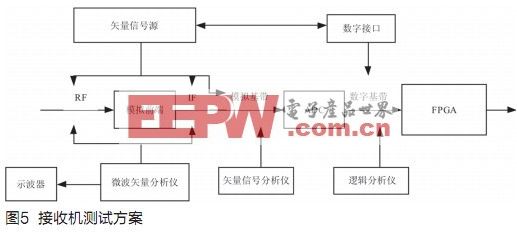

電路評估與測試

本電路使用修改的AD9642-250EBZ電路板和基于HSC-ADC-EVALCZ FPGA的數據采集板。這兩片板具有對接高速連接器,可以快速完成設置并評估電路性能。修改的AD9642-250EBZ板包括本筆記所述的評估電路,HSC-ADC-EVALCZ數據采集板與VisualAnalog?評估軟件一起使用,此外還使用SPI控制器軟件來適當控制ADC并采集數據。AD9642-250EBZ板的原理圖、BOM和布局請參見User Guide UG-386。CN-0279設計支持包中的readme.txt說明了對標準AD9642-250EBZ板做出的修改。應用筆記AN-835詳細說明了如何設置硬件和軟件,以運行本電路筆記所述的測試。

電子發燒友App

電子發燒友App

評論