簡介

本系列文章的前幾部分介紹了Zynq SDR快速原型開發(fā)平臺1,說明了利用MATLAB和Simulink開發(fā)算法以成功處理和解碼ADS-B傳輸?shù)牟襟E2,并展示了如何在仿真中和利用SDR平臺獲得的實時數(shù)據(jù)驗證該算法3。所有階段的最終目標是創(chuàng)建一個經(jīng)驗證的模型,其可以轉(zhuǎn)換為C和HDL代碼,并且能夠方便地集成到SDR平臺的軟件和硬件基礎(chǔ)設(shè)施中。

T本系列第二部分("利用MATLAB和Simulink進行S模式檢測和解碼")2討論的Simulink模型是一個具有足夠高精度硬件細節(jié)的仿真模型,可驗證該設(shè)計將能成功解碼ADS-B消息。以該模型為出發(fā)點,本部分將討論為了產(chǎn)生一個能夠在Zynq SDR快速原型開發(fā)平臺上運行的有效接收機設(shè)計所需的最后步驟。像前面幾篇文章一樣,開發(fā)該有效設(shè)計所需的技能包括: 熟練使用MATLAB和Simulink,了解Zynq無線電硬件,以及軟硬件集成技能。

?

本文提出的步驟包括:

以Zynq SoC上的FPGA結(jié)構(gòu)和ARM? 處理系統(tǒng)為目標,將Simulink模型劃分為多個功能。

引入對Simulink模型的設(shè)計變更,以改善所生成的HDL代碼的性能。

生成ADS-B接收機算法的HDL和C語言源代碼。

將生成的源代碼集成到Zynq無線電平臺設(shè)計中。

此過程結(jié)束時,就會產(chǎn)生一個經(jīng)全面驗證的SDR系統(tǒng),其運行從Simulink ADS-B模型自動生成的C和HDL代碼,可實時接收和解碼商用航空器信號。

將模型劃分為硬件和軟件組件

生成實現(xiàn)代碼過程的第一步是劃分設(shè)計功能,以便在Zynq SoC的可編程邏輯和ARM處理系統(tǒng)上運行。

功能劃分通常是從明確設(shè)計的不同組件的處理要求和所需的執(zhí)行速率與時間開始。需要以采樣速率實時運行的計算密集型組件(如數(shù)據(jù)調(diào)制/解調(diào)算法),最適合在可編程邏輯中實現(xiàn)。計算量相對較少的處理任務(wù)(如數(shù)據(jù)解碼和渲染,以及系統(tǒng)監(jiān)視和診斷),更適合通過軟件實現(xiàn)。其它需要考慮的方面有: 運算的數(shù)據(jù)類型和復雜度,以及輸入和輸出數(shù)據(jù)的精度。所有以可編程邏輯為目標的運算都采用定點、整數(shù)或布爾數(shù)據(jù)類型。對于更復雜的運算,如三角函數(shù)和平方根,須在可用硬件資源的約束下,利用近似來高效實現(xiàn)。所有這些約束都會導致精度損失,若不加以適當評估和處理,可能會對系統(tǒng)功能帶來不利影響。但是,以處理系統(tǒng)為目標的組件可以采用浮點數(shù),并以最高保真度實現(xiàn)任何復雜度的運算,不過通常要以降低執(zhí)行速度為代價。

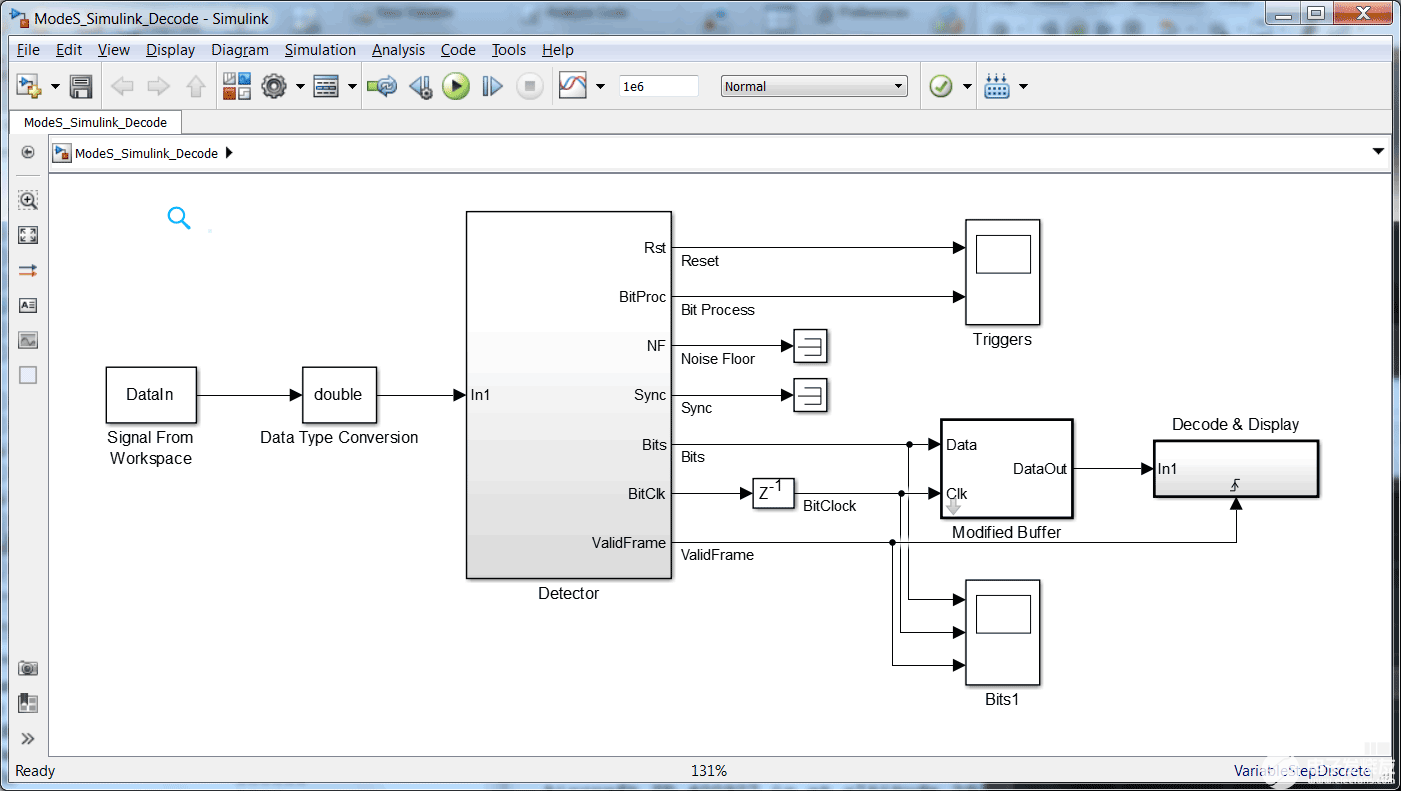

以上述約束作為指導原則,ADS-B解碼算法的劃分是相當明顯的。ModeS_Simulink_Decode.slx模型中的檢波器模塊的功能,包括I/Q樣本的前端處理一直到校驗和計算,非常適合在Zynq SoC的可編程邏輯上實現(xiàn)(圖1)。 改良緩沖器和解碼與顯示模塊中的消息位解碼功能,很容易在處理系統(tǒng)中實現(xiàn)。

圖1. ModeS_Simulink_Decode.slx: FPGA和ARM處理器劃分

對下述內(nèi)容和Simulink模型感興趣的讀者,可在Analog Devices GitHub庫4中找到相關(guān)文件。4

從Simulink模型生成HDL代碼

S模式解碼器模型中的檢波器模塊(圖2)包括多個子系統(tǒng): CalcSyncCorr、CalcNF、SyncAndControl、BitProcess、CalcCRC和FameDetect。MathWorks的HDL編碼器5用于產(chǎn)生此設(shè)計的HDL源代碼。

圖2. 用于HDL代碼生成的檢波器模塊

為了利用HDL編碼器成功生成HDL代碼,Simulink模型必須滿足一些條件。下面是其中幾個最重要的要求:

使用支持HDL代碼生成的模塊。HDL編碼器支持大約200個Simulink模塊的代碼生成6。在檢波器設(shè)計中,所有模塊都支持HDL代碼生成,包括狀態(tài)流程圖和數(shù)字濾波器模塊。

使用定點數(shù)據(jù)類型。在檢波器設(shè)計中,信號使用12位、24位和布爾數(shù)據(jù)類型。12位數(shù)據(jù)類型與ADI公司AD9361收發(fā)器上的模數(shù)轉(zhuǎn)換器的位寬一致。

使用標量或矢量信號。矢量信號可用于多通道信號或資源共享。

避免模型中出現(xiàn)代數(shù)環(huán)。HDL編碼器軟件不支持存在代數(shù)環(huán)條件的模型的HDL代碼生成。

檢波器模塊,最終用C語言實現(xiàn)。由此得到的模型ModeS_ADI_CodeGen.slx用于生成HDL代碼。與手動編碼過程相比,它只需幾分鐘便能生成數(shù)千行HDL代碼。HDL編碼器產(chǎn)生的源代碼是Simulink模型的位真、周期精確版本。這是使用模型進行設(shè)計在生產(chǎn)力提升方面帶來的重大好處之一,所生成的代碼是Simulink模型的精確轉(zhuǎn)譯。

此外,這些代碼易讀且可追溯,工程師可以輕松地將生成的代碼映射到設(shè)計模型。這是通過多種方法來實現(xiàn)的(圖3):

生成的HDL代碼文件中保留了該模型的層次。本例中,頂層模塊被命名為Detector.vhd,處在下一級的子系統(tǒng)被命名為CalcNF.vhd、Bit_Process.vhd等。

T生成的代碼中保留了該模型所用的模塊名稱、端口名稱、信號名稱、數(shù)據(jù)類型和復雜度。

模型與源代碼之間存在關(guān)聯(lián),設(shè)計人員點擊Simulink模型中的某個模塊,便可自動導航到相應的HDL代碼。同樣,生成的代碼中也有超級鏈接,點擊它便會打開Simulink模型,并高亮顯示與該代碼段相關(guān)的模塊。

圖3. ModeS_ADI_CodeGen.slx的HDL源代碼

優(yōu)化ADS-B模型以產(chǎn)生具有更高時鐘速度的HDL代碼

雖然ModeS_ADI_CodeGen.slx模型成功生成了HDL代碼,但在絕大多數(shù)情況下,設(shè)計人員會希望改善初始結(jié)果。設(shè)計人員通常要滿足速度和面積約束條件,這就需要優(yōu)化初始Simulink模型以實現(xiàn)所需的效果。Simulink和代碼生成的一個重要優(yōu)勢是,設(shè)計人員可以在模型中進行優(yōu)化,并運行仿真以確保變更沒有破壞算法,然后重新生成HDL代碼。這種方法比修改HDL源代碼(可能會破壞算法)更為簡單,而且不易出錯。

對于本設(shè)計,模型生成的HDL代碼很容易適應可用的FPGA結(jié)構(gòu),但運行的時鐘速率相對較低。這在許多初步設(shè)計中是常見現(xiàn)象。HDL編碼器內(nèi)置的分析工具表明,模型中的關(guān)鍵路徑從I/Q樣本輸入延伸到CalcCRC子系統(tǒng)中的第一個寄存器。在設(shè)計中插入流水線寄存器是提高時鐘速度的一種常見方法(圖4)。 流水線縮短了信號操作之間的路徑,代價是增加了整體處理的延遲。這種折中通常是可以接受的,因為相對于更高的時鐘速度,延遲略微增加是很小的代價。

圖4. 檢波器設(shè)計中插入流水線寄存器

位于子系統(tǒng)之間的流水線寄存器有助于改善設(shè)計的時鐘速率,但如果數(shù)字濾波器模塊選擇優(yōu)越的架構(gòu),則可以實現(xiàn)更好的時鐘速率。許多Simulink模塊都有架構(gòu)選擇,設(shè)計人員可以藉此優(yōu)化設(shè)計的速度或面積。對于計算噪底和前同步碼相關(guān)性所用的數(shù)字濾波器(圖5),輸出乘法器的流水線化可以縮短數(shù)字濾波器內(nèi)的關(guān)鍵路徑,提高設(shè)計時鐘速率。

圖5. 數(shù)字濾波器模塊的HDL模塊選擇

采取這兩個簡單的流水線變更之后,生成的HDL代碼的時鐘速率便超過140 MHz。這對于使用代碼生成工具的工程設(shè)計是一個有用的啟示: 在代碼生成模型上應用一點硬件設(shè)計原理知識,便可對生成的代碼結(jié)果產(chǎn)生相當大的影響。對該設(shè)計還可以做進一步的優(yōu)化,但并無必要,因為HDL代碼很容易滿足該設(shè)計相對簡單的時序和資源目標。

在傳統(tǒng)無線電設(shè)計過程中,大量開發(fā)時間花在HDL代碼的測試和調(diào)試上。而在基于模型的設(shè)計方法中,更多時間是花在開發(fā)仿真和代碼生成模型上,本例就是如此。然而,開發(fā)時間會節(jié)省很多,因為生成的源代碼與經(jīng)驗證的仿真行為完全一致,只需對嵌入式硬件執(zhí)行極少量的調(diào)試。

利用MATLAB編碼器7生成C語言代碼

與生成HDL代碼相似,為了生成用于本設(shè)計解碼功能的C語言代碼,也有幾個條件必須滿足。下面是兩個最重要的要求:

使用MATLAB編碼器支持的函數(shù)。MATLAB編碼器支持大部分MATLAB語言和眾多工具箱8,但您可能無意中使用了代碼生成所不支持的函數(shù)。MATLAB編碼器提供了"代碼就緒工具"9等工具來幫助找出不支持的函數(shù)。

一旦聲明一個MATLAB變量,其大小和類型便不得改變。這是為了確保在生成的代碼中正確分配存儲器。

從MATLAB生成C代碼的最簡單方法是從MATLAB工具列上的Apps選項卡新建一個MATLAB編碼器項目。MATLAB編碼器項目的最終輸出如圖6所示。

圖6. 針對的DecodeBits_ADI.m的MATLAB編碼器項目

在該項目中,頂層MATLAB函數(shù)是DecodeBits_ADI.m。用戶需要指定此函數(shù)所需的數(shù)據(jù)類型和大小作為輸入參數(shù)。 圖6顯示,此函數(shù)的輸入?yún)?shù)為112個布爾數(shù)據(jù)位和2個雙精度值(用以提供用戶當前的經(jīng)度和緯度)。DecodeBits_ADI.m的輸出大小和數(shù)據(jù)類型(例如:*nV表示向北速度,*eV表示向東速度,*alt表示高度)由MATLAB編碼器自動確定。MATLAB編碼器會找出頂層入口文件DecodeBits_ADI.m調(diào)用的所有其他函數(shù),包括AltVelCalc_ADI.m和LatLongCalc_ADI.m,然后生成整個解碼算法的C語言源代碼。

MATLAB編碼器生成的C語言代碼是MATLAB功能的直接轉(zhuǎn)譯。如同HDL代碼生成,MATLAB編碼器產(chǎn)生的源代碼也是易讀且可追溯的,工程師可以輕松發(fā)現(xiàn)原始MATLAB代碼與生成的C代碼之間的關(guān)系。本例的C代碼可從MATLAB命令提示產(chǎn)生,并且可由任何ANSI C編譯器編譯。

HDL代碼平臺部署

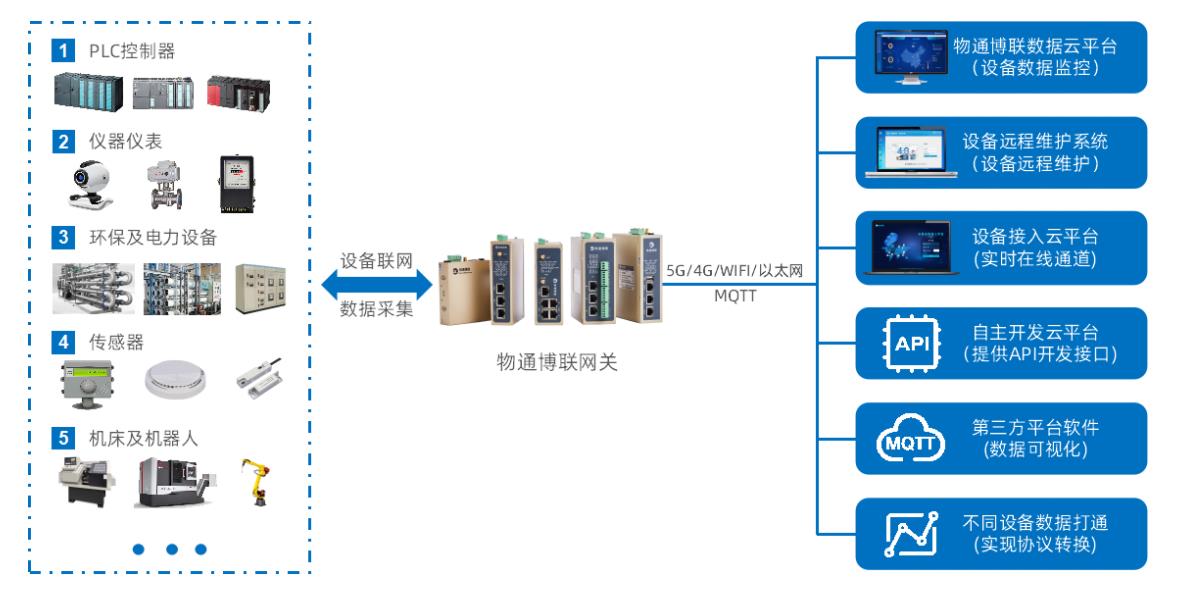

完成上述步驟(將設(shè)計劃分為不同功能以在Zynq的可編程邏輯和處理系統(tǒng)上運行,針對HDL和C語言代碼生成優(yōu)化設(shè)計,以及通過仿真驗證優(yōu)化后的設(shè)計能夠有效工作且滿足性能標準)之后,現(xiàn)在便需要將設(shè)計部署到實際SDR硬件平臺上,并驗證系統(tǒng)在實際條件下的功能為此,我們使用ADI公司的AD-FMCOMMS3-EBZ SDR平臺10,其連接到一個運行ADI Linux發(fā)行版的Xilinx ZC706板11。

AD-FMCOMMS3-EBZ板附帶一個ADI公司提供的開源Vivado HDL參考設(shè)計12。該參考設(shè)計包含用以配置AD-FMCOMMS3-EBZ板上的AD9361收發(fā)器及傳輸數(shù)據(jù)所需的全部IP模塊。圖7為該HDL參考設(shè)計的框圖。

圖7. HDL參考設(shè)計框圖

AD9361 IP內(nèi)核實現(xiàn)了AD9361收發(fā)器芯片與Zynq器件之間的LVDS接收和發(fā)送數(shù)據(jù)接口,以及與設(shè)計其余部分的數(shù)據(jù)接口。DMA模塊用于AD9361 IP與DDR存儲器之間的高速數(shù)據(jù)傳輸。 AD9361 IP模塊的數(shù)據(jù)接口包括4條用于接收的數(shù)據(jù)線和4條用于發(fā)送的數(shù)據(jù)線,對應于AD9361的兩個接收通道和兩個發(fā)送通道的I&Q數(shù)據(jù)。每條數(shù)據(jù)線都是16位寬。為使系統(tǒng)內(nèi)部的數(shù)據(jù)傳輸效率更高,接收和發(fā)送數(shù)據(jù)被包裝到由DMA模塊管理的64位寬總線中。AD9361 IP的16位并行數(shù)據(jù)線通過打包和解包模塊連接到DMA。

為了將ADS-B模型的HDL代碼部署到SDR平臺的現(xiàn)有HDL基礎(chǔ)設(shè)施中,需要創(chuàng)建一個可插入數(shù)據(jù)路徑中的IP內(nèi)核,從而實時處理收到的數(shù)據(jù)并將處理過的數(shù)據(jù)傳送到軟件層。部署過程是一個困難且耗時的任務(wù),因為它要求對HDL設(shè)計的功能有深刻的理解,同時需要嫻熟的HDL編程技能。為了簡化這些步,MathWorks在HDL編碼器中集成了一個稱為HDL Workflow Advisor的實用工具,ADI公司為AD-FMCOMMS2-EBZ/AD-FMCOMMS3-EBZ SDR平臺和Xilinx ZC706板提供了一個板支持包(BSP) 13。

HDL Workflow Advisor可引導用戶一步一步地從Simulink模型生成HDL代碼。用戶可以選擇不同的目標工作流程,包括"ASIC/FPGA"、"FPGA在環(huán)"和"IP內(nèi)核生成"。目標平臺選擇包括Xilinx評估板、Altera評估板和FMCOMMS2/3 ZC706 SDR平臺。余下的代碼生成和目標集成過程可由HDL Workflow Advisor自動完成。

ADI公司提供的BSP是板定義和參考設(shè)計14的集合,用以為HDL Workflow Advisor提供必要的信息和工具來產(chǎn)生與現(xiàn)有HDL參考設(shè)計兼容的IP模塊,以及將生成的IP插入HDL參考設(shè)計。 圖8顯示了如何配置Workflow Advisor來產(chǎn)生ADS-B模型的IP內(nèi)核。請注意:必須選擇IP內(nèi)核生成工作流程,并以ADI公司的AD-FMCOMMS3-EBZ SDR平臺和Xilinx ZC706板為目標。

圖8. Workflow Advisor配置

下一步是配置IP與參考設(shè)計之間的接口。 在輸入側(cè),該模型接受原始I&Q樣本,模型的輸入端口與AD9361接收器數(shù)據(jù)端口直接相連。在模型的所有輸出信號中,當前階段感興趣的是數(shù)據(jù)、frame_valid和bit_clk信號。數(shù)據(jù)和frame_valid為16位寬,由bit_clk信號提供時鐘。這些信號可以連接到BSP的"DUT Data x Out"接口,意味著它們將接收對DMA模塊的直接訪問;然后可以將數(shù)據(jù)傳輸?shù)紻DR供軟件層訪問。bit_clk信號連接到BSP的"DUT Data Valid Out"接口,用以控制DMA采樣速率。圖9顯示了HDL接口必須如何配置。

圖9. HDL接口配置

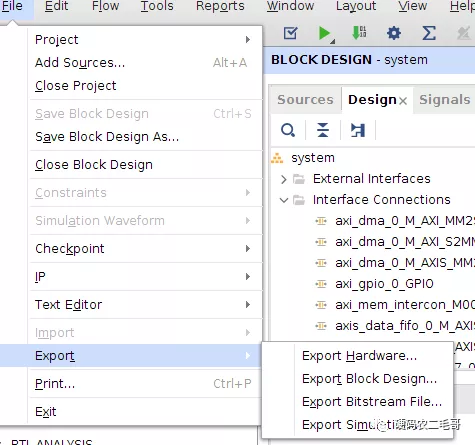

一旦定義了目標接口,HDL Workflow Advisor的第2步和第3步便可保持默認狀態(tài),然后通過運行步驟4.1(創(chuàng)建項目)來啟動項目生成過程。此步驟的結(jié)果是產(chǎn)生一個Vivado項目,其ADS-B IP內(nèi)核已集成到ADI公司的HDL參考設(shè)計中。圖10顯示了ADS-B IP內(nèi)核與設(shè)計中其余模塊的連接。

圖10. HDL參考設(shè)計中的ADS-B IP連接

從Vivado項目生成位流便可結(jié)束HDL集成過程,但最終目標是讓Linux在系統(tǒng)上運行。 為此,在生成位流之后,可按照標準Xilinx SDK第一階段引導加載程序(fsbl)和Linux引導文件創(chuàng)建過程創(chuàng)建一個Linux引導文件。與新創(chuàng)建HDL設(shè)計對應的Linux設(shè)備樹和映像文件隨同AD-FMCOMMS3-EBZ BSP發(fā)布。所有文件都必須與SD卡引導分區(qū)上的Linux引導文件一同復制;引導分區(qū)用于存儲在Xilinx ZC706板上運行ADI公司Linux發(fā)行版所需的全部文件。

C語言代碼平臺部署

將ADS-B HDL IP集成到SDR平臺的HDL設(shè)計并創(chuàng)建Linux SD卡之后,便需要實現(xiàn)用來解碼ADS-B數(shù)據(jù)的軟件應用程序。此應用程序基于第5部分生成的C代碼,執(zhí)行如下任務(wù):

配置AD9361以接收ADS-B信號。

從ADS-B IP內(nèi)核讀取數(shù)據(jù)。

在讀取的數(shù)據(jù)中檢測有效ADS-B幀。

解碼并顯示ADS-B信息。

實現(xiàn)任務(wù)1和任務(wù)2的最簡單方法是使用libiio庫15提供的功能。此庫提供了接口函數(shù),允許用戶輕松配置AD9361以及接收和發(fā)送數(shù)據(jù)。 配置過程設(shè)置如下系統(tǒng)參數(shù):

LO頻率—1.09 GHz

采樣速率—12.5 MHz

模擬帶寬—4.0 MHz

AGC—快速啟動模式

除上述參數(shù)外,一個數(shù)據(jù)速率為12.5 MSPS、通帶頻率為3.25 MHz、阻帶頻率為4 MHz的數(shù)字FIR濾波器也被加載到AD9361中,確保收到的數(shù)據(jù)僅包含目標頻段。該FIR濾波器的系統(tǒng)參數(shù)和設(shè)計方法詳見本系列文章第三部分3所述。

ADS-B IP的輸出數(shù)據(jù)通過DMA模塊傳輸?shù)较到y(tǒng)的DDR存儲器。libiio庫提供如下功能: 將從ADS-B IP獲取的數(shù)據(jù)放置到指定大小的存儲緩沖器中;等待緩沖器填滿;通過指針訪問該緩沖器。 一旦緩沖器填滿,ADS-B解碼算法便可處理數(shù)據(jù)。ADS-B IP內(nèi)核有兩個輸出通道:一個通道對應于ADS-B位流,另一個通道指示一個有效數(shù)據(jù)幀在位流中的何處結(jié)束。兩個通道均包含相同的數(shù)據(jù)速率,彼此同步。 有效通道中一個等于1的樣本表示數(shù)據(jù)通道中一個有效幀的最后一位。 通過解析這兩個通道,軟件可以從位流中提取有效的ADS-B數(shù)據(jù)幀,并將數(shù)據(jù)傳送到MATLAB編碼器生成的解碼函數(shù)。當計算航空器坐標時,解碼函數(shù)利用ADS-B數(shù)據(jù)幀和當前位置的經(jīng)緯度作為輸入。當前經(jīng)緯度被指定為應用程序的參數(shù)。ADS-B解碼數(shù)據(jù)的顯示與Simulink模型相似。

ADS-B數(shù)據(jù)解碼程序是在Linux下利用makefile構(gòu)建。該應用程序的源代碼和makefile可在Analog Devices github庫中下載16。

這樣就完成了利用HDL編碼器從ADS-B模型生成的HDL代碼和利用MathWorks MATLAB編碼器生成的C代碼的平臺部署步驟。下一步是驗證系統(tǒng)功能并評估結(jié)果。

系統(tǒng)驗證

為了驗證系統(tǒng)功能,首先要在AD-FMCOMMS3-EBZ板的一個接收端口與一個發(fā)送端口之間建立一個回送連接,并發(fā)送仿真期間使用的相同ADS-B信號。通過接收和解碼此數(shù)據(jù),可以驗證SDR平臺上運行的算法輸出是否與仿真結(jié)果一致。圖11顯示了ADS-B數(shù)據(jù)解碼程序的輸出,結(jié)果與本系列文章第三部分中利用預先捕捉的數(shù)據(jù)進行HDL仿真所獲得的結(jié)果完全相同。 這說明系統(tǒng)運行符合預期,可以利用實際數(shù)據(jù)進行測試。

圖11. 回送結(jié)果

現(xiàn)場實際測試時,SDR接收機放在MathWorks位于美國馬薩諸塞州納蒂克的總部外面,系統(tǒng)解碼的ADS-B信息與飛機實時跟蹤網(wǎng)站(如flightradar24.com)提供的數(shù)據(jù)進行對比。結(jié)果證實:在天線的視線范圍內(nèi),系統(tǒng)能夠解碼從飛機收到的數(shù)據(jù)。圖12顯示了系統(tǒng)檢測到的航空器信息與在線飛機跟蹤數(shù)據(jù)的對比情況。可以看到,解碼算法給出了正確的航空器ID、高度、速度和經(jīng)緯度坐標。

圖12. 實時數(shù)據(jù)結(jié)果

結(jié)論

本系列文章展示了如何利用基于模型的設(shè)計來實現(xiàn)SDR平臺從仿真到生產(chǎn)的全過程,這是其中的最后一篇。本系列說明了開發(fā)一個"硬件準備就緒"的ADS-B Simulink模型的所有階段。 我們設(shè)計了一個仿真模型來證明我們能夠解碼記錄到的ADS-B消息,然后利用從SDR硬件平臺獲取的實時數(shù)據(jù)驗證該模型。這不僅驗證了該模型,而且驗證了SDR平臺的模擬前端和數(shù)字接收機信號鏈的設(shè)置。同時,它令我們確信該平臺已調(diào)整好,可用于接收ADS-B信號。然后,我們將該模型劃分為不同的功能,以便在Zynq處理系統(tǒng)和可編程邏輯上運行,并優(yōu)化了該模型以自動生成C和HDL代碼。最后,我們將C和HDL代碼集成到SDR設(shè)計中,并利用實時商業(yè)空中交通數(shù)據(jù)驗證了系統(tǒng)的功能。最終成果是一個設(shè)計流程——使用MathWorks建模和代碼生成工具,并結(jié)合Zynq SDR平臺來創(chuàng)建全面有效的SDR系統(tǒng)。

示例系統(tǒng)說明:相比于傳統(tǒng)設(shè)計方法,基于模型的設(shè)計工作流程與ADI公司的集成RF捷變收發(fā)器可編程無線電硬件AD9361/AD9364 相結(jié)合,可以幫助設(shè)計團隊更快開發(fā)出有效的無線電原型,成本也更低。文中的原型是由筆者在相對較短的時間內(nèi)制作出來的,遇到的障礙極少,使用了如下資源:

在MATLAB和Simulink中能夠創(chuàng)建ADS-B接收機模型,并生成可用的C和HDL源代碼。

HDL Workflow Advisor中的功能,它們使很多軟硬件集成步驟自動完成。

libiio等庫,幫助完成其余集成步驟以便部署SDR原型。

MathWorks和ADI公司提供的產(chǎn)品幫助和技術(shù)支持。

ADS-B是一個相對簡單的標準,為通過這種方法構(gòu)建SDR原型提供了一個很好的測試案例。采用基于模型的設(shè)計和Zynq SDR平臺的工程師應當能夠按照本系列文章所提出的工作流程,開發(fā)出更復雜、更強大的QPSK、QAM和LTE SDR系統(tǒng)。

參考文獻?

1Di Pu, Andrei Cozma, 和 Tom Hill. "快速通往量產(chǎn)的四個步驟:利用基于模型的設(shè)計開發(fā)軟件無線電,第一部分——ADI/Xilinx SDR快速原型開發(fā)平臺及其能力、優(yōu)勢和工具",模擬對話第49卷第3期。

2Mike Donovan, Andrei Cozma, 和 Di Pu. "快速通往量產(chǎn)的四個步驟:利用基于模型的設(shè)計開發(fā)軟件無線電,第二部分——利用MATLAB和Simulink進行S模式檢測和解碼",模擬對話第49卷第4期。

3Di Pu, Andrei Cozma. "快速通往量產(chǎn)的四個步驟:利用基于模型的設(shè)計開發(fā)軟件無線電,第三部分——利用硬件在環(huán)驗證S模式信號解碼算法",模擬對話第49卷第4期。

4Analog Devices GitHub庫。

5HDL編碼器。

6HDL編碼器模塊支持。

7MATLAB編碼器。

8MATLAB工具箱。

9MATLAB代碼生成就緒工具。

10AD-FMCOMMS3-EBZ用戶指南。

11Xilinx Zynq-7000 All Programmable SoC ZC706評估套件。

12AD-FMCOMMS2-EBZ/AD-FMCOMMS3-EBZ/AD-FMCOMMS4-EBZ HDL/AD-FMCOMMS5-EBZ HDL參考設(shè)計。

13Analog Devices BSP for MathWorks HDL Workflow Advisor。

14電路板和參考設(shè)計注冊系統(tǒng)。

15什么是Libiio?

16MathWorks目標模型—ADSB。

作者

Mike Donovan是MathWorks公司應用工程部門經(jīng)理。他擁有巴克內(nèi)爾大學電氣工程學士學位和康涅狄克大學電氣工程碩士學位。加入MathWorks之前,Mike開發(fā)過雷達和衛(wèi)星通信系統(tǒng),并在寬帶電信行業(yè)工作過。

Andrei Cozma? 是ADI公司工程設(shè)計經(jīng)理,負責支持系統(tǒng)級參考設(shè)計的設(shè)計與開發(fā)。 他擁有工業(yè)自動化與信息技術(shù)學士學位及電子與電信博士學位。他參與過電機控制、工業(yè)自動化、軟件定義無線電和電信等不同行業(yè)領(lǐng)域的項目設(shè)計與開發(fā)。

Di Pu是ADI公司系統(tǒng)建模應用工程師,負責支持軟件定義無線電平臺和系統(tǒng)的設(shè)計與開發(fā)。她與MathWorks密切合作解決雙方共同客戶的難題。加入ADI公司之前,她于2007年獲得南京理工大學(NJUST)電氣工程學士學位,于2009年和2013年分別獲得伍斯特理工學院(WPI)電氣工程碩士學位和博士學位。她是WPI 2013年博士論文Sigma Xi研究獎獲得者。

電子發(fā)燒友App

電子發(fā)燒友App

評論